经典FPGA源码分享

在FPGA学习过程中,乘法器、除法器、二进制转BCD码等基础模块的设计是核心重点,但多数设计仅完成仿真验证,缺乏实际硬件上板测试,难以确保模块功能的实用性。本文以8位十进制计算器为载体,整合多种自研功能模块,完成硬件上板验证,全程未调用任何厂商IP核,实现了设计的高通用性与资源高效利用。(文末附源码下载链接)。

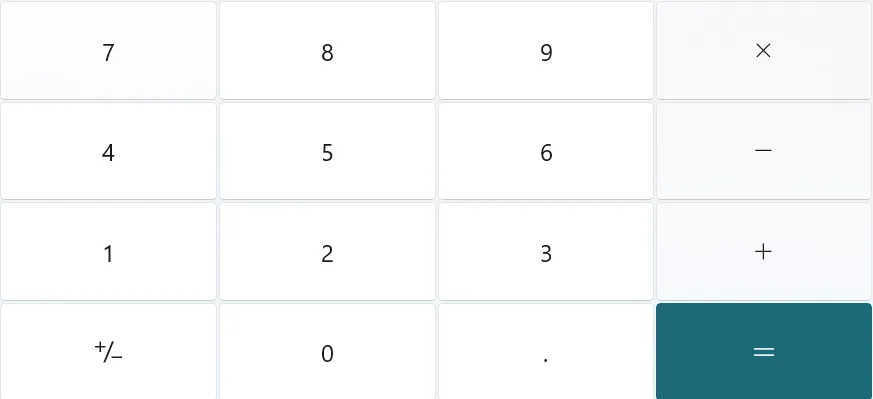

本计算器基于FPGA实现8位十进制数加、减、乘、除四则运算,通过4×4矩阵键盘输入数据与运算符,8个数码管实时显示输入数据及运算结果,支持连续运算功能。按下等号得到结果后,可直接输入数字开启新运算,或按下运算符将上一次结果作为本次运算的第一个操作数;清零按键可清除所有历史输入,多次输入运算符时仅最后一次生效,操作便捷贴合实际使用场景。

系统顶层模块作为枢纽,仅完成7个子模块的信号连线,各子模块分工明确。其中,矩阵键盘检测模块采用状态机实现逐行扫描与20ms消抖,精准识别按键位号并输出有效信号;控制模块作为核心,通过状态机实现按键识别、运算控制与显示数据分配,协调各模块有序工作。

部分代码展示:

运算模块均采用移位+加法架构设计,乘法器支持14位输入、27位输出,运算延迟可控;除法器支持27位输入,可精准输出商值,两者均避免了传统架构的资源浪费与频率限制。二进制转BCD码模块采用参数化设计,通过移位+加法算法,解决了除法+取余算法的弊端,可灵活适配不同位宽转换需求。

下载方式

后台回复“fpga”即可免费获取电子版

点赞

收藏

分享

夜雨聆风

夜雨聆风