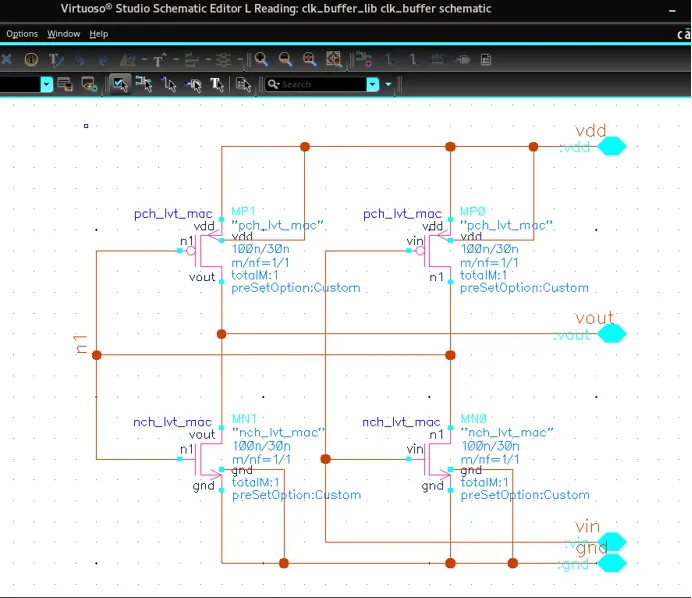

一、先搞懂:clkbuffer,芯片时钟系统的“核心守门员”在数字与模拟混合芯片中,时钟信号是芯片运转的“心跳”,而clkbuffer作为时钟链路的关键模块,承担着时钟信号放大、驱动增强、噪声抑制、相位稳定的核心作用。它虽属于基础模拟电路,却直接决定芯片的时序精度、抗干扰能力和整体功耗:- 要保证低抖动、低偏移,避免时钟失真导致芯片运行异常;- 需适配不同负载、电压与工艺角,满足宽温域工作需求;- 要兼顾功耗与驱动能力,平衡性能与芯片能耗。传统设计模式下,工程师需要手动选型拓扑、调试器件参数、反复跑SPICE仿真、优化电路结构,一个标准化clkbuffer模块的设计与验证,往往需要数天甚至一周时间,重复劳动极大,也占用了工程师攻克核心复杂电路的精力。二、OpenCLAW是什么?专为芯片设计的AI自动化利器OpenCLAW是一款开源AI智能体框架,核心架构由“大模型+执行引擎+专业工具插件”组成,区别于普通AI仅能提供设计建议,它能真正实现从需求理解、任务拆解到工具调用、执行优化的全闭环自动化,堪称芯片设计领域的“智能执行者”。针对模拟电路设计,OpenCLAW内置了专属EDA工具插件、仿真引擎和模拟电路知识库,可直接对接Cadence、SPICE等专业设计工具,无需人工操作,就能完成电路拓扑选择、参数优化、仿真验证、原理图生成等全流程工作,真正做到“一句话需求,AI自主完成设计”。三、从0到1:OpenCLAW生成clkbuffer的全流程揭秘本次clkbuffer的全自动生成,是OpenCLAW在模拟基础模块自动化的首次精准落地,全程遵循“需求输入→智能解析→拓扑选型→参数优化→仿真验证→输出交付”的闭环逻辑,每一步都由AI自主完成:1. 极简需求输入,无需专业代码工程师只需输入自然语言形式的设计需求,无需编写复杂脚本,比如:“设计一款CMOS工艺clkbuffer,电源电压3.3V,工作温度-40℃~125℃,输出时钟抖动<50fs,驱动10pF负载,低功耗设计”。OpenCLAW的智能体模块会快速解析需求,提取电压、温度、抖动、负载等核心性能指标,拆解为拓扑选型、参数计算、仿真验证等子任务,分配给对应专业智能体执行。2. 智能拓扑选型,匹配最优方案基于内置的模拟电路知识库,OpenCLAW会根据clkbuffer的性能需求,自动排除不兼容拓扑,筛选出最适配的差分clkbuffer经典拓扑,兼顾低抖动、强驱动与低功耗特性,同时给出选型依据,替代工程师手动判断的繁琐过程。3. 全自动参数优化,告别反复调试针对选定的拓扑,OpenCLAW调用内置优化算法,结合工艺文件自动计算晶体管宽长比、电阻电容值、偏置电流等关键参数,通过多目标优化,平衡抖动、功耗、驱动能力三大核心指标,一次性输出最优参数组合,省去人工逐参数调试的时间。4. 闭环仿真验证,自动迭代优化参数确定后,AI自主调用SPICE仿真引擎,自动生成网表,完成DC工作点、AC特性、瞬态响应、温度扫描、蒙特卡洛等全维度仿真,自动提取仿真数据与需求指标对比。若仿真结果不达标,AI会自主定位问题(如抖动超标、驱动能力不足),反馈至参数优化模块调整参数,重新仿真,直至完全满足设计要求,全程无需人工盯守。

一、先搞懂:clkbuffer,芯片时钟系统的“核心守门员”在数字与模拟混合芯片中,时钟信号是芯片运转的“心跳”,而clkbuffer作为时钟链路的关键模块,承担着时钟信号放大、驱动增强、噪声抑制、相位稳定的核心作用。它虽属于基础模拟电路,却直接决定芯片的时序精度、抗干扰能力和整体功耗:- 要保证低抖动、低偏移,避免时钟失真导致芯片运行异常;- 需适配不同负载、电压与工艺角,满足宽温域工作需求;- 要兼顾功耗与驱动能力,平衡性能与芯片能耗。传统设计模式下,工程师需要手动选型拓扑、调试器件参数、反复跑SPICE仿真、优化电路结构,一个标准化clkbuffer模块的设计与验证,往往需要数天甚至一周时间,重复劳动极大,也占用了工程师攻克核心复杂电路的精力。二、OpenCLAW是什么?专为芯片设计的AI自动化利器OpenCLAW是一款开源AI智能体框架,核心架构由“大模型+执行引擎+专业工具插件”组成,区别于普通AI仅能提供设计建议,它能真正实现从需求理解、任务拆解到工具调用、执行优化的全闭环自动化,堪称芯片设计领域的“智能执行者”。针对模拟电路设计,OpenCLAW内置了专属EDA工具插件、仿真引擎和模拟电路知识库,可直接对接Cadence、SPICE等专业设计工具,无需人工操作,就能完成电路拓扑选择、参数优化、仿真验证、原理图生成等全流程工作,真正做到“一句话需求,AI自主完成设计”。三、从0到1:OpenCLAW生成clkbuffer的全流程揭秘本次clkbuffer的全自动生成,是OpenCLAW在模拟基础模块自动化的首次精准落地,全程遵循“需求输入→智能解析→拓扑选型→参数优化→仿真验证→输出交付”的闭环逻辑,每一步都由AI自主完成:1. 极简需求输入,无需专业代码工程师只需输入自然语言形式的设计需求,无需编写复杂脚本,比如:“设计一款CMOS工艺clkbuffer,电源电压3.3V,工作温度-40℃~125℃,输出时钟抖动<50fs,驱动10pF负载,低功耗设计”。OpenCLAW的智能体模块会快速解析需求,提取电压、温度、抖动、负载等核心性能指标,拆解为拓扑选型、参数计算、仿真验证等子任务,分配给对应专业智能体执行。2. 智能拓扑选型,匹配最优方案基于内置的模拟电路知识库,OpenCLAW会根据clkbuffer的性能需求,自动排除不兼容拓扑,筛选出最适配的差分clkbuffer经典拓扑,兼顾低抖动、强驱动与低功耗特性,同时给出选型依据,替代工程师手动判断的繁琐过程。3. 全自动参数优化,告别反复调试针对选定的拓扑,OpenCLAW调用内置优化算法,结合工艺文件自动计算晶体管宽长比、电阻电容值、偏置电流等关键参数,通过多目标优化,平衡抖动、功耗、驱动能力三大核心指标,一次性输出最优参数组合,省去人工逐参数调试的时间。4. 闭环仿真验证,自动迭代优化参数确定后,AI自主调用SPICE仿真引擎,自动生成网表,完成DC工作点、AC特性、瞬态响应、温度扫描、蒙特卡洛等全维度仿真,自动提取仿真数据与需求指标对比。若仿真结果不达标,AI会自主定位问题(如抖动超标、驱动能力不足),反馈至参数优化模块调整参数,重新仿真,直至完全满足设计要求,全程无需人工盯守。

夜雨聆风

夜雨聆风