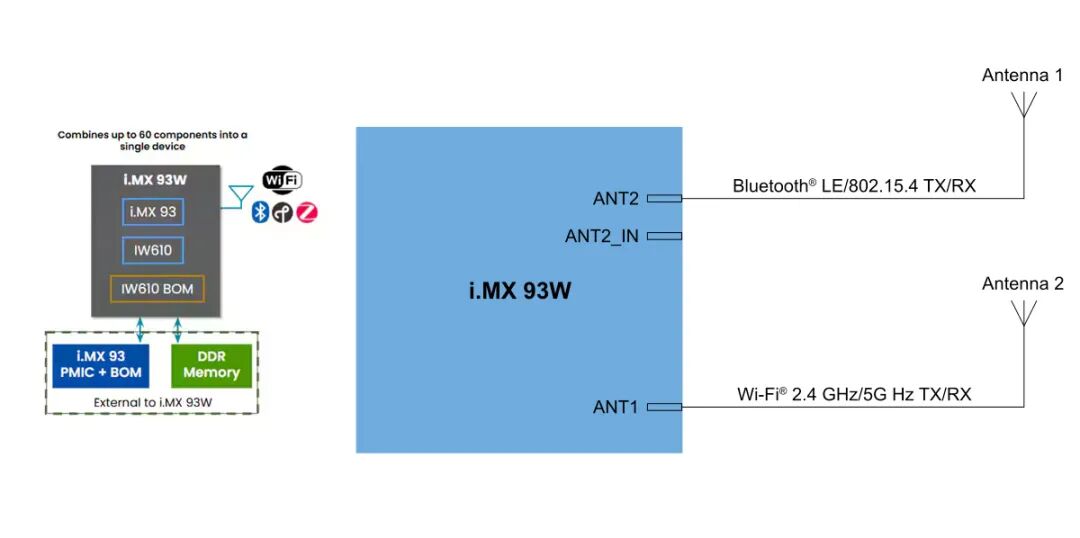

恩智浦i.MX 93W并非传统意义上的单芯片SoC,而是一颗采用系统级封装(System-in-Package, SiP)的异构集成器件。它在14.2×12毫米的FCCSP402封装内,通过基板级互连将i.MX 93应用处理器与IW610三频无线模组整合在一起,球间距0.5毫米,总共402个焊球。这种物理结构决定了其内部总线架构与电源域的划分逻辑——主芯片负责高算力应用处理与安全运算,IW610则通过SDIO或USB接口与主芯片通信,形成完整的边缘AI节点硬件底座。

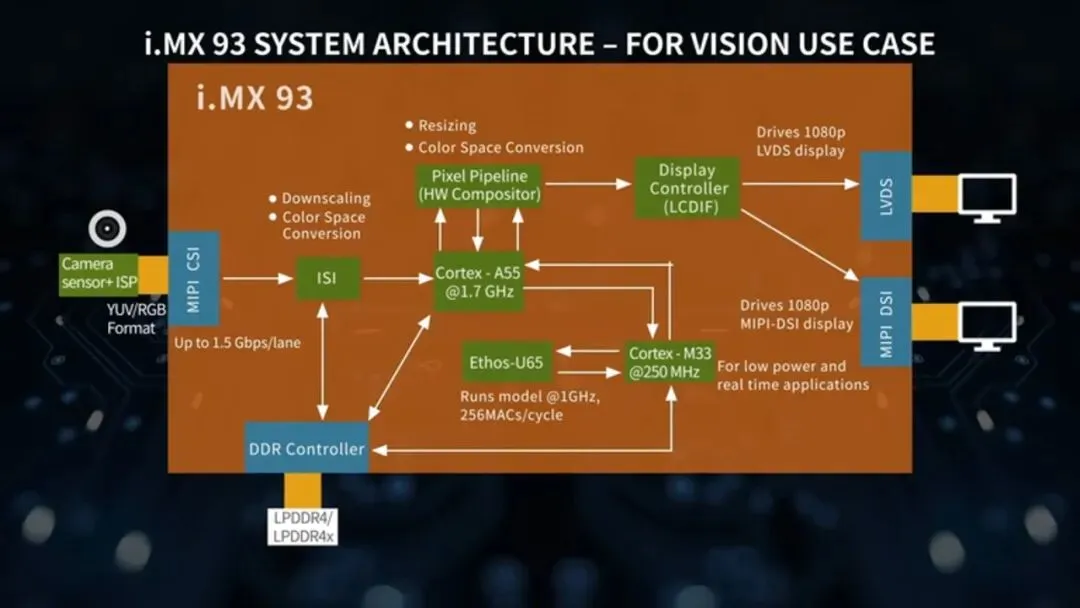

紧邻A55集群的左侧,是实时域(Real-Time Domain)的物理位置。这里集成了一颗Arm Cortex-M33内核,运行频率250MHz,配备16KB代码缓存与16KB系统缓存,拥有256KB TCM(Tightly-Coupled Memory),同样支持ECC。这颗M33并非简单的协处理器,而是拥有完整的NVIC中断控制器、FPU与MPU,可独立运行FreeRTOS或Zephyr RTOS。在物理AI应用中,M33通常负责传感器数据采集、实时控制与低功耗待机,而A55集群则保持休眠,直至被M33唤醒处理复杂推理任务。

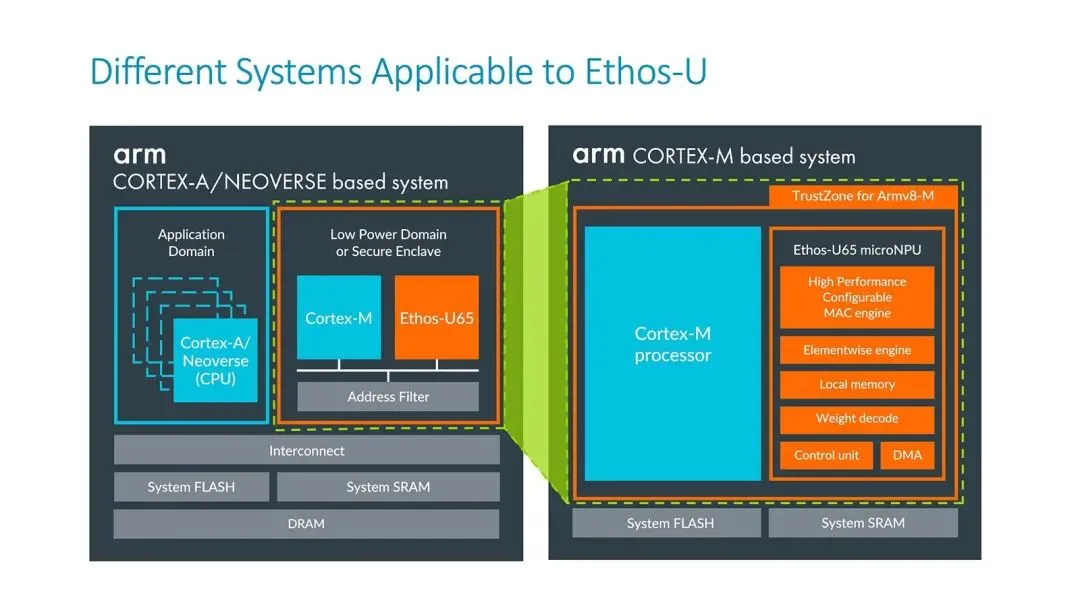

真正让i.MX 93W具备边缘AI能力的,是嵌入在实时域与应用域之间的Arm Ethos-U65 microNPU。这颗专用神经网络处理器采用可配置的MAC阵列设计,在i.MX 93W中配置为256 MACs/cycle,峰值算力达到1.8 eTOPs(每秒1.8万亿次操作),支持INT8与FP16混合精度推理。Ethos-U65的架构设计颇具巧思:它并非独立运行,而是作为Cortex-M33的从属加速单元存在,通过专用AMBA AXI接口与M33紧密耦合,同时通过系统总线访问外部DDR内存。这种架构下,M33负责NPU的任务调度与不支持算子的回退执行,而U65则专注于卷积、全连接等高强度矩阵运算。

在内存子系统方面,i.MX 93W的物理实现颇具特色。主芯片集成640KB OCRAM(On-Chip RAM),分布于三个电源域内,其中A55集群附近布置有256KB L3缓存,M33周围布置256KB TCM,剩余128KB作为系统RAM。这些片上内存均支持ECC,满足工业与汽车应用的可靠性要求。外部内存接口为16-bit LPDDR4/4X,最高速率3.7 GT/s,支持内联ECC,通过专用PHY与主芯片互联。值得注意的是,Ethos-U65在执行推理时,需要将模型权重从DDR预取到其本地的384KB SRAM中,这部分内存与OCRAM物理分离,位于NPU宏单元内部。

安全性是i.MX 93W架构设计的另一重点。芯片左下角集成了EdgeLock Secure Enclave(高级配置),这是一个独立的硬件安全子系统,拥有专用的安全CPU、加密引擎与密钥存储单元。物理上,它通过隔离总线与主系统连接,支持安全启动、远程认证、生命周期管理与防篡改检测。安全区内置真随机数生成器(TRNG)、AES-256/SHA-2/RSA-4096硬件加速器,以及用于安全时钟的专用振荡器。这种物理隔离架构使得即使主系统的Linux内核被攻破,安全区内的密钥与加密操作仍不受影响,满足PSA Certified Level 2与SESIP认证要求。

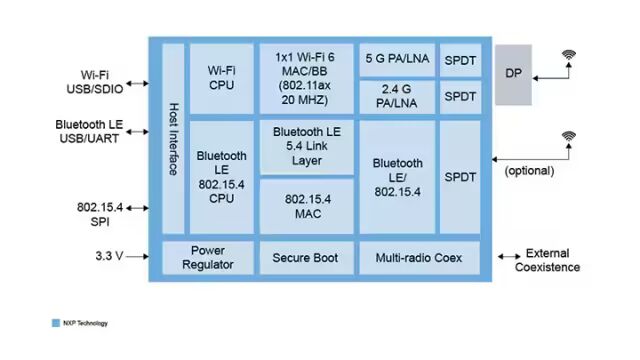

转向封装另一侧,IW610三频无线模组采用独立Die设计,通过封装基板与主芯片互联。IW610内部集成了三颗独立的射频收发器:一颗支持2.4/5GHz双频的Wi-Fi 6(802.11ax)收发器,物理层支持20MHz带宽、1024-QAM调制,最高速率1201Mbps;一颗支持Bluetooth 5.4的收发器,支持2Mbps LE Audio与长距离编码;以及一颗802.15.4收发器,用于Thread与Zigbee协议。三颗收发器共享基带处理单元,但拥有独立的射频前端与天线接口。

在i.MX 93W的SiP封装内,IW610通过SDIO 3.0或USB 2.0接口与主芯片通信,同时通过专用引脚与主芯片的"多射频共存仲裁器"(Multi-Radio Coexistence Arbiter)连接。这个硬件模块位于主芯片的 connectivity mix 区域,负责协调Wi-Fi、蓝牙与802.15.4的时分复用,避免同频干扰。仲裁器通过硬件信号线实时监测各射频的活动状态,在物理层实现优先级调度,这比软件调度降低了约60%的冲突延迟。

互联架构方面,i.MX 93W内部采用多层AXI总线结构。主系统通过NIC-400互连矩阵连接各主设备(A55、M33、DMA、以太网MAC)与从设备(DDR控制器、外设寄存器)。值得注意的是,芯片集成了两个增强型DMA控制器(eDMA3与eDMA4),分别拥有32通道与64通道,支持scatter-gather与通道抢占。这些DMA引擎位于WAKEUPMIX与AONMIX(Always-On Mix)区域,可在主CPU休眠时独立搬运数据,配合M33实现微安级待机功耗。

外设接口的物理分布也体现了低功耗设计理念。芯片底部集中布置了所有高速接口:两路千兆以太网MAC(其一支持TSN时间敏感网络)、两路USB 2.0 OTG、两路CAN-FD、MIPI-CSI/DSI PHY、以及FlexSPI接口。这些接口的I/O Pad支持1.8V/3.3V双电压,通过独立的电源域供电,可单独关闭未使用的外设以节省功耗。例如,当仅使用Wi-Fi连接时,以太网PHY的电源域可完全断电。

从芯片的物理实现来看,i.MX 93W的功耗管理单元(PMU)采用分布式设计。片内集成多个低压差线性稳压器(LDO)与开关电源控制器,由外部PMIC统一供电。芯片支持多种低功耗模式:在RUN模式下,A55与M33全速运行,功耗约500mW;在IDLE模式下,A55时钟门控,M33保持运行,功耗降至数十毫瓦;在DSM(Deep Sleep Mode)下,仅保留AON域与安全区供电,功耗可低至微瓦级。这种精细的电源域划分,使得i.MX 93W能够在工业网关等场景中,仅靠纽扣电池维持RTC与安全监控功能数年时间。

综合来看,i.MX 93W的架构设计体现了"物理AI"时代对边缘计算设备的严苛要求:通过SiP封装实现计算与连接的极致集成,通过异构多核(A55+M33+U65)实现性能与功耗的动态平衡,通过硬件级安全区满足合规要求,通过预认证的射频设计降低量产门槛。这颗芯片的每一块硅片面积、每一条总线走向、每一个电源域的划分,都在回答同一个问题——如何让AI智能体在边缘端可靠、安全、持久地运行。

夜雨聆风

夜雨聆风