高速信号完整性

当前 AI 芯片、HBM、Chiplet、先进封装全面爆发,高速信号完整性(SI) 已从 “可选优化” 变成芯片量产与系统稳定的核心门槛。信号一旦失真、抖动、串扰、衰减,直接导致:接口不兼容、速率上不去、批量失效、车规 / 服务器认证不过关,甚至全盘返工。

Part.01

为什么高速信号完整性测试至关重要?

速率越高,越脆弱

PCIe 6.0、112G/224G、DDR5、CPO 等接口速率飙升,信号完整性问题呈指数级放大,传统检测手段完全失效。

先进封装倒逼高精度验证

CoWoS、2.5D/3D IC 堆叠后,垂直互连、串扰、阻抗不连续问题剧增,检测复杂度比传统封装提升 300%+,必须依赖专业 SI 实验室。

车规 / 服务器 / AI 芯片强制要求AEC‑Q100、OCP、PCI‑SIG 等标准对眼图、抖动、时序、误码率有严苛合规门槛,第三方 SI 测试是通过认证的关键。

成本与时间的 “止损点”

流片后再改板代价百万级;SI 前置仿真 + 测试可提前规避 90% 以上高速问题,大幅缩短研发周期、降低返工成本。

上海磐测能做什么:

高速信号完整性一站式方案

Part.02

上海磐测信息技术(iPasslabs)专注高速信号测试与信号完整性 SI,为芯片、系统、封装、PCB 提供从仿真到验证的全流程服务。

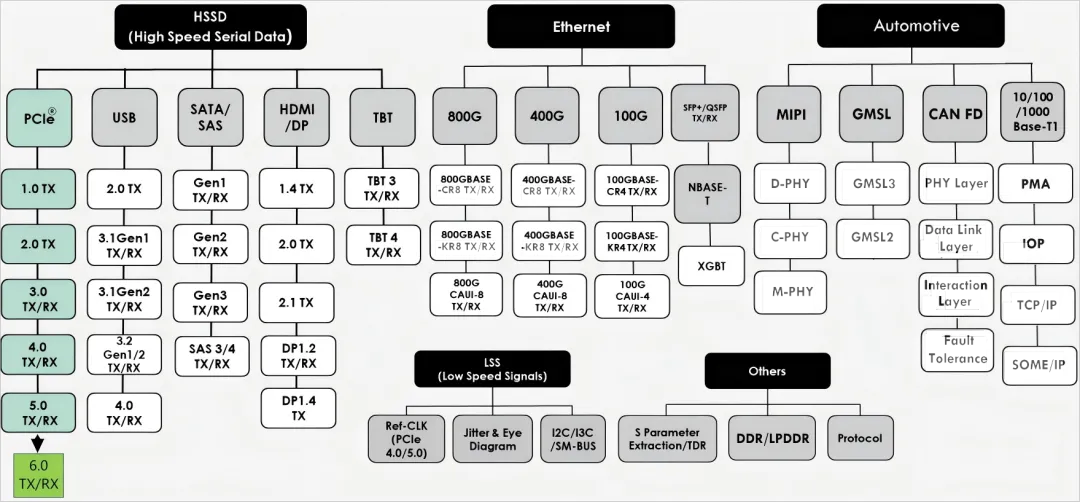

1. 核心测试能力(覆盖主流高速接口)

PCIe Gen5/Gen6 全链路一致性测试

112G/224G 数据中心高速互联电气 & 光接口测试

DDR5/4 信号完整性与时序测试

USB4、HDMI2.1、DP、MIPI、SATA/SAS 高速接口测试

眼图、抖动、阻抗、串扰、S 参数、插入损耗、回波损耗

定制化 SI 仿真、调试、问题定位

2. 磐测核心优势

顶级硬件平台配备59GHz 超高带宽实时示波器、误码率测试仪、高频探针台与专业夹具系统。

自研夹具与测试板自主 PCIe Gen5/Gen6 测试夹具、112G ISI Board,精度对标国际一线,支持快速量产验证。

全流程服务设计前期SI 仿真→原型测试验证→量产一致性认证→问题定位 Debug,一站式交付。

标准合规背书:PCI‑SIG 授权认证实验室,测试方案符合车规、服务器、AI 芯片合规要求。

为客户专属定制EVB、测试夹具

Part.03

信号完整性测试到底测什么?

(极简看懂)

Science & Technology

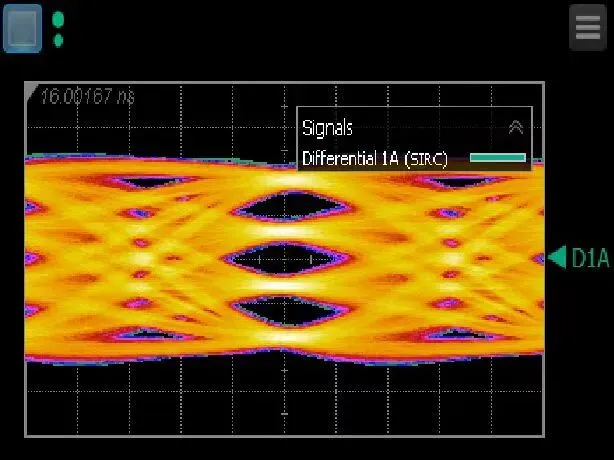

眼图测试:看 “眼睛睁得大不大”,判断信号质量与抗干扰能力

抖动分析 Jitter:随机 / 周期抖动,决定高速链路能否稳定跑满速率

阻抗与 S 参数:把控传输线 “高速公路” 是否平顺

时序与建立 / 保持时间:保证芯片 “说话与听话” 同步不出错

串扰与噪声:避免高速线互相 “干扰打架”

哪些客户必须做 SI 测试?

Part.04

AI/GPU/ 算力芯片、HBM、先进封装(CoWoS/2.5D/3D);

车规 MCU、功率器件、域控制器、ADAS 平台;

服务器、存储、PCIe 卡、高速交换芯片;

高频 PCB / 封装设计公司、IC 设计公司。

上海磐测寄语

在半导体行业从规模扩张转向高质量发展的关键阶段,高速信号完整性不再是 “锦上添花”,而是产品能否上车、上线、上市的底线能力。

上海磐测以高精度、高标准、高效率的 SI 测试与仿真服务,助力客户攻克高速互联瓶颈,守住芯片可靠性底线,与中国半导体产业共同迈向更高性能、更自主可控的未来。

扫描下方二维码 关注我们

夜雨聆风

夜雨聆风