主流STA工具解析

在数字芯片设计中,时序分析不仅是工具能力的体现,更是工程方法论的体现。不同平台背后代表不同流程理念与风险控制策略。欢迎参与投票,看看行业主流选择,也欢迎在评论区分享你的 STA 实战经验与观点。

在数字芯片设计流程中,STA 是连接逻辑实现与物理实现的关键节点。Setup、Hold、Clock Skew、OCV、Path Group 等指标,并不是简单的报表数字,而是芯片能否在目标频率下稳定运行的基础。随着先进工艺节点的演进,PVT 变化、寄生提取精度与功耗耦合效应不断增强,STA 的复杂度和重要性持续提升。

1. STA 的核心技术挑战

-

MCMM 多模式多角分析

先进节点设计往往需要覆盖数十甚至上百个 Mode/Corner 组合。不同电压、温度、工艺偏差下,时序路径的延迟变化明显。高效的 MCMM 引擎不仅要保证精度,还要具备容量与并行能力。

-

OCV 与变异建模

On-Chip Variation(OCV)模型不断演进,从传统 derate 到 AOCV、POCV,工具需要支持复杂的统计时序分析能力,否则签核风险显著增加。

-

与物理实现的闭环

STA 不再是孤立环节。寄生参数(SPEF)、SDF 回标、功耗分布与 IR Drop 信息都会影响最终时序结果。工具与后端实现平台的耦合程度,直接决定迭代效率。

2. 主流签核平台解析

-

Synopsys PrimeTime: 签核标准的代表

PrimeTime 长期作为先进节点 Signoff 工具的主流选择。其优势体现在:

-

成熟稳定的 MCMM 引擎

-

强大的约束解析能力

-

与 Design Compiler、IC Compiler 的深度整合

-

广泛的 foundry 认证支持

在 5nm、3nm 等先进工艺中,签核准确性与生态兼容性成为其核心价值。

-

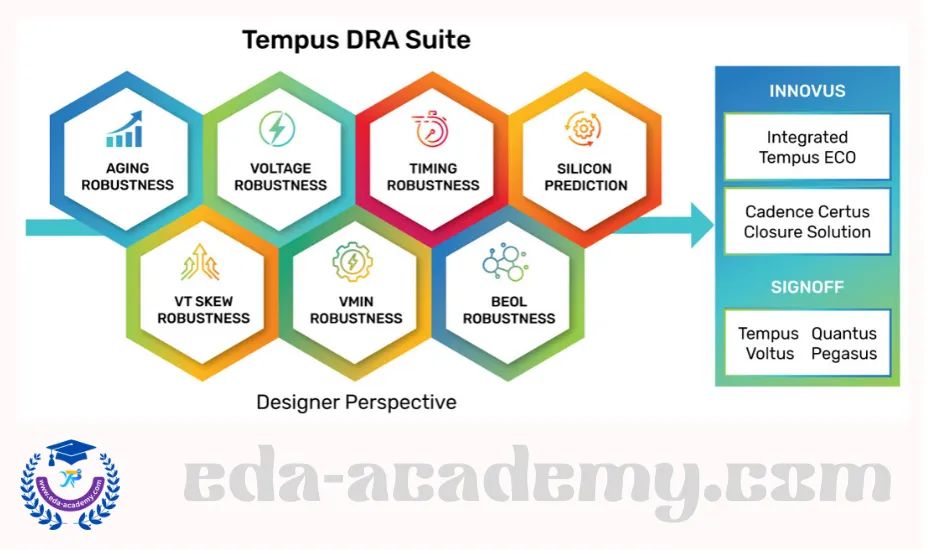

Cadence Tempus: 统一流程中的 STA 核心

Tempus 是 Cadence 数字实现平台中的关键组件,与 Genus、Innovus 形成统一流程。其技术特点包括:

-

分层与并行分析能力

-

高容量大规模设计支持

-

功耗感知时序分析

-

流程一体化带来的数据一致性

在强调前后端协同与快速收敛的项目中,这种统一流程优势明显。

-

其他商业工具: 差异化与区域生态

部分工具更专注于特定场景:

-

功耗耦合与 IR Drop 感知分析

-

早期估算或验证用途

-

本地化支持与成本优势

在某些区域市场或特定细分领域,它们承担辅助或补充角色,但在先进节点大规模签核场景中使用比例相对较低。

-

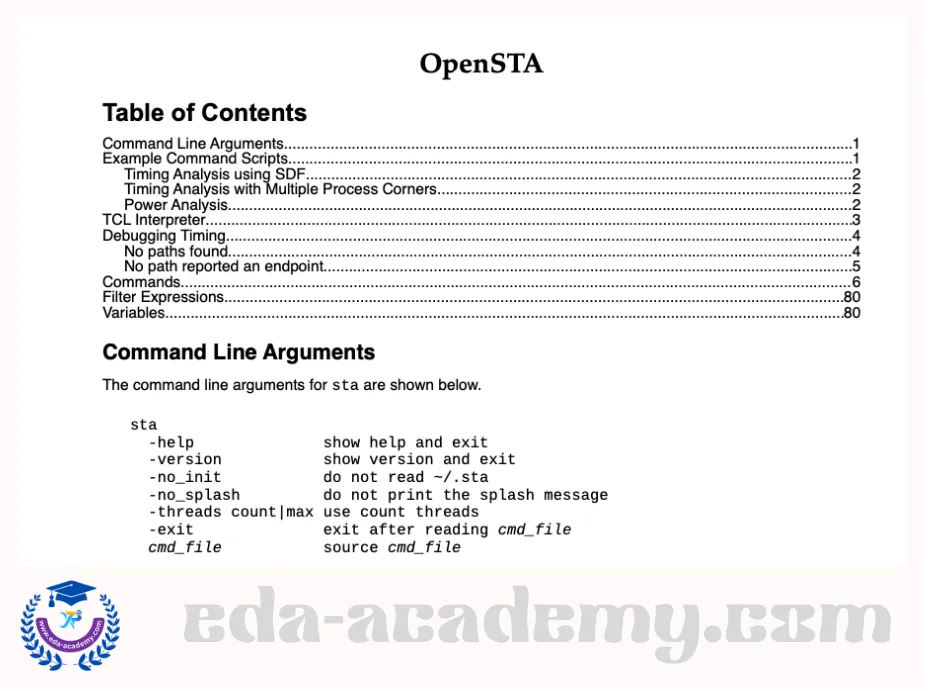

开源与混合流程: 学习与研究平台

OpenSTA、OpenTimer 等工具多用于教学、研究或开源流片项目。优点在于:

-

开放架构

-

易于二次开发

-

适合理解时序原理

但在复杂 PVT 角覆盖、统计建模与 signoff 级精度方面,仍存在明显差距。

3. 工具选择背后的逻辑

选择 STA 平台通常受以下因素影响:

-

公司整体 EDA 生态

-

目标工艺节点

-

设计规模与复杂度

-

与后端实现工具的协同效率

-

Foundry 认证与客户要求

在先进节点项目中,签核工具往往不是单纯技术选择,而是风险管理决策。

4. STA 的未来趋势

-

更强的统计时序能力

-

与功耗、电源完整性更深耦合

-

云端高容量并行分析

-

AI 辅助路径优化

随着设计规模持续扩大,STA 不再只是“跑报表”,而是数据驱动优化的重要环节。

END

《EDA网院》出品 · 与全球工程师一起探索芯片的世界

夜雨聆风

夜雨聆风