01

SoC设计实战

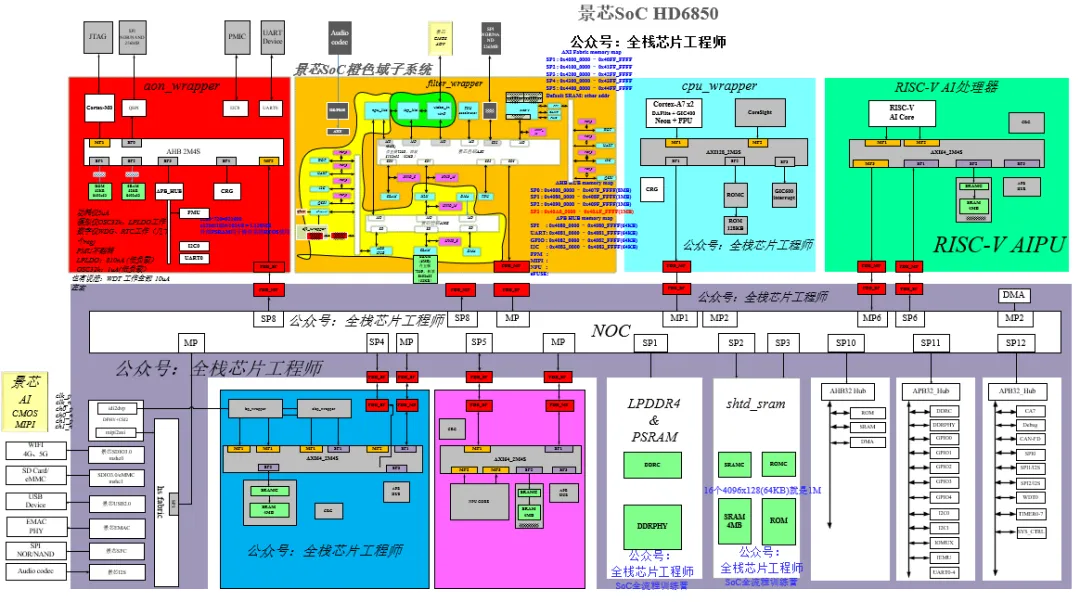

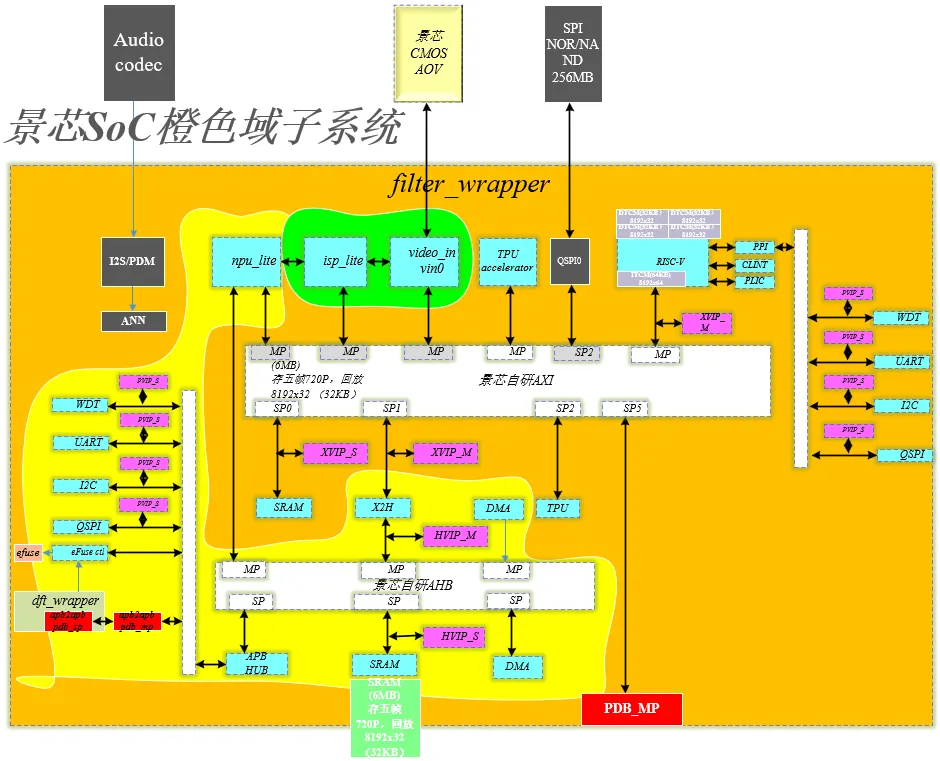

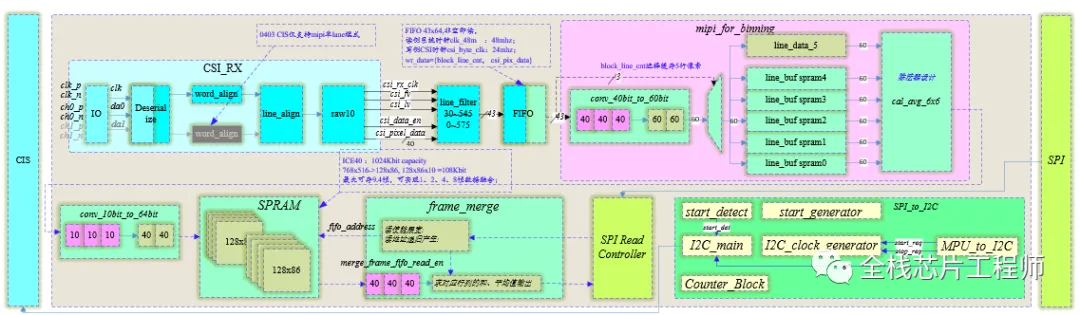

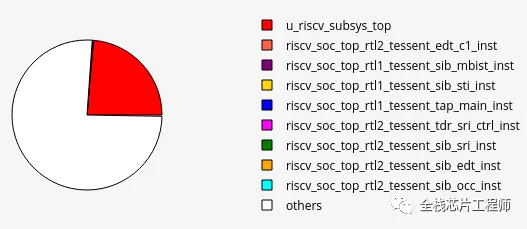

橙色子系统采用低功耗RISC-V架构,全部自研实现了AXI总线矩阵、AHB总线矩阵、ISP-Lite、NPU-lite、MIPI DPHY软核、SRAM、DMA、UART、I2C、QSPI/SPI等常用IP,项目设计验证架构如下:

景芯橙色域子系统分为三个subchip子系统,包括media_wrapper、amba_wrapper、cpu_wrapper三个subchip,每个subchip的功能描述如下:

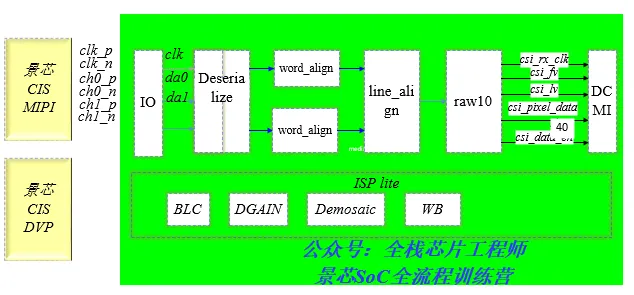

media wrapper(上图青色部分)负责MIPI图像输入、DPV图像输入、异步处理、ISP图像处理。

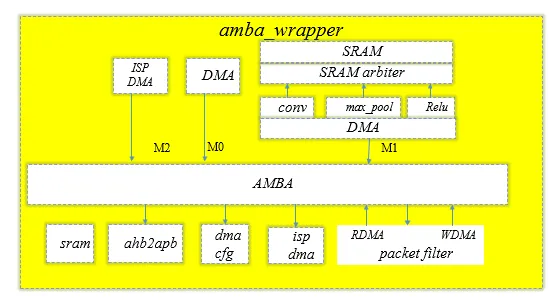

amba wrapper(浅黄色部分)负责接收media wrapper传递过来的经过ISP预处理过的图像,通过专用DMA搬运数据到amba wrapper系统主存SRAM,DMA搬运完成后,CPU配置NPU搬运系统主存SRAM的图像数据去做矩阵运算(卷积)。

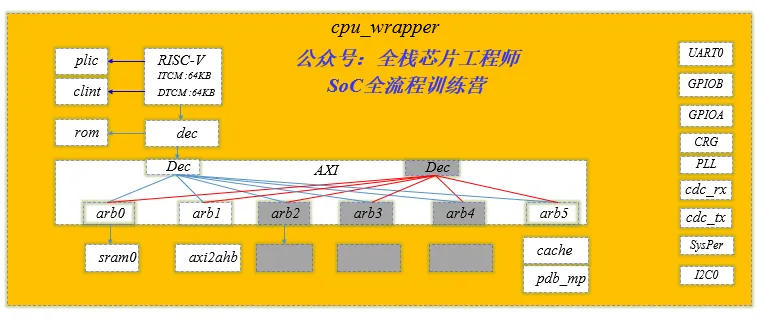

cpu wrapper负责RISC-V CPU、TCM、自研AXI总线矩阵的译码、仲裁、AXI2AHB总线桥、中断系统、低功耗PMU管理等功能。NPU卷积完成后,RISC-V CPU执行WFI指令进入休眠模式。通过isolate信号和retain信号进行时钟门控、电源门控。

为了满足不同经验的学员需求,景芯开发了两套环境分别作为进阶课和基础课,带您一起手搓AXI总线矩阵、AHB总线矩阵、ISP-Lite、NPU-lite、MIPI DPHY软核、SRAM、DMA、UART、I2C、QSPI/SPI等常用IP,让您快速掌握架构、总线协议、接口协议、图像算法、软硬件协同验证等设计核心,让您快速超越同龄人!

02

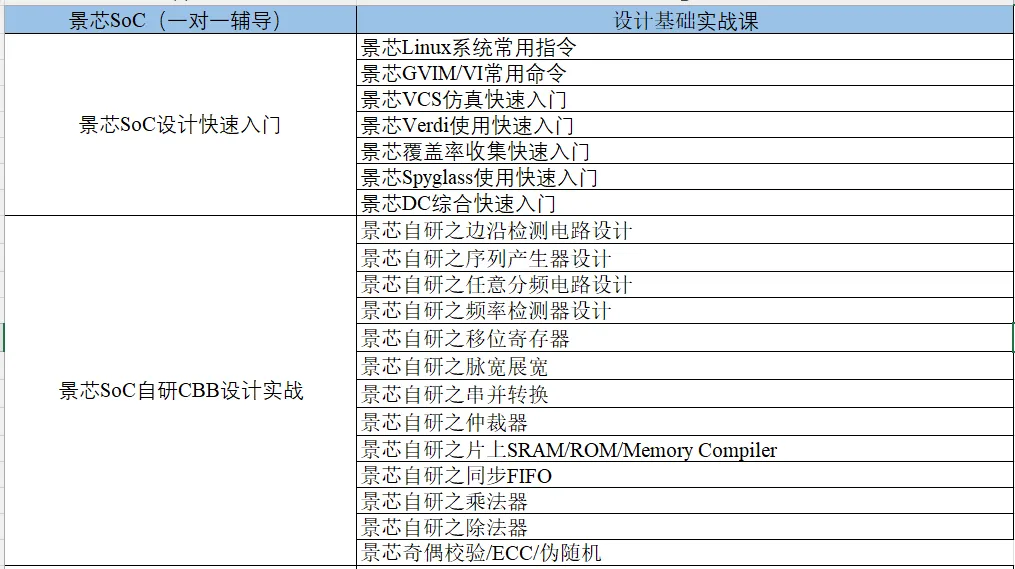

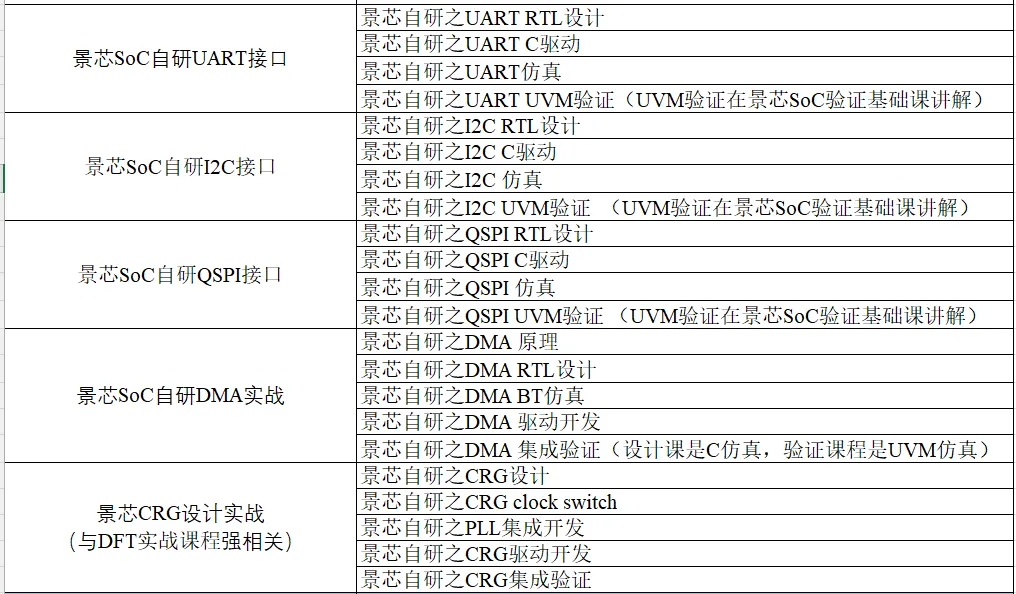

设计实战基础课目录

Part.01

设计实战基础课

一对一辅导是景芯SoC全流程训练营的特色!景芯SoC设计实战基础课最新课表如下:

Part.02

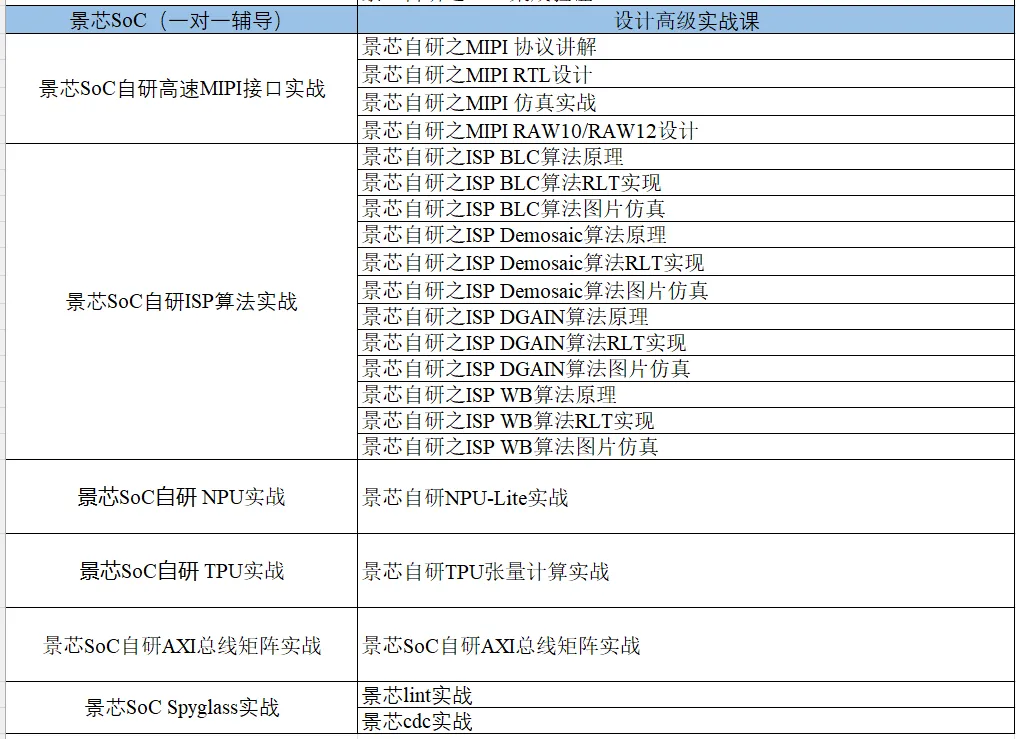

设计实战进阶课

景芯SoC设计实战进阶课最新课表如下(买进阶课、送基础课):

Part.06

课程报名微信,扫描咨询我们吧

景芯SoC芯片全流程实战附属【知识星球】,一个包括设计、验证、DFT、后端全流程技术的交流平台,也是景芯学员的答疑平台!若您和我一样渴求技术,那欢迎扫下面二维码加入星球,共同进步!

03

景芯团队Design Service提供哪些服务?

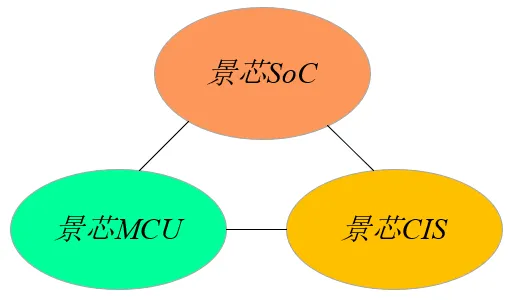

景芯主营业务是design service+一对一芯片辅导培训!景芯团队将持续打磨芯片全流程技术,边缘AI时代,景芯团队一定成!景芯团队提供的芯片Design Service设计服务包括:

提供SoC、MCU、ISP、CIS等芯片设计、验证、DFT、后端服务

提供DDR/PCIE/MIPI/ISP/NPU/VPU/CAN/USB/ETH等复杂IP设计

提供7nm、12nm、28nm、40nm、55nm、65nm、90nm等后端设计

提供高校、企业定制化芯片设计服务、设计培训业务

景芯团队为客户定制了数款A55、A7系列SoC芯片,皆一版成功!

景芯团队为客户定制了数款M7、M3/4、M0系列MCU芯片!

景芯团队为客户定制了数款RISC-V系列MCU芯片!

景芯团队为客户定制了数款CIS芯片以及ISP模块化设计!

04

景芯SoC训练营项目有什么亮点?

亮点1:景芯SoC自研MIPI解码

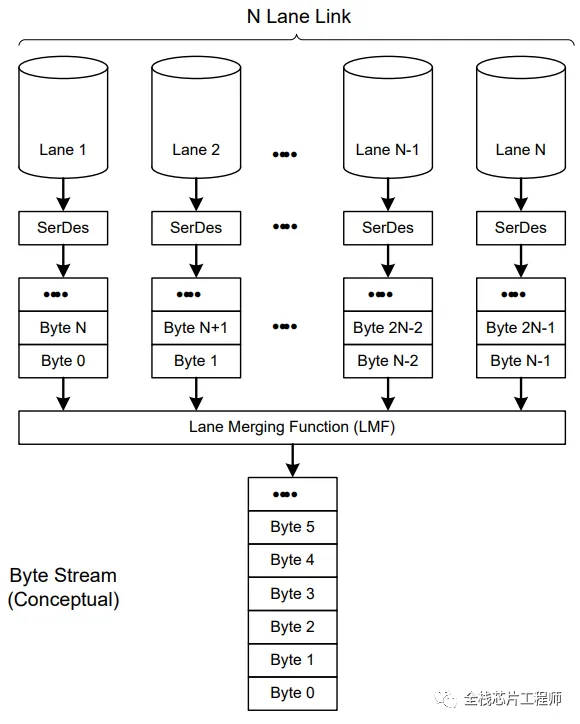

数字电路中经典设计:多条通信数据Lane Merging设计实现

数字电路中经典设计:多条通信数据Lane Distribution实现

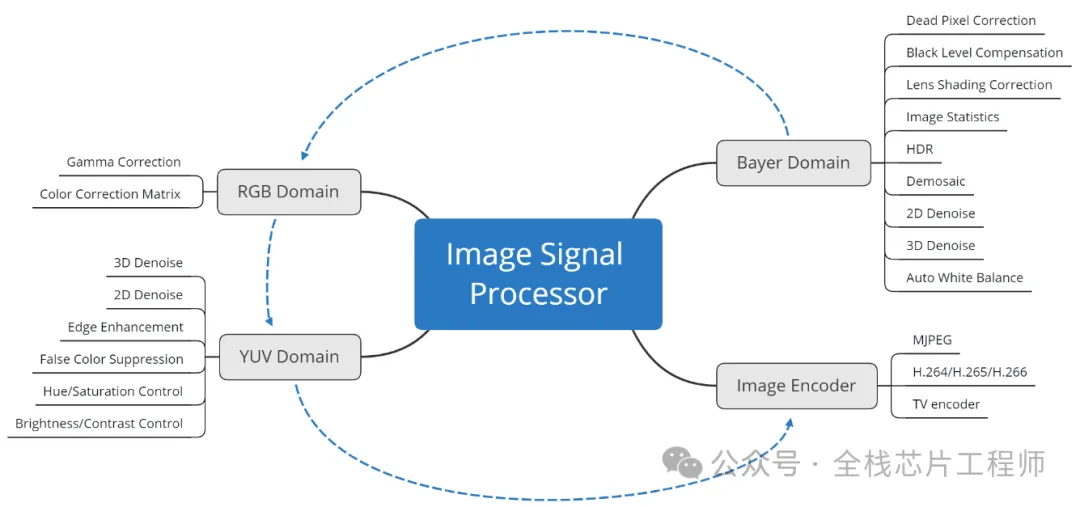

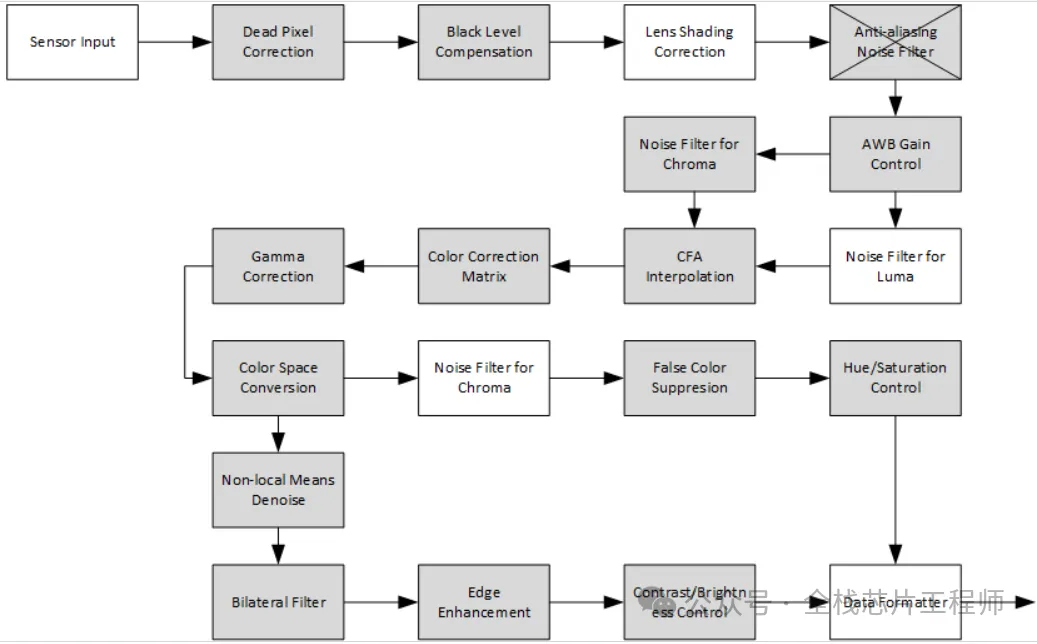

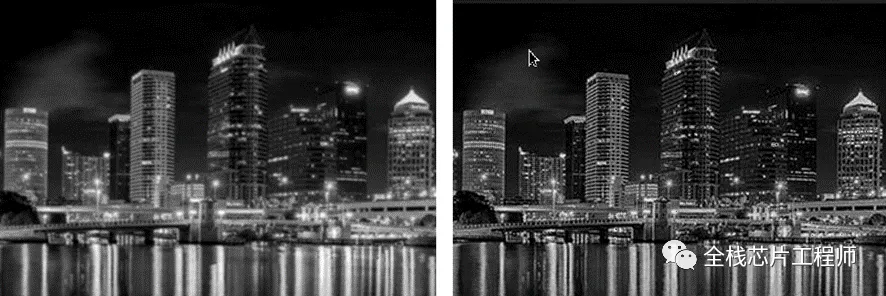

亮点2: 景芯SoC自研ISP图像处理

✅dpc - 坏点校正

✅blc - 黑电平校正

✅bnr - 拜耳降噪

✅bnr - 拜耳降噪

✅dgain - 数字增益

✅demosaic - 去马赛克

✅wb - 白平衡增益

✅ccm - 色彩校正矩阵

✅csc - 色彩空间转换 (基于整数优化的RGB2YUV转换公式)

✅gamma - Gamma校正 (对亮度基于查表的Gamma校正)

✅ee - 边缘增强

✅stat_ae - 自动曝光统计

✅stat_awb - 自动白平衡统计

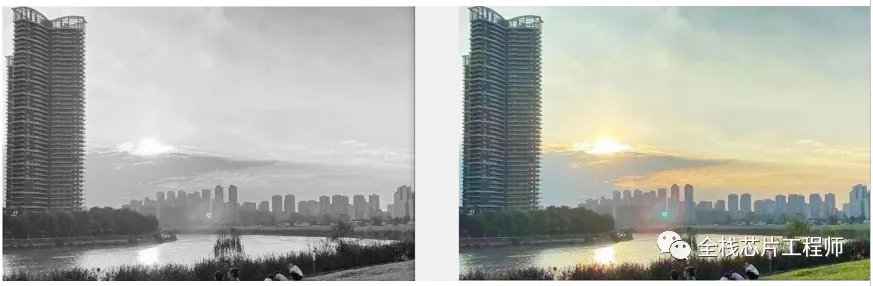

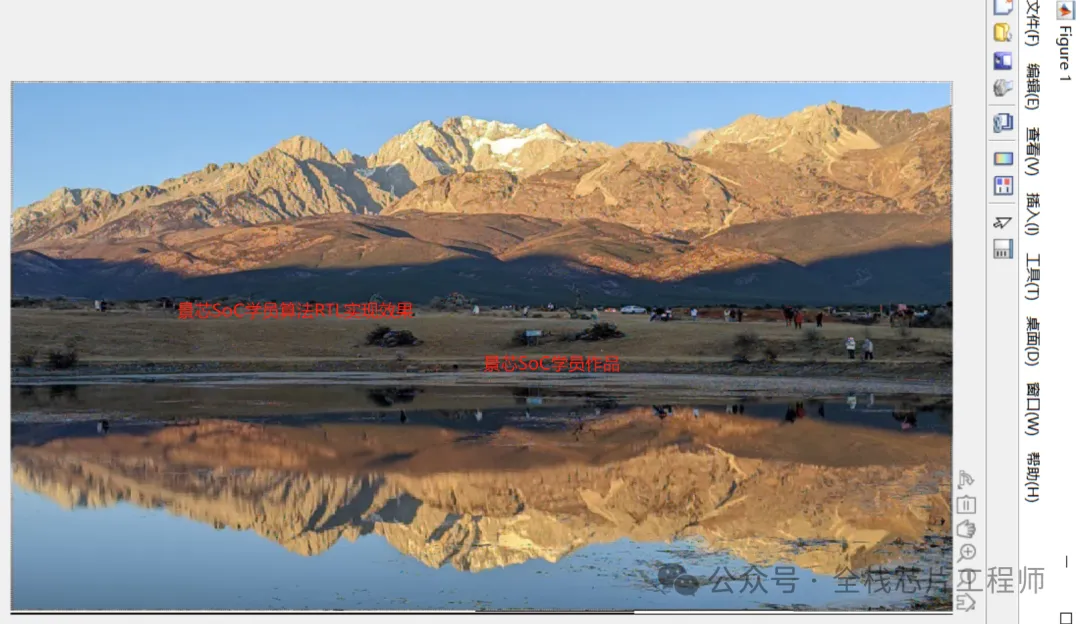

【景芯SoC学员ISP算法实现的作品】:

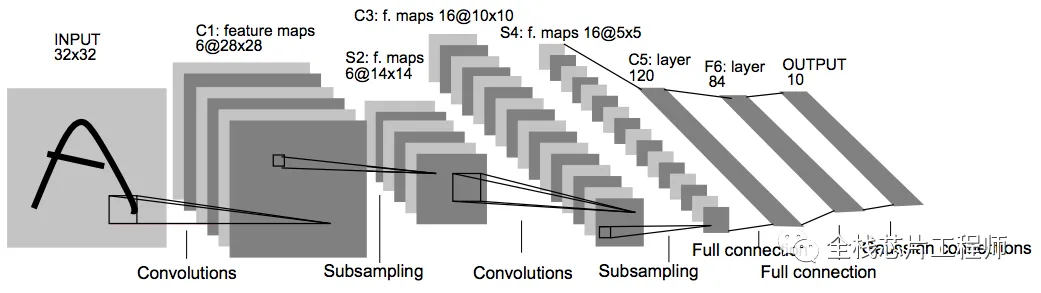

亮点3:景芯SoC自研NPU

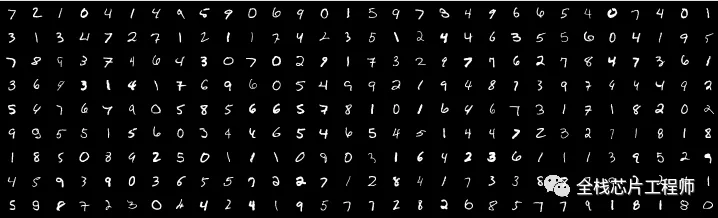

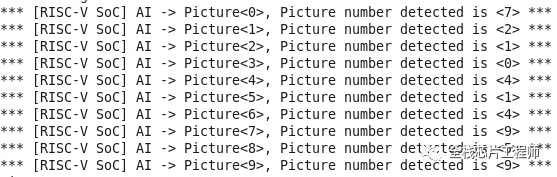

支持手写数字的AI识别:

仿真结果:仿真识别上图7、2、1、0、4、1、4、9

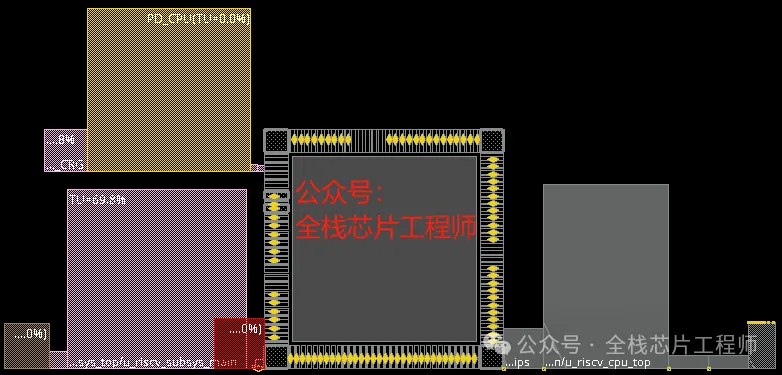

亮点4:景芯SoC UPF低功耗设计

全芯片UPF低功耗设计(含DFT设计)

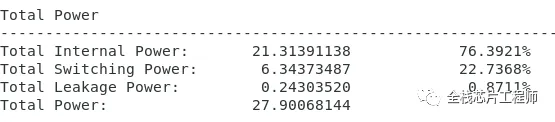

景芯SoC训练营培训项目,低功耗设计前,功耗为27.9mW。

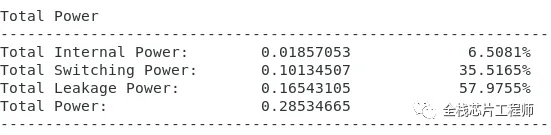

低功耗设计后,功耗为0.285mW,功耗降低98.9%!

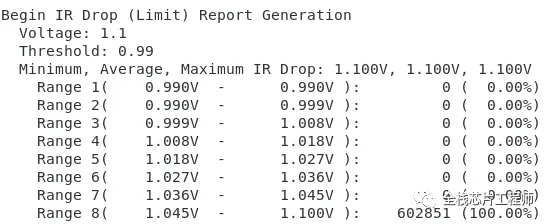

电压降检查:

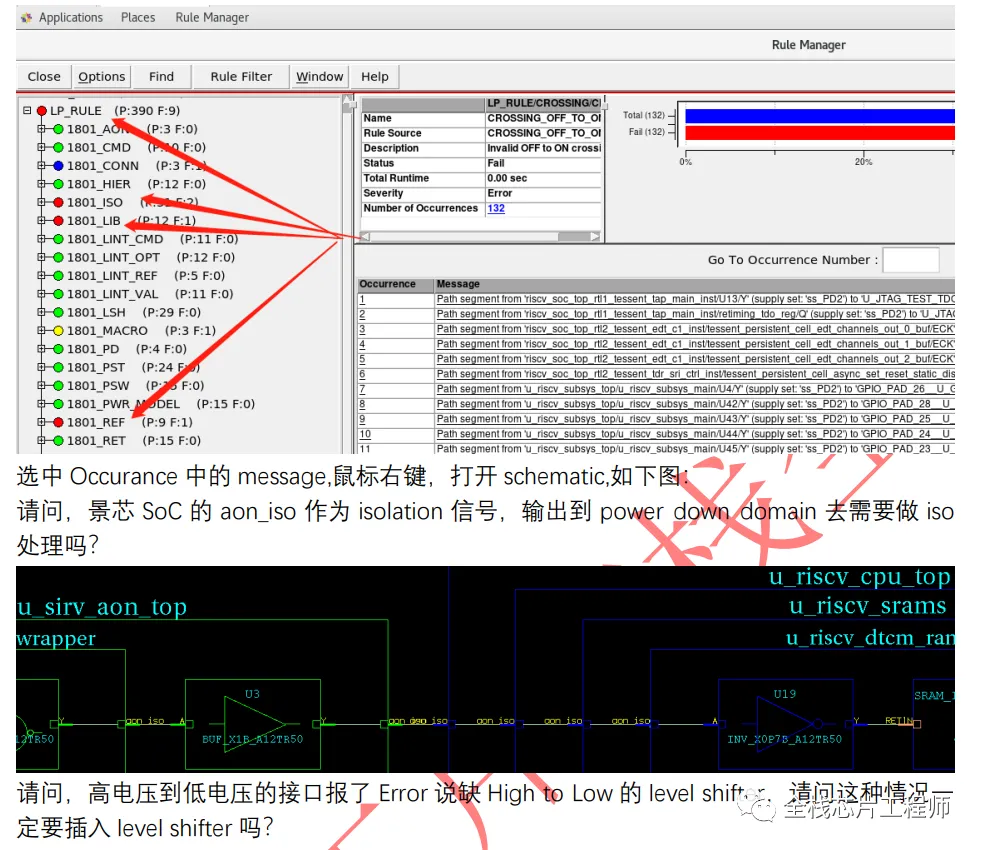

低功耗检查:

低功耗设计的DRC/LVS,芯片顶层的LVS实践价值极高,具有挑战性!业界独一无二的经验分享。

05

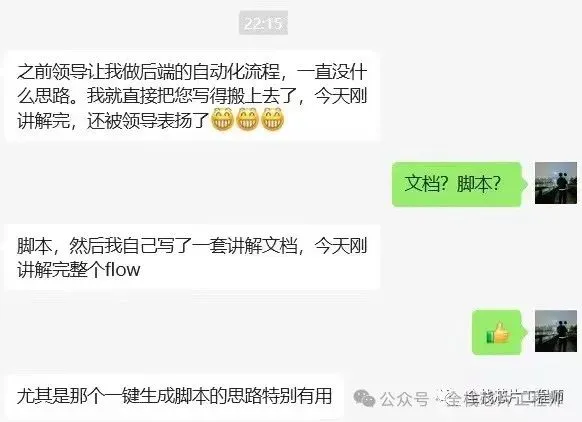

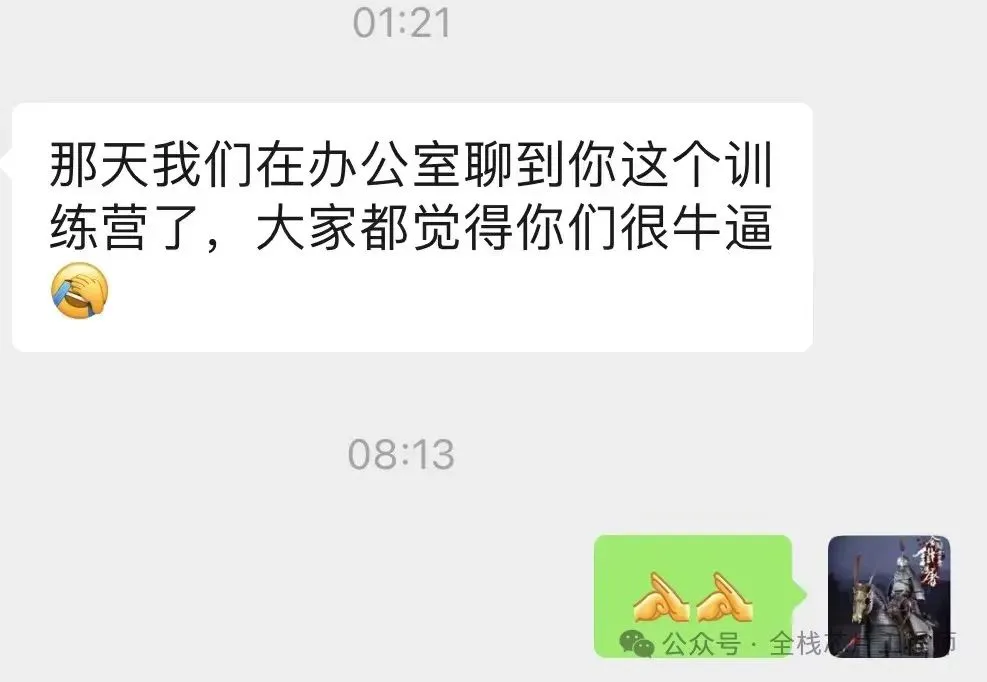

景芯SoC训练营好评如潮

十分感谢景芯学员们对景芯的信任和支持,景芯团队一定更努力精心打磨景芯SoC实战课,让大家无论资深还是资浅都能从景芯训练营获得成长!

最近学员纷纷咨询小编offer选择的问题,看到大家通过景芯培训提升后拿到心仪的offer了,非常开心,祝贺大家都拿到心仪offer了!

另外,小编的一个景芯VIP学员,成都某985,硕士7年经验,之前通过景芯培训提升后拿到心仪的offer了,这3个offer我看了都眼红!上次发起了投票,今天公布下结果。先来看下三个offer情况:

1、 某GPU公司,月薪5.8w,年终4个月合计23.2万,年薪92.8万,岗位是SoC前端设计,公积金12%;

2、多媒体SOC厂商JC,月薪6.5w,年终奖2个月合计13万,年薪91万,岗位是SoC芯片设计工程师,公积金12%;

3、 国企X微电子,月薪5.5W,年终奖4个月合计22万,年薪88万,担任数字ic设计工程师,主要从事SOC芯片设计,公积金10%

这里补充发布上次大家的投票结果公布:

从结果可以看出,市场行情不好,大家都看好国企军工的稳定性了,GPU仍然是技术首选,虽然GPU公司都在厮杀,但是仍有前景,但是IPC SOC反而得票最低,内卷同时没有太大增量市场。

另外,景芯资深老学员告诉我,留学X国的硕士去外企某芯片巨头薪资是20万+美金!折合RMB超过140万,才25岁左右的小伙子!薪资超140万!努力学习技术吧 骚年。

课程报名微信:

06

招聘:景芯SoC学员供不应求

职位:SoC 数字前端设计工程师

岗位职责:

1、根据设计需求,完成 SoC 芯片中子模块的设计、集成、仿真等工作;

2、根据设计需求,完成第三方 IP 的配置、集成、仿真等工作;

3、完成 sdc、upf 的编写和检查,完成综合与 formal check 等工作;

4、完成性能、功耗分析;

5、支持 FPGA 和 emulator 原型验证;

6、支持中后端工作,协助完成时序收敛;

7、支持芯片 bringup,支持软件驱动开发及应用方案开发。

任职要求:

1、微电子、电子工程等相关专业硕士及以上学历,三年以上工作经验;

2、精通 Verilog/SystemVerilog 硬件描述语言,具备规范化代码设计能力。

3、深入理解 SoC 设计流程,熟练使用 VCS, Verdi, Spyglass, DesignCompiler 等 EDA 工具;

4、参与/掌握以下一项或者多项技术:

1) CPU, NoC, DDR, MIPI CSI, MIPI DSI, USB, 外设等 IP 的设计或集成;

2)AMBA 总线协议;

3)低功耗设计;

4)带宽评估与优化;

5)Python/Tcl 脚本开发,实现自动化流程。

5、具有良好的表达沟通能力及团队合作精神,具有较强的独立工作能力和动手能力;

6、良好的英文阅读、文档编写能力。

职位:数字前端设计工程师(ISP方向)

任职要求:

1、熟练掌握 Verilog HDL,能够使用 RTL 描述复杂数字电路;

2、熟悉 VCS/Verdi 等常见 debug 工具,能够对大规模数字电路进行仿真及 debug;

3、能够采用 Design compiler(或 Quartus/Vivado/Synplify 等 FPGA 工具)对 RTL 设计进行综合并分析时序、 面积;

4、熟悉 DDR 读写原理,熟悉常见片上总线规范(例如 AMBA AXI);

5、熟悉数字图像信号处理(ISP)、图像降噪、图像画质增强等相关方向。

岗位关键字:

数字前端设计,ASIC 前端设计,RTL 设计、ISP,图像降噪、图像画质增强。

职位:数字前端设计工程师(视频处理方向)

任职要求:

1、熟练掌握 Verilog HDL,能够使用 RTL 描述复杂数字电路;

2、熟悉 VCS/Verdi 等常见 debug 工具,能够对大规模数字电路进行仿真及 debug;

3、能够采用 Design compiler(或 Quartus/Vivado/Synplify 等 FPGA 工具)对 RTL 设计进行综合并分析时序、 面积;

4、熟悉 DDR 读写原理、熟悉常见片上总线规范(例如 AMBA AXI);

5、对视频编解码、GPU、GE2D、Display Engine 等机器视觉相关方向有强烈的学习意愿。

岗位关键字:

数字前端设计,ASIC 前端设计,RTL 设计、视频编解码(H.264/H.265/HEVC),GPU,GE2D、Display Engine。

职位:数字前端设计工程师(AI 人工智能方向)

任职要求:

1、熟练掌握 Verilog HDL,能够使用 RTL 描述复杂数字电路;

2、熟悉 VCS/Verdi 等常见 debug 工具,能够对大规模电路进行仿真 debug;

3、能够采用 Design compiler(或 Quartus/Vivado/Synplify 等 FPGA 工具)对 RTL 设计进行综合并分析时序、 面积;

4、熟悉 DDR 读写原理、熟悉常见片上总线规范(例如 AMBA AXI);

5、对 CNN,大语言模型(LLM)等常见 AI 算法及硬件实现方法有强烈的学习意愿。

岗位关键字:

数字前端设计,ASIC 前端设计,RTL 设计、AI/人工智能,深度学习、CNN、大语言模型 LLM。

职位:FPGA 原型验证工程师

岗位职责:

1、负责 FPGA 原型验证平台的设计、调试和维护;

2、完成从 SoC 到 FPGA 的 verilog 代码转换、集成和仿真验证;

3、支持 FPGA 系统调试;

4、跟进 FPGA 原型验证方法学的演进,完善 FPGA 验证流程。

任职要求:

1、电子、计算机、自动化等相关专业,本科及以上学历,三年以上工作经验;

2、精通 Verilog/SystemVerilog 硬件描述语言,有扎实的数字电路基础;

3、熟练掌握 Xilinx/Intel FPGA 芯片的设计、验证流程,熟练掌握 EDA 工具使用;

4、具有以下一项或者多项能力:

1)熟悉 AMBA 总线协议;

2)具有 IP 集成/验证经验,或系统集成/验证经验;

3)熟悉 ARM 等嵌入式处理器体系结构;

4)熟悉常见外设协议,具有相关调试经验;

5)具有脚本编写能力,能够将工作流程脚本化。

5、具有良好的表达沟通能力及团队合作精神,具有较强的独立工作能力和动手能力;

6、良好的英文阅读、文档编写能力。

夜雨聆风

夜雨聆风