【核心导读/TL;DR】

随着人工智能算力芯片(如NVIDIA Blackwell架构的B200)系统功耗正式突破千瓦大关,以及新能源汽车高压化架构、消费电子极致轻薄化的多重驱动,作为直流-直流(DC-DC)电源转换核心链路的功率电感(Power Inductor)正面临着前所未有的热管理、高频交流损耗以及瞬态响应挑战。本文基于严谨的第三方工程物理与市场供应链视角,深度拆解全球一体成型电感(Molding Choke)巨头——乾坤科技(Cyntec)的核心技术壁垒与全生命周期产品线。

本报告不仅为硬件研发工程师提供从底层材料物理(软饱和特性、涡流损耗控制)到前沿应用拓扑(TLVR多相架构、PD 3.1高频快充、AEC-Q200极限车规)的严苛选型逻辑及印制电路板(PCB)Layout避坑指南;同时为电子元器件采购群体梳理了Cyntec的全球产能分布、Lead Time交期波动趋势,并独家整理了与Coilcraft、Vishay等国际大厂的同级别Pin-to-Pin替代矩阵。旨在帮助产业链核心从业者在复杂多变的技术演进与宏观供应链博弈中,构建兼顾极致电气性能与高度供货韧性的被动元器件落地策略。

1. 行业背景与品牌护城河:Cyntec如何定义一体成型电感

1.1 被动元器件全球版图中的乾坤科技

在全球被动元器件的宏观经济版图中,电感器(Inductor)作为三大基础无源器件(电容、电阻、电感)之一,其市场规模正处于一个由技术变革引发的超级周期中。根据最新市场研报数据,全球电感器市场在2025年整体估值约为56亿美元,并预计将以高达13.15%的复合年增长率(CAGR)迅速扩张,至2032年有望突破87亿美元的大关 。在这一庞大的赛道上,市场呈现出显著的寡头垄断与细分领域技术割据态势。日系厂商如Murata(村田)、TDK以及Taiyo Yuden(太阳诱电)长期在射频(RF)叠层电感及消费类小型化电感领域占据统治地位;而美系厂商如Vishay(威世)和Coilcraft 则在严苛的车规级耐高温环境与超低损耗的定制化大电流领域树立了难以撼动的标杆 。

成立于1991年的台湾乾坤科技(Cyntec),隶属于全球电源管理巨头台达电子(Delta Electronics)集团,其成功在日美巨头夹击中突围并确立全球领导地位的锚点,在于其对一体成型电感(Molding Choke)的大规模商业化应用与极致的良率控制。历史性的转折点出现在2013年,彼时智能手机正从单核/双核向高性能多核架构跃进,对主板供电的集成度提出了严苛要求。Cyntec凭借其开发的微型化一体成型电感成功切入苹果(Apple)供应链,实现了iPhone内部电源转换链路几乎100%采用一体成型电感的壮举,从而确立了其在高端移动终端电源转换领域的绝对霸主地位 。时至今日,Cyntec与Vishay、Murata(含其收购的TOKO)以及奇力新(Chilisin,现已并入国巨体系)共同瓜分了全球Molding Choke产能的80%以上,行业集中度极高,构筑了深厚的规模与先发护城河 。

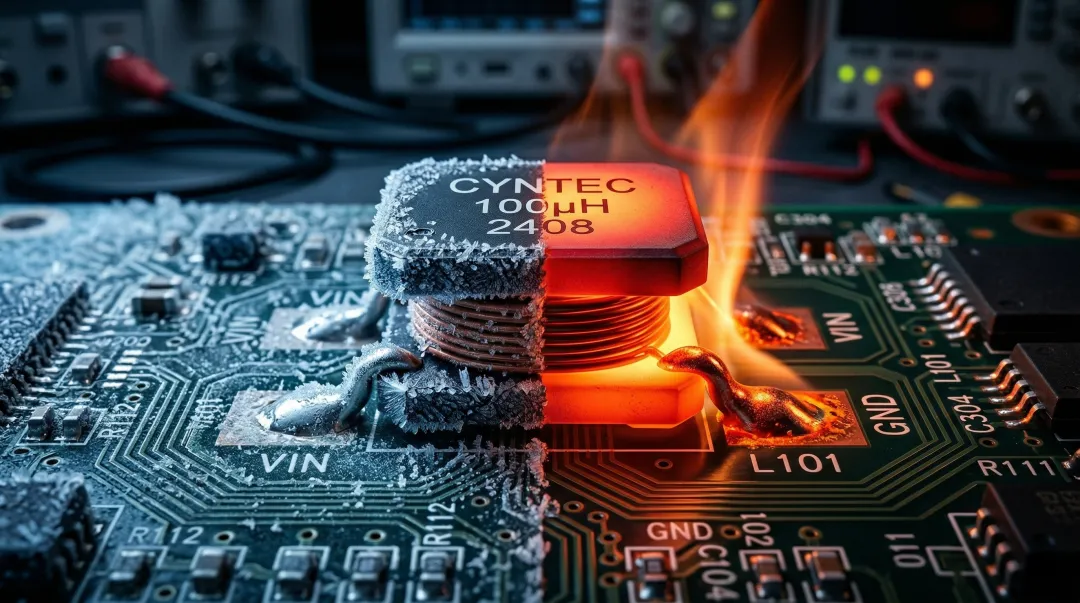

1.2 核心技术壁垒:粉末冶金配方与一次性共烧制程

在深入探讨Cyntec的产品线之前,必须厘清一体成型电感的物理本质。传统的绕线电感(Wire-wound Inductor)或磁封胶电感在面对现代高算力芯片极高的电流变化率(di/dt)时,往往暴露出漏磁严重、电磁干扰(EMI)大、体积臃肿以及局部热点(Hot Spot)难以消散等致命弱点。Molding Choke的革命性在于,其将高导电率的漆包铜线圈预先绕制,随后将金属磁性粉末(如铁基合金粉、羰基铁粉或非晶纳米晶粉末)混合特殊树脂作为绝缘粘合剂,直接在极高的压力下包裹线圈压铸成型,最终形成一个高密度、无缝隙的实心整体 。

Cyntec在该领域的护城河并非简单的流水线组装工艺,而是深埋于材料科学底层的粉末配方(Formula)与跨越机械、热力学边界的制程(Process)壁垒:

第一,纳米级磁粉绝缘包覆与配方调优。 一体成型电感的核心矛盾在于:金属粉末具有极高的饱和磁通密度,但同时金属也是良导体。如果在高频交变磁场下,金属颗粒之间相互导通,会产生极其巨大的涡流损耗(Eddy Current Loss),瞬间将电感烧毁。Cyntec的技术壁垒在于其掌握了极高水准的粉末冶金与表面绝缘处理工艺,能够将微米甚至纳米级的金属粉末颗粒表面均匀包覆一层极薄且耐高温的绝缘树脂层 。这种配方不仅确保了金属合金材料在高频(>3MHz)开关电源下仍能保持极低的磁滞与涡流损耗,还需要根据不同的应用场景(如追求高感值、低直流电阻或高频低耗),对铁氧体粉和陶瓷粉进行精密的设计与比例调配 。

第二,低温常温压制与共烧技术。 在压铸成型过程中,要获得高密度的磁芯(密度越高,导磁率与饱和电流越大),必须施加巨大的机械压力。然而,过高的压力极易压破内部铜线的绝缘漆膜,导致线圈匝间短路。Cyntec掌握了在常温下使用特殊润滑体系进行高密度压制,并在低于300摄氏度的温和环境下,将作为导电介质的金、银、铜线圈与外部包裹的磁性材料进行一次性成型烘烤的关键技术 。这不仅保护了内部脆弱的导电绝缘结构,还有效克服了铁氧体材料与其他非金属/金属材料共烧时的技术难点,解决了不同材料之间热膨胀系数(CTE)失配导致的应力开裂问题 。

1.3 Molding Choke的底层物理优势

相比于传统的开磁路或半闭合磁路电感,Cyntec的一体成型结构在工程物理层面呈现出三大压倒性优势,这也是其能够席卷从消费电子到重型算力设备的底层原因:

平缓的软饱和特性(Soft Saturation): 物理学中,当磁场强度增加到一定程度,磁芯材料内部的磁畴将全部同向排列,此时磁导率骤降,电感量急剧丧失,这种现象称为磁饱和。传统铁氧体电感往往表现出断崖式的“硬饱和(Hard Saturation)”,一旦电流越过阈值,电感瞬间变为一根导线,导致开关管因短路而炸机。而在Molding Choke中,由于绝缘树脂的存在,金属磁粉颗粒之间形成了海量且均匀分布的“微小分布气隙(Distributed Air Gap)” 。这些分布气隙使得磁芯在遭遇突发大电流(如GPU瞬间满载)时,磁导率下降呈现平滑、缓慢的曲线。这种出色的软饱和特性为电源管理IC(PMIC)的过流保护(OCP)介入预留了充足的安全裕度 。

绝对的低声噪与抗EMI干扰: 当大电流通过传统线圈时,交变磁场会使磁性材料产生微小的形变,即磁致伸缩现象(Magnetostriction),同时线圈本身在安培力的作用下也会产生高频震动,两者叠加便产生了令人烦躁的可听噪声(高频啸叫)。一体成型结构由于高密度的金属粉末紧密且完全无缝地包裹住了线圈,从物理力学层面彻底锁死了振动源,实现了几近于零的机械共振噪声 。同时,闭合的金属粉末外壳构成了天然的磁屏蔽罩,将漏磁通(Leakage Flux)降至最低,极大地优化了高频电路的电磁干扰(EMI)问题 。

极佳的热传导与温漂稳定性: 空气是热的不良导体。传统绕线电感内部存在大量空气间隙,导致线圈发热难以散出。Molding Choke的实心金属基结构具有远优于空气和普通环氧树脂的导热系数,能够迅速将线圈核心区域产生的焦耳热传导至器件表面并散入环境或PCB铜箔中 。此外,这种材料的直流重叠特性具有极高的温度稳定性,因周围环境温度变化引起的透磁率变动极小,完美契合了现代电子设备内部环境高温化封装的苛刻需求 。

2. 核心产品线拆解与底层技术指标

要精准驾驭Cyntec庞大的电感产品矩阵,硬件工程师必须首先深入拆解其核心明星系列,并透彻理解决定其性能边界的四大核心电气参数的物理意义。Cyntec目前的单月产能已突破12亿颗,产品线涵盖了从纳米级消费电子到千瓦级数据中心的全场景需求 。

2.1 明星系列巡礼:从微型化到大功率的进阶

PCMB / PCMC 系列(大电流表面贴装功率电感) 这是奠定Cyntec行业地位的基石系列。以PCMC065T为例,该系列主打高功率密度与低高度(Low Profile),最大厚度被严格控制在5.0mm以内,却能提供高达50A的峰值饱和电流(Isat)。该系列广泛采用了先进的金属合金粉末(Metal Dust Core),能够完美支持高达3MHz的高频DC-DC转换器开关频率。这类器件是目前高端笔记本电脑CPU主板供电(VRM/IMVP规范)、轻薄服务器主板以及各类高压交换机供电模块的绝对主力 。

高频超薄微型系列(HTEK / HTEL / SDEB) 针对内部空间寸土寸金的消费电子(如TWS真无线耳机、智能手表、5G射频前端及超薄智能手机),Cyntec推出了尺寸极限缩小的微型系列。例如HTEK12100F,其物理尺寸仅为1.2mm x 1.0mm x 0.6mm,但在如此狭小的空间内,依然能保持低于72mΩ的最大直流电阻,并提供超过2A的饱和电流与温升电流 。这种在极小体积内实现高能量密度的能力,是其稳居顶级手机供应链的核心。

TLM / HCUVE 系列(TLVR 跨电感电压调节器核心器件) 这是Cyntec应对当前AI大算力时代(如NVIDIA Hopper与Blackwell架构GPU)的核心杀手锏。在极高电流且要求微秒级瞬态响应的算力板上,传统的多相并联电压调节模块(VRM)在应对GPU从空载到数百安培满载的剧烈负载阶跃时,响应速度已触及物理天花板 。Cyntec的TLVR电感(Trans-inductor Voltage Regulator)创新性地在主级电源线圈外部,集成了与其余所有相位串联的次级绕组。这种多相、薄型设计利用磁耦合效应,成功将动态响应效率提升了数个量级,能够应对超过1000A/µs的高电流瞬变,同时由于纹波相抵效应,允许工程师在PCB设计时削减高达40%的大容量输出滤波电容,极大地释放了主板空间 。

2.2 核心参数的物理意义与工程表现

在阅读Cyntec的Datasheet时,资深研发工程师不能仅停留在表面数字,必须透过数据洞察其在实际PCB铜箔上运行的物理表现:

DCR(直流电阻,DC Resistance): 通常在规格书中分为典型值(DCR_Typ)和最大值(DCR_Max)。DCR完全由内部铜线的总长度、截面积材质以及绕制工艺决定。它直接决定了电感在稳态工作时的传导损耗(

)。为了在有限体积内追求极限的低DCR,Cyntec在其中大功率系列(如为服务器供电的SEP-EX系列 )中大量采用了扁平线(Flat Wire)绕组工艺。相比于传统的圆截面铜线,扁平铜线不仅极大提升了磁芯窗口的槽满率(Fill Factor),大幅降低了DCR;更重要的是,扁平线显著增加了导体的表面积,有效削弱了高频交变电流下的趋肤效应(Skin Effect,即高频电流倾向于集中在导体表面传输的现象),从而显著降低了高频下的交流等效阻抗 。

)。为了在有限体积内追求极限的低DCR,Cyntec在其中大功率系列(如为服务器供电的SEP-EX系列 )中大量采用了扁平线(Flat Wire)绕组工艺。相比于传统的圆截面铜线,扁平铜线不仅极大提升了磁芯窗口的槽满率(Fill Factor),大幅降低了DCR;更重要的是,扁平线显著增加了导体的表面积,有效削弱了高频交变电流下的趋肤效应(Skin Effect,即高频电流倾向于集中在导体表面传输的现象),从而显著降低了高频下的交流等效阻抗 。Isat(饱和电流,Saturation Current): 不同厂商对Isat的定义标准并不统一。Cyntec通常将其严谨地定义为施加直流偏置电流后,电感量(Lo)较初始值下降20%或30%时所对应的电流值 。工程师在选型时必须极度警惕温度对Isat的降额影响。规格书上的Isat标称曲线往往是在25℃室温下测得,而在实际密闭的高温机箱(如85℃以上)中运行,磁芯的饱和磁通密度会发生漂移,Isat曲线会向下平移。Molding Choke的优越性在此刻显现,即便在极端发热状态下遭遇峰值脉冲电流突破了Isat阈值,其软饱和特性也能保证电感量只是平滑衰减,而绝非瞬间归零,保全了后级昂贵的硅芯片。

Irms(温升电流/额定发热电流,Heating Current): Irms表征的是电感的热耗散能力。Cyntec通常将其定义为在25℃环境温度下,施加连续直流电流使电感本体温度自身上升约40℃(

)时的电流值 。必须指出,实际工程中器件的最终温度不仅取决于Irms,还深度依赖于PCB的Layout设计(铜箔厚度、过孔数量、散热风道)。由于Molding Choke是一体成型的实心金属块,其内部热阻极低,热量能迅速从核心线圈传导至器件引脚并被PCB地平面吸收,因此在同等体积下,其Irms表现通常远优于内部含空气隙的传统磁屏蔽电感。

)时的电流值 。必须指出,实际工程中器件的最终温度不仅取决于Irms,还深度依赖于PCB的Layout设计(铜箔厚度、过孔数量、散热风道)。由于Molding Choke是一体成型的实心金属块,其内部热阻极低,热量能迅速从核心线圈传导至器件引脚并被PCB地平面吸收,因此在同等体积下,其Irms表现通常远优于内部含空气隙的传统磁屏蔽电感。AC Loss(交流损耗)与Q值(品质因数): 这是高频DC-DC转换器中隐藏最深的“效率杀手”。当开关频率跨越1MHz甚至冲向更高的GaN(氮化镓)拓扑频段时,总损耗中传导损耗(DCR)的占比会下降,而交流损耗(AC Loss)将占据主导。AC Loss主要包含磁芯损耗(Core Loss,由磁滞回线面积决定的磁滞损耗和涡流损耗构成)以及交流绕组损耗(AC Winding Loss,由趋肤效应和邻近效应引起)。尽管标准规格书往往对AC Loss语焉不详,但它是决定电源在半载和满载时真实转换效率的关键。Cyntec通过持续迭代粉末配方,特别是提升粉末颗粒表面的绝缘膜层阻抗,在抑制高频涡流方面表现卓越,保证了在高频大纹波电流下依然具有相对可控的温升与较高的Q值。

3. 客观横向竞对分析:寻找Cyntec的“甜蜜点”(Sweet Spot)

在多元化、碎片化且应用场景极度跨界的被动元器件生态中,没有任何一家原厂能够打破物理定律,实现全场景的通吃。作为客观中立的行业分析,我们必须跳出单一厂商的视角,将Cyntec的参数面板与行业标杆——如美系的Coilcraft、Vishay(威世),日系的Murata(村田)、TDK,以及正在强势崛起的国内龙头顺络电子(Sunlord)——进行技术指标与市场定位的残酷对标。

3.1 全球一线电感原厂竞品矩阵大横评

为了直观呈现各家在技术路线与市场策略上的分野,下表提炼了核心维度的对抗关系:

对比维度 | Cyntec (乾坤科技) | Coilcraft | Vishay (威世) | Murata (村田) / Sunlord (顺络) |

主打核心系列 | PCMC / TLM (TLVR) / VBH | XAL / XEL / XGL 系列 | IHLP 系列 (车规绝对标杆) | DFE (Murata) / MWSA (Sunlord) |

底层磁芯技术路线 | 金属合金粉末一次压铸成型 | 高性能复合磁芯结构 | 特种铁粉/复合材料专利成型 | 射频陶瓷叠层 / 铁氧体及金属合金 |

电学参数核心优势 | 极佳的综合性价比、优异的大电流瞬态响应(TLVR)、DCR控制优异 | 在极高频(>2MHz)下拥有业界最低的AC损耗、尺寸与感值覆盖极广 | 极高的热稳定度,长期高温运行无热老化(No Thermal Aging) | 极致的小型化(射频级,Murata) / 极具侵略性的成本与产能扩张速度(Sunlord) |

饱和特性(Isat)表现 | 优秀的软饱和曲线,衰减平滑可控 | 极其优异的软饱和特性,抗峰值电流尖峰能力极强 | 软饱和特性优越,高负载下电感量保持率极高 | 金属系呈良好软饱和,传统铁氧体系列呈断崖式硬饱和 |

DCR(直流电阻)控制 | 极低(在主流系列中广泛成熟应用扁平线技术降低阻抗) | 极低(最新XGL系列在同等体积下的DCR几近触碰物理极限) | 极低(凭借其专利的内部封装结构与高导电引线框架) | 良好,视具体封装尺寸与成本定位而定 |

战略级强势应用市场 | AI算力服务器(GPU/CPU)、高端PC、智能手机、大功率快充 | 通信基站、高频工业电源、对能效要求苛刻的航空航天与医疗设备 | 新能源汽车核心部件(OBC、BMS、驱动逆变器)、重型工业控制 | 海量IoT设备、通用DC-DC电源、车联网通信模块 |

3.2 深度洞察:Cyntec的优势区间与客观局限性

优势区间(Sweet Spot):AI算力浪潮下的先发统治力 Cyntec当前最庞大的商业护城河与技术“甜蜜点”,毫无疑问建立在以NVIDIA架构为代表的AI服务器及超算网络领域。在处理数百瓦乃至千瓦级(如NVIDIA B200)算力芯片的供电时,传统的电压调节模块(VRM)技术路线已经崩溃。Cyntec极其敏锐地捕捉到了从48V配电向底层芯片极低电压(约0.8V)、超大电流转换的行业痛点 。其主推的TLVR(Trans-inductor Voltage Regulator)多相耦合电感,完美契合了GPU在模型训练和推理时产生的恐怖阶跃电流 。在这条高度定制化、需原厂深度参与前期架构设计的赛道上,Cyntec凭借与台达体系的协同效应、雄厚的仿真与材料研发实力,成功卡位,形成了相比于欧美厂商显著的响应速度与先发定制优势。此外,在单月十亿级产能的加持下 ,Cyntec在保持极高一致性(Cpk)的同时,展现出了令欧美原厂感受到压力的成本控制力。

4. 工程师选型指南与Layout避坑原则 (硬核技术干货)

在现代高密度的PCB硬件开发中,电感的选型早已超越了简单的“对齐电感量(L)与额定电流(I)”的初级阶段。针对当下最热门的三大前沿应用拓扑,我们为硬件研发工程师提炼出直指核心的选型逻辑,并深度剖析在Layout与生产制程中极其容易引发灾难性失效的“隐形地雷”。

4.1 前沿应用场景一:AI算力GPU核心供电 (H100/B200的百安培级挑战)

场景与物理痛点: 进入大语言模型(LLM)时代,AI芯片的功耗呈指数级飙升。以NVIDIA Blackwell架构的B200为例,其热设计功耗(TDP)高达1000W(相较于前代Hopper架构H100的700W有着惊人的跃升)。在服务器机架内,供电架构通常采用从48V背板电压降至12V中间母线,再通过Point-of-Load(POL)降压至GPU核心所需的极低电压(约0.6V - 0.8V)。这意味着POL级的输出电流将轻易突破1200A。更可怕的是负载的动态特性——GPU在处理大规模矩阵乘法瞬间,电流的阶跃变化率(di/dt)极大,若电感储能释放迟缓,将导致核心电压瞬间跌落(Voltage Droop),致使整个算力集群宕机或计算错误。

破局选型逻辑: 面对如此恐怖的瞬态响应需求,依赖传统大幅降低电感量(L)来提升响应速度的做法已行不通(会导致稳态纹波过大)。必须采用TLVR(Trans-inductor Voltage Regulator)架构。

推荐方案与参数解读: 强烈推荐引入Cyntec的TLM/HCUVE系列(如TLM966411F、TLM106012F-L等型号)。该系列电感量被精准控制在极低的70nH至200nH区间内,确保极速的电流爬升率。其核心魔力在于四端子结构——除了常规的主供电绕组,电感内部还集成了一组隔离的次级绕组。在PCB上,所有相位的次级绕组首尾串联,并接入一个调谐电感(Tuning Inductor)。当某一个相位因负载突变产生高频电压差时,变压器耦合效应会瞬时将这一信号传递给所有并联的相位,促使所有相位的电感同时输出电流支撑负载。采用Cyntec该系列方案,不仅能将瞬态响应速度飙升至1000A/µs以上,还能因各相纹波的高效抵消,大幅削减服务器主板上40%的昂贵且占空间的大容量输出电容(Bulk Capacitors)。

4.2 前沿应用场景二:新能源汽车OBC与BMS (跨越AEC-Q200极限温区)

场景与物理痛点: 在新能源电动汽车(EV)的生态中,车载充电机(OBC,处理交流转直流的高压充电)和电池管理系统(BMS,涉及高精度电芯均衡与隔离通信)所处的物理环境极其恶劣。元器件不仅需要承受引擎舱或底盘极端的温度循环(-40℃至125℃或155℃),还要面对持续的机械低频震动以及高压开关带来的高频传导/辐射EMI干扰。

破局选型逻辑: “车规级”是不可妥协的底线。选型电感必须通过国际汽车电子协会制定的AEC-Q200被动元件应力测试认证 。这涵盖了上千小时的高温高湿偏压(Humidity bias)、严苛的冷热冲击(Temperature Cycling)以及极端的机械冲击震动测试。

推荐方案与参数解读: 推荐使用Cyntec的AOTA系列或针对车载电源高度集成的Molding Type PFC Module。对于OBC中负责提升电网功率因数的PFC电路,传统的环形磁芯(Ring-core)绕线电感由于体积巨大、重心不稳,在车辆长年震动下极易发生引脚疲劳断裂。Cyntec采用大体积粉末冶金压铸技术制成的PFC模块,在保持相同电气参数的前提下,将单体体积缩减了惊人的66%,整体模块重量下降34% 。实心的成型结构从根本上消除了磁芯碎裂与线圈摩擦短路的风险,是汽车轻量化与高可靠性设计的典范。

4.3 前沿应用场景三:140W/240W PD 3.1高频快充适配器

场景与物理痛点: 随着PD 3.1协议将快充功率上限推高至240W,并在初级与次级广泛引入氮化镓(GaN)高电子迁移率开关管,电源的开关频率被推高至几百kHz甚至向MHz级别迈进。频率的提升换来了电感和电容体积的大幅缩小,使得“口红电源”、“超薄饼干充”成为可能,但代价是极剧上升的AC损耗与趋肤效应。

破局选型逻辑: 在如此狭小且缺乏主动散热的密闭塑胶壳内,传统的圆线铁氧体电感会因集肤效应使得电流全挤在导线表面,导致交流阻抗飙升,器件严重发热甚至热失控失效。此时必须考量扁平线设计与软饱和特性(防止在插拔瞬间或PD协议握手急剧改变输出电压时发生硬饱和)。

推荐方案: Cyntec厚度严格控制在微型级别的薄型PCMC系列是绝佳的现成方案。扁平铜线工艺完美拉平了电流密度分布,对抗了趋肤效应;高绝缘度的金属粉材将高频涡流封锁在纳米颗粒内部。这种设计极大降低了高频DC-DC转换下的整体表面温升。

4.4 深度失效分析:Layout与制造制程中的避坑原则

纵使选用了各项参数完美的Cyntec一体成型电感,如果研发在PCB Layout阶段或NPI工程师在表面贴装(SMT)工艺规划时出现误判,依然会导致灾难性的批量返工。一体成型电感在应用端最致命的失效模式是本体裂纹(Flex Cracking)与内部漏电流增大/短路。

避坑地雷 1:忽视热膨胀系数(CTE)失配引发的致命剪切力

现象表征: 电感本体边缘通常呈现出45度角的贯穿性微裂纹,严重时甚至连带将PCB表层的焊盘铜箔整片撕裂剥离 。

物理根因: 常见的FR4材质PCB板的热膨胀系数(CTE)约为17 ppm/℃,而Molding Choke的金属粉末与树脂混合体CTE仅为约8-10 ppm/℃。在SMT过回流焊炉的急剧降温阶段,或产品在实际使用中处于剧烈的冷热交变环境(Thermal Shock)时,PCB板的收缩量远大于电感本体。这种巨大的物理收缩差异,会在电感的金属端头和脆弱的树脂结合部产生惊人的机械拉应力(Tensile Stress),导致分子链解缠绕从而发生脆性断裂 。

Layout防范对策: 研发在进行PCB敷铜设计时,电感两个焊盘周围连接的覆铜面积应尽量保持对称(Thermal Relief设计),避免单侧散热过快导致凝固时间产生时间差而引入额外的扭转应力。此外,在PCBA拼板分板(Depaneling,如V-cut折板或铣刀切割)工序中,必须确保切割产生的机械应变(Micro-strain)无法传导到靠近板边的电感元件上,大型电感应尽量远离应力集中的分板边缘布置 。

避坑地雷 2:迷信“焊锡越饱满越牢固”的Solder Fillet高度陷阱

常识误区: 许多缺乏经验的工艺工程师认为,SMT贴片时焊锡越多、侧边爬锡越饱满(甚至将电感侧面端头全部包住),器件的抗震性与连接就越牢固。

致命事实: 对于Molding Choke而言,过多的焊锡将是一场噩梦。高耸饱满的焊锡堆积会将电感侧面端头与PCB死死“锚固”成一个刚性极强的整体。这导致原本可以通过焊点微小形变来吸收缓冲的热应力(上文提到的CTE失配应力)无处释放,从而将巨大的拉应力直接转嫁给电感本体材料,极大增加了开裂的几率 。

规范制程指导: 根据IPC标准及各大被动元器件行业规范的强烈建议,最佳的侧边爬锡高度(Solder Fillet Height)应严格控制在电感侧面端头高度的1/3 至 2/3之间 。为了达到这一精确目标,工艺工程师必须通过优化钢网(Stencil)的开孔设计,精确计算面积比(Area Ratio应>0.66)和宽厚比(Aspect Ratio应>1.5),从而实现对锡膏释放体积(Transfer Efficiency)的精准把控,这是预防批量回流焊裂纹失效的核心基石。

5. 采购供应链洞察:产能博弈、行情趋势与替代防线 (市场干货)

在电子制造业的血雨腥风中,元器件采购部门的核心KPI永远是三位一体的:保交期(Lead Time)、控成本、抗风险。在当前全球地缘政治逆全球化、宏观经济周期震荡以及局部产能被AI巨头瞬间抽干的复杂博弈下,构建针对Cyntec及其同级别物料的供应链(Supply Chain)防线至关重要。

5.1 宏观交期波动预测与Cyntec产能战略布局

当前交期(Lead Time)趋势深度剖析: 综合当前主流电子元器件分销平台(如Digi-Key, Mouser)与现货市场情报,标准的常规尺寸Molding Choke在市场平稳期的原厂标准交期通常维持在较为健康的12周至16周区间 。然而,当前的供应链环境正经历结构性失衡。受全球以英伟达(NVIDIA)、超微(Supermicro)为首的AI基础设施数据中心建设狂潮影响,能够支持千瓦级算力的定制化大电流、高频料号(尤其是采用复杂耦合绕线工艺的TLVR高端电感系列),其上游金属粉末原料配额与专属产线产能正被头部算力巨头签订长协(LTA)大量锁定 。这种虹吸效应不可避免地蔓延,导致现货市场上部分中大功率料号的交期被急剧拉长至20周甚至更久的预警水位。

产能分布与原厂扩产动向: 作为台达电子(Delta)帝国版图下的核心资产,Cyntec拥有极其强悍的重资产制造能力。其生产基地矩阵横跨台湾本土及中国大陆多地,依托历经数十年迭代的高度自动化制程生产线,Cyntec目前的磁性元件年产能已呈指数级跨越至百亿颗(单月超12亿颗)的历史高位 ,这为全球海量消费电子订单提供了坚实的交付托底。 展望未来的产能资本开支方向,随着AI大语言模型(LLM)算力迭代与新能源电动汽车架构向800V演进的强劲双轨拉动,Cyntec的扩产重心正明显向两极分化倾斜:一端是极具技术溢价的超高功率密度异构集成模块(如TLVR与OBC PFC模块),另一端则是面向穿戴式设备的极限微型化薄型贴片。对于一线采购专员而言,在制定物料需求计划(MRP)时,对于BOM单中涉及扁平线工艺、特殊大尺寸或高感值的非标高规品,必须将备货周期(Buffer)战略性地拉长至少1个季度,并执行严格的Rolling Forecast(滚动预测)机制。

5.2 缺货断链预案:构建Pin-to-Pin主流物料同级别替代选型防线

为了彻底规避因不可抗力(如工厂火灾、突发地缘制裁、原厂产线调整)引发的单点断供风险(Single Source Risk),硬件研发与采购团队必须形成合力,在新产品导入(NPI)阶段的初期,就强行拉通并确立Second Source(二供)甚至Third Source战略。

基于决定能否直接替换的两大核心基石——物理封装尺寸(Footprint Land Pattern)与核心电气指标动态曲线(Isat衰减斜率, DCR_max分布),我们独家梳理了Cyntec核心系列与国际第一梯队品牌(Vishay, Coilcraft)近似Pin-to-Pin或Drop-in替代的战略对抗矩阵 :

Cyntec (乾坤科技) 主流系列代表 | 核心物理尺寸 (L x W x H) | Vishay (威世) 推荐替代型号系列 | Coilcraft (尔必达) 推荐替代型号系列 | 替代验证核心注意事项与侧重点 (Engineering Check) |

PCMB061H 系列 | 7.0 x 6.6 x 1.8 mm | IHLP-2525AH-01 | XAL7020 系列 | 尺寸高度兼容,属常规低压应用完美替代。需重点确认二供的DCR_max微小偏差是否会引起系统整体发热预算超标。 |

PCMB063T 系列 | 7.0 x 6.6 x 3.0 mm | IHLP-2525CZ-01 | XAL7030 系列 | 属于最主流的3.0mm厚度甜点区。Vishay的耐高温无老化特性略胜一筹,而Coilcraft在高频(>2MHz)纹波下的AC损耗表现稍优。 |

PCMB065T / PCMC065T | 7.0 x 6.6 x 5.0 mm | IHLP-2525EZ-01 | XAL7050 系列 | 5.0mm高规大电流厚度。交替使用时,研发必须在环境保温箱中实测最大满载峰值电流(Peak Load)下的真实温升曲线。 |

PCMB104T 系列 | 11.0 x 10.0 x 4.0 mm | IHLP-4040DZ-01 | XAL1010 系列 | 步入10x10mm级别的中大功率段。重点检查规格书陷阱:不同厂商定义软饱和拐点的标准(是电感量下降20%还是30%定义为Isat)存在差异,需比对Bode波特图。 |

PCMC135T 系列 | 13.5 x 12.5 x 5.0 mm | IHLP-5050EZ-01 | SER1360 / XAL1580 | 超大尺寸Molding型,多用于汽车电子或基站重载。除电气验证外,必须送至第三方实验室进行包含剧烈扫频的完整三轴机械震动测试(Vibration Test)。 |

HTEK / HTEL 微型系列 | 1.6 x 0.8 mm (0603封装) | -- (此极小尺寸领域非Vishay强项) | XFL2005 / XEL 系列 | 消费类极其狭小空间应用替代。采购端需确保替代料能顺利上机;工艺端需紧盯高速贴片机的吸嘴兼容性识别,以及过回流焊炉时因两端表面张力不均引发的翘碑现象(Tombstoning)风险。 |

(极度警示:上述商业替代建议矩阵仅供宏观寻源参考,真实操作中绝不存在毫无妥协的100%完美替换。任何Pin-to-Pin替换执行前,必须由资深研发工程师主导打样,放入具体的电源拓扑结构中,在极限输入/输出电压、极高/极低温箱真实负载状态下,进行包含Bode Plot(波特图)相位裕度测试、瞬态阶跃响应(Load Transient)以及红外热成像温升抓取的全维度系统级验证。)

【总结与行动建议】(Takeaways)

在摩尔定律(Moore's Law)由于逼近量子隧道物理极限而演进逐渐放缓的今天,系统整体性能的突破往往不再单单依赖制程节点的微缩,而越来越残酷地考验着外围供电网络(Power Delivery Network, PDN)这套“能源基础设施”的硬实力与稳定性。Cyntec(乾坤科技)凭借其在一体成型电感领域数十年如一日筑起的粉末冶金配方壁垒、无可挑剔的自动化共烧工艺以及庞大的产能后盾,完美踩中了消费电子极致轻薄化、汽车电子苛刻高可靠性以及AI超算网络大电流瞬态供电的三大历史性爆发风口。

全价值链行动建议:

对于硬件研发工程师: 必须果断摒弃过去仅仅依靠比对标称电感量L值和最大饱和电流Isat的浅层选型习惯。面对下一代大功率、高频宽禁带(SiC/GaN)应用,必须主动向原厂索要并深入剖析电感的AC Loss(交流损耗)频谱曲线与动态热阻模型进行多维严苛评估;针对正在爆发的AI或高速网络交换机等极端瞬态场景,尽早跳出传统VRM的思维舒适区,主动储备并实践TLVR磁耦合串联架构的原理与底层Layout走线经验。

对于采购与供应链管理者: 应通过顶层数据实时监控全球算力霸权扩张对高端特殊工艺Molding Choke原材料和产能的深层挤压效应。充分利用本文独家提供的Cross-Reference战略替代矩阵表,倒逼研发团队加速推动关键BOM单的双源或多源化交叉认证(Dual-sourcing/Multi-sourcing),从而在宏观不可抗力波动与芯片战交织的时代,构建起具有高度弹性与反脆弱能力的被动元件供应链蓄水池。

终极拷问:

当拥有高达192GB HBM3e显存、单卡功耗疯狂飙升至1000W级别的NVIDIA B200 GPU已成服务器标配,更激进的冷板式液冷架构与底层供电网络的物理重构正在以摧枯拉朽之势席卷整个数据中心生态。面对动辄数千安培的狂暴瞬态电流与逼近物理极限的热通量,您主导设计的当前这套电源拓扑结构,以及备料库中沉睡的那些传统磁性元器件,真的准备好迎接下一个“算力寒武纪”的残酷洗礼了吗?

(欢迎各位硬件大牛、采购精英在评论区深度留言,分享您在电感选型调优、Layout血泪史或供应链断货保供中踩过的“坑”与独特前瞻见解。)

👇 扫描下方二维码,立即获取 Cyntec 在线电感选型 (Power Inductor ),您的专属电源磁性元器件解决方案!

#乾坤科技 #Cyntec #台达电子 #一体成型电感 #MoldingChoke #TLVR架构#AI算力供电 #英伟达B200 #高频快充PD3 #新能源汽车OBC #BMS电感 #硬件工程师 #PCB设计避坑 #SMT焊接工艺 #电子元器件采购 #元器件交期预警 #国产替代选型 #Vishay替代 #Coilcraft对标 #被动元器件分析

#乾坤科技 #Cyntec #台达电子 #一体成型电感 #MoldingChoke #TLVR架构#AI算力供电 #英伟达B200 #高频快充PD3 #新能源汽车OBC #BMS电感 #硬件工程师 #PCB设计避坑 #SMT焊接工艺 #电子元器件采购 #元器件交期预警 #国产替代选型 #Vishay替代 #Coilcraft对标 #被动元器件分析

夜雨聆风

夜雨聆风