随着大语言模型参数规模从十亿级跃升至万亿级,AI计算需求呈现出爆发式增长。在这个背景下,计算架构不再由单一品类主导,而是形成了GPU、TPU、APU、NPU等多种架构并存的局面。

GPU:通用计算的基石与生态霸主

图形处理器(GPU)最初为图形渲染设计,但凭借其大规模并行计算能力,已成为当前AI领域的事实标准。

技术核心:GPU采用SIMT(单指令多线程)执行模型,以NVIDIA的Streaming Multiprocessor(SM)为基本计算单元。每个SM包含CUDA Core(基础计算单元)和Tensor Core(矩阵加速单元)。以最新Blackwell架构为例,其Tensor Core已演进至第五代,支持FP4精度计算,并在Hopper架构中引入了Transformer Engine,可动态管理混合精度计算。

内存架构:现代AI GPU采用分层存储体系。以H100为例,寄存器提供数十TB/s的极限带宽但容量仅256KB/SM;L1缓存/共享内存容量256KB/SM,带宽约10TB/s;L2缓存60MB,带宽5TB/s;外部HBM3容量80GB,带宽3.35TB/s。这种层次结构通过数据局部性优化,缓解了"内存墙"问题。

生态壁垒:CUDA生态经过20年积累,形成了深厚的软件护城河。PyTorch、TensorFlow等主流框架对CUDA支持最为完善,这也是其他架构难以撼动GPU地位的核心原因。

技术实现细节

核心架构:Streaming Multiprocessor (SM)

CUDA Core:基础FP32/INT32计算单元,每个SM含128-256个

Tensor Core:专用矩阵乘加单元(4×4×4 FMA),支持FP16/BF16/INT8/FP8/FP4

RT Core:光追加速单元(Turing及以后),处理BVH遍历和光线-三角形相交测试

Warp调度器:32线程为一组(Warp),单指令多线程(SIMT)执行

内存层次(以H100为例)

关键技术

NVLink:芯片间高速互联(Hopper达900GB/s双向)

Transformer Engine:Hopper引入,动态管理FP8精度

MIG(Multi-Instance GPU):Ampere起支持,单卡虚拟化成7个独立实例

技术发展迭代

| Tesla | ||||

| Fermi | ||||

| Kepler | ||||

| Maxwell | ||||

| Pascal | ||||

| Volta | 第一代Tensor Core | |||

| Turing | RT Core光追 | |||

| Ampere | ||||

| Hopper | ||||

| Blackwell |

TPU:谷歌的云端AI专用武器

张量处理器(TPU)由谷歌自研,代表了ASIC(专用集成电路)路线在AI领域的成功实践。

架构特色:TPU的核心是脉动阵列(Systolic Array)——一种二维矩阵计算结构,数据从阵列一端流入,在流动过程中完成乘加运算,结果从另一端流出。这种设计最大化数据复用,减少了内存访问次数。TPU v4包含65536个MAC(乘加单元),峰值算力达275 TFLOPS(BF16)。

内存与扩展:TPU采用HBM2/3作为外部存储,配合28MB片上SRAM。其最大优势在于集群扩展能力,TPU Pod可通过3D Torus网络连接数千颗芯片,形成超大规模训练集群(v5p Pod可达8960芯片)。

适用边界:TPU与TensorFlow/JAX深度绑定,仅通过谷歌云提供服务。其架构针对Transformer类模型优化,但对于非规则计算或需要频繁分支的场景效率较低。

技术实现细节

架构设计

脉动阵列(Systolic Array):核心计算单元是65536个8-bit乘加单元,排列成256×256的二维阵列

数据流驱动:数据从一端流入,在阵列中流动计算,结果从另一端流出,最大化数据复用

专用矩阵乘法器:针对Transformer中的矩阵运算优化,不追求通用性

内存层次

关键参数(TPU v4)

BF16精度为主,支持INT8

峰值算力:约275 TFLOPS(BF16)

功耗:约200W

制程:7nm(v4)、5nm(v5)

技术发展迭代

| TPU v1 | ||

| TPU v2 | ||

| TPU v3 | ||

| TPU v4 | ||

| TPU v5e/v5p |

APU:异构融合的统一内存实践

加速处理器(APU)将CPU与GPU集成于单一芯片,代表了异构计算架构的重要分支。AMD的Ryzen AI系列与Apple的M系列是这一路线的代表。

统一内存架构:APU的核心创新在于统一内存架构(Unified Memory Architecture)。传统架构中,CPU使用DDR内存,GPU使用GDDR/HBM显存,数据需通过PCIe总线拷贝。而APU让CPU与GPU共享同一物理内存池(通常为LPDDR5X),实现零拷贝数据共享。以AMD Strix Halo为例,其提供128GB统一内存,带宽256GB/s;Apple M3 Ultra更达到819GB/s的惊人带宽。

技术权衡:统一内存消除了数据搬运开销,且容量可做得很大(最高512GB),适合大模型推理。但其带宽(256-819GB/s)仍低于高端独立GPU的HBM(3TB/s+),且CPU与GPU存在带宽竞争。此外,APU的GPU部分通常采用集成显卡架构(如RDNA 3.5),图形性能弱于独立显卡。

生态现状:APU需依赖ROCm(AMD)或Metal(Apple)生态,CUDA兼容性仍是短板。

技术实现细节

架构本质

CPU + GPU 异构集成:在同一硅片上集成通用处理器和图形处理器

共享内存控制器:CPU和GPU通过同一内存控制器访问系统内存

统一地址空间:CPU和GPU看到相同的虚拟地址,零拷贝数据共享

AMD Strix Halo(最新一代)细节

关键技术

Infinity Fabric:AMD的片内/片间互联总线,连接CPU、GPU、NPU

Smart Access Memory(SAM):CPU直接访问全部GPU内存,突破传统限制

Chiplet设计:CPU、GPU、I/O分别制造,通过先进封装集成

技术发展迭代

| 初代APU | |||

| GCN架构 | |||

| Zen+Vega | |||

| RDNA时代 | |||

| AI增强 |

NPU:端侧AI的能效比之王

神经网络处理器(NPU)专为低功耗AI推理设计,广泛部署于智能手机、轻薄笔记本及IoT设备。

架构特点:NPU通常包含专门的MAC阵列,针对INT8/INT4低精度计算优化,并支持稀疏计算(跳过零值运算)。以Apple Neural Engine为例,其采用16核设计,M4系列提供38 TOPS算力;高通Hexagon NPU则采用标量+向量+张量三单元异构设计。

技术演进:早期NPU(2017年左右)仅支持简单CNN推理;随着Transformer普及,现代NPU增加了对Attention机制的硬件支持,并引入KV Cache管理单元。Intel、AMD在PC处理器中集成的NPU(如Intel NPU 4.0、AMD XDNA 2)算力已突破40 TOPS,支撑本地大模型运行。

定位清晰:NPU追求极致能效比(每瓦算力),但绝对算力有限,且仅适合推理(Inference),无法承担训练(Training)任务。

技术实现细节

架构特点

专用MAC阵列:大量低精度(INT8/INT4)乘加单元

数据流优化:针对神经网络层间数据流动优化,减少内存访问

稀疏计算支持:跳过零值计算,提升效率

Apple Neural Engine(代表设计)

高通Hexagon NPU

标量+向量+张量三单元设计

标量单元:控制流、激活函数

向量单元:SIMD并行

张量单元:矩阵乘法加速

技术发展迭代

| 早期DSP | ||

| 专用NPU诞生 | ||

| 算力竞赛 | ||

| Transformer优化 | ||

| PC级NPU |

IPU与LPU:SRAM-only的极端路线

Graphcore的IPU和Groq的LPU代表了另一种架构哲学:摒弃外部DRAM,仅用片上SRAM。

技术实现:Groq LPU包含230MB片上SRAM,提供80TB/s的极端带宽和确定性延迟(无抖动)。其采用时序编译器(Temporal Compiler),在编译阶段即确定所有指令的执行时序,运行时无需缓存未命中等待。IPU则采用1216个独立核心(MIMD架构)和900MB片上SRAM,针对图计算优化。

能力边界:SRAM-only架构的致命限制在于容量——230MB仅能容纳小模型(如7B-13B参数)。对于大模型,需通过模型并行(Model Parallelism)将参数分布到多芯片,增加了系统复杂度。因此,这类架构目前主要服务于对延迟极度敏感的场景(如高频交易、实时对话)。

市场命运:Graphcore已于2024年被收购并停产,表明纯SRAM路线在商业上难以与GPU竞争;Groq则通过云服务模式(GroqCloud)继续探索LLM推理市场。

技术实现细节(Groq)

极致架构

张量流式处理器(TSP):不是传统SIMD,而是VLIW+数据流

SRAM-only设计:230MB片上SRAM,零外部DRAM

确定性执行:编译时确定所有时序,运行时无延迟波动

时序编译器:将模型编译成精确的指令时间表

关键参数(GroqChip)

系统级设计

GroqNode:4芯片,1TB/s互联

GroqRack:64芯片,支持70B模型

GroqCloud:云端API服务

技术发展迭代

| 初代芯片 | ||

| GroqChip | ||

| 大模型支持 | ||

| 下一代 |

FPGA与ASIC:灵活性与专用性的光谱两端

现场可编程门阵列(FPGA)和专用集成电路(ASIC)位于灵活性与效率的两个极端。

FPGA:通过可编程逻辑单元(LUT)和可配置互联,FPGA可在硬件层面实现任意数字电路。Xilinx Versal系列甚至集成了AI引擎(AIE),提供512个VLIW SIMD处理器。FPGA适合算法快速迭代期或小批量部署,但单位算力成本高于ASIC。

ASIC:当算法固化且需求量极大时,全定制ASIC可实现最优能效比。除TPU外,AWS的Inferentia/Trainium、阿里巴巴的含光800均属于此类。ASIC开发周期长(1-2年)、流片成本高昂(数千万美元),但一旦量产,单位成本极低。

FPGA(Field Programmable Gate Array)

技术实现

可编程逻辑单元:LUT(查找表)+ 触发器,实现任意组合逻辑

可编程互联:可配置的路由资源连接逻辑单元

硬核IP:嵌入DSP slice、Block RAM、高速收发器

Xilinx Versal(代表产品)

ASIC(Application Specific Integrated Circuit)

全定制设计

逻辑综合:RTL代码→门级网表

物理设计:布局、布线、时序优化

制造:流片(Tape-out),不可修改

Google TPU就是ASIC的典型成功案例

技术发展迭代

| 早期 | ||

| 成熟期 | ||

| AI时代 | ||

| 现状 |

结语:从通用到专用的架构分化

AI处理器的发展呈现出明显的专业化分化趋势:GPU守住通用计算的中央阵地,TPU、NPU、LPU等专用架构在特定场景建立优势,APU则在个人计算设备中推动异构融合。

GPU之所以成为AI领域事实标准,不是因为某一项技术最强,而是平衡性最好:

比TPU灵活,能跑任意算法

比APU/NPU性能高,能训练大模型

比IPU/LPU容量大,能处理大模型

比FPGA/ASIC易用,CUDA生态成熟

但随着AI计算场景分化(云端训练 vs 端侧推理 vs 低延迟服务),专用芯片(TPU、NPU、LPU)正在蚕食GPU的领地,形成"GPU守中央,专用芯片占四方"的格局。

综合对比表

| 定位 | ||||||||

| 架构 | ||||||||

| 计算单元 | ||||||||

| 内存类型 | ||||||||

| 带宽 | ||||||||

| 灵活性 | ||||||||

| 编程难度 | ||||||||

| 生态 | ||||||||

| 代表厂商 |

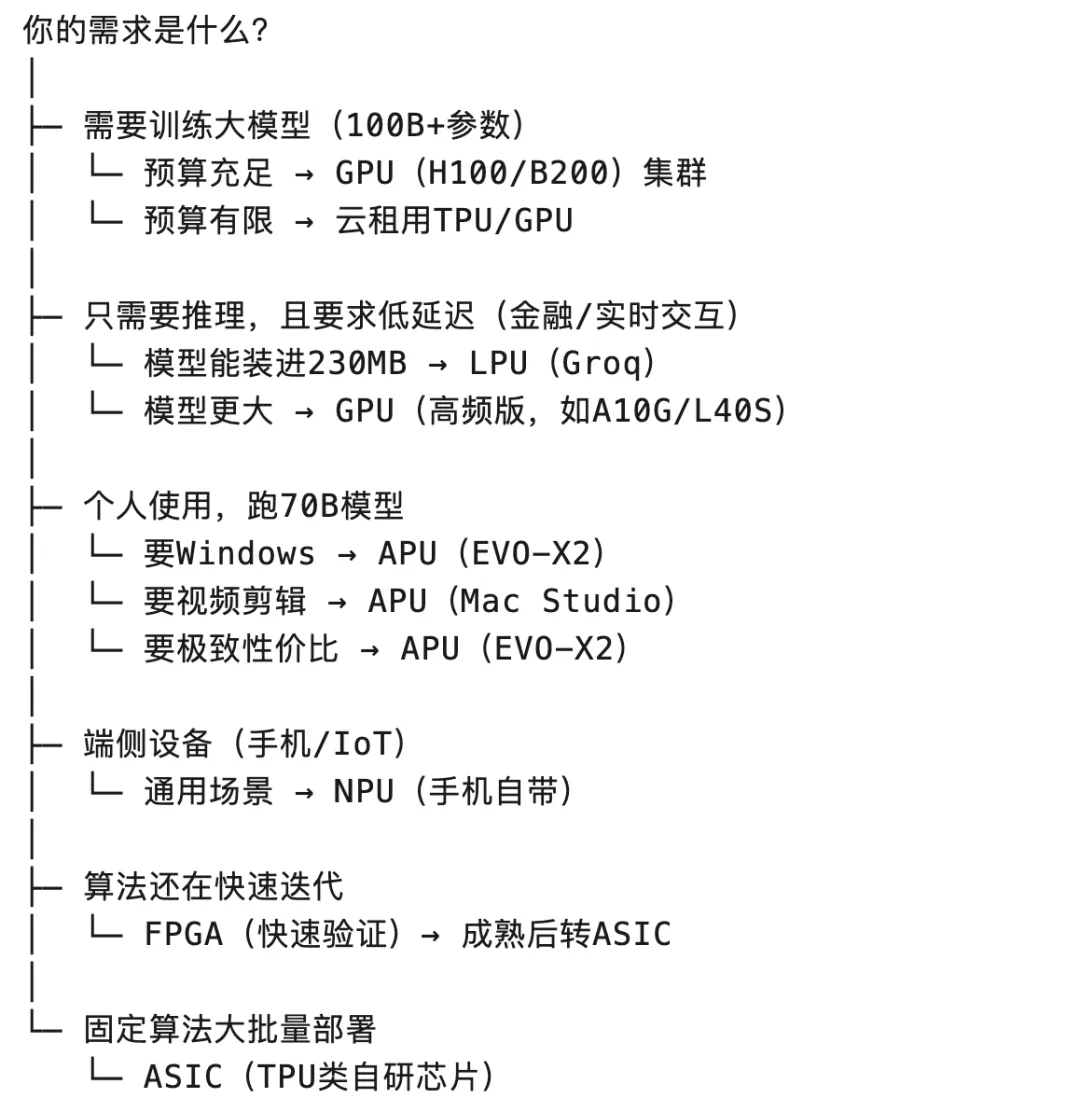

选择决策树

夜雨聆风

夜雨聆风