AI的未来——效率、工具与工程师

文章的内容可以视作对视频文案的整理,方便想快速了解视频内容和喜欢文字阅读的观众。

B站视频教程:

• 合集·模拟电路自动化设计

前面几篇已经跟各位从零介绍该如何搭建一个属于自己的模拟电路前端设计自动化的平台。本文将会做一个相对完整的收束,谈一谈在整理这些内容过程中的一些个人思考,各位权当故事听听就好。

首先会聊聊在工具能力不断增强、AI 开始进入设计流程的背景下,我们应该如何看待模拟电路设计这件事,以及设计者本身所处的位置?该如何平衡工具学习与电路学习之间的关系,以最大化工作学习的效率?

另一方面,当整个行业甚至说整个社会都在追求更高效率时,我们也不得不进一步追问:效率的持续提升,究竟会将工程师,将我们带向何处?

战术上的勤奋,战略上的懒惰

在传统的模拟电路设计领域,很多人是非常勤奋的,我们愿意花费大量的时间去学习电路的原理,分析电路的结构,然后去不断的做仿真、调参数、看波形,一点一点把电路调到满足指标。

这种学习和工作方式是没问题的,而且很大程度上是工程师们构建自己竞争力的基础。

但与此同时,也确实存在一种现象,我听到不少对模拟电路自动化感兴趣的同学提到,当他们把电路优化的工具介绍给学长或者leader的时候,有些工程师会抱着嗤之以鼻,居高临下的态度,相当排斥电路优化的工具。

这背后的原因,一方面是学习成本,另一方面也是路径依赖。一旦已经习惯了一种工作方式,再去切换到新的工具链,其实是需要额外投入的。

但从结果上看,这种“拒绝工具”的状态,未必真的更高效。

在电路设计中,我们经常讲 trade-off,比如功耗、面积、速度之间如何权衡。其实在个人能力上,也存在类似的问题:工具能力和电路能力之间如何分配精力,本身也是一种 trade-off。

如果完全忽略工具,只依赖手工去完成所有流程,很多重复性的工作其实是在不断消耗时间;但如果工具投入过多,而忽略电路本身,又会失去对问题本质的把握。

因此,更合理的状态应该是:**在理解电路的基础上,引入合适的工具,把重复劳动剥离出来。

从这个角度看,工具并不是在“取代设计能力”,而是在放大设计能力的使用效率。

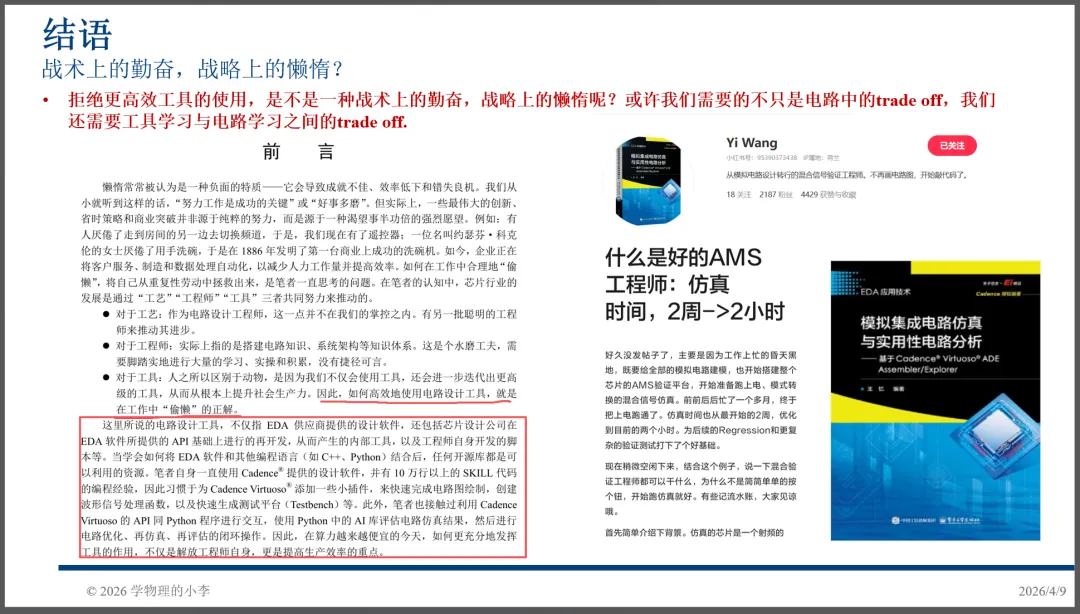

在工具能力和电路能力之间做的比较好的,我觉得王忆老师就是一个很好的榜样,王忆老师就是和何乐年老师一起写《模拟集成电路设计与仿真》一书的共同作者,相信大家对这本书并不陌生。(大伙可以关注王老师的小红书号(●ˇ∀ˇ●))

这里引用王老师在他最新出版的《模拟集成电路仿真与实用性电路分析》书中的一句话:

“在算力越来越便宜的今天,如何更充分地发挥工具的作用,不仅是解放工程师自身,更是提高生产效率的重点。”

从图上我们也可以看到,王老师结合对电路和工具的深度理解,可以将一个两周的AMS仿真验证缩短到短短两小时。我想王老师给我们做了一个很好的示范。

写到这,还有一位对我影响很深的老师也不得不提,这位老师我不知道他的姓名,只知道他知乎的名字叫“sigma delta66”,sigma delta老师也有一个公众号,名字叫“固推铁球”,我不是很能看懂老师的网名😂

抛开网名,老师分享的内容都是极好的,我将公众号中一篇名为《海外 asic 设计咨询公司工作流程简介》的帖子部分内容分享给大家:

"熟悉我的读者都知道我极为推崇建模。建模是我在欧洲留学和工作的过程中学到的最重要的技能。 反观国内很多高校和公司,他们在做 ic 时并没有走"建模-spec-电路"的正向设计流程。很多时候,一个项目的 spec 和设计主要依赖于公司里老人的经验。如果要做某款芯片,而团队里又没有有相关经验的老鸟,那么只能摸着石头过河,或者出去挖角。"

"相比于提图,挖角对整个行业的影响更大。大家都在一个小小的花园里挖呀挖呀的后果只会让大家变得浮躁,无法沉下心来学习和做技术积累,也会带来很多纠纷,甚至牢狱之灾。"

"与之形成鲜明对比的是, 一个重视建模的公司通常不太怕因为失去某个工程师而无法继续做某个项目。因为,这个工程师的思考方式和经验都可以通过建模固化下来,变成公司的无形资产。"

原文链接在这:海外 asic 设计咨询公司工作流程简介

设计工具的理解,不应该局限在 EDA 软件

很多时候,我们提到“电路设计工具”,默认指的就是 Virtuoso、Spectre、ADE 这一类软件。但如果从工程实践角度来看,这样的理解其实是相当狭窄的。

王忆老师在书中也提到:

“这里所说的电路设计工具,不仅指EDA供应商提供的设计软件,还包括芯片设计公司在EDA软件所提供的API基础上进行的再开发,从而产生的内部工具,以及工程师自身开发的脚本等。当学会如何将EDA软件和其他编程语言(如C++、Python)结合后,任何开源库都是可以利用的资源。”

随着近两年大语言模型的发展,尤其是诸如 OpenClaw、OpenAI Codex 等能够通过命令行界面(CLI, Command-Line Interface)直接参与甚至接管部分计算机操作流程的工具出现,对工程师的能力结构也提出了新的要求。

真正有价值的工具,不只是图形界面里的那些功能,还包括围绕这些平台做的二次开发能力,例如:

• SKILL 脚本 • OCEAN 仿真控制 • Python 数据处理与流程组织 • 以及近两年逐渐引入的大语言模型

工具不再只是一个“使用对象”,而是可以被不断扩展、不断组合的系统。谁能够在这个系统之上构建出更高效的流程,谁就能在同样的设计任务中获得更高的效率。

AI for Analog 未来的发展

OpenAI旗下高级编码助手Codex的产品开发负责人Alexander Embiricos 在一档播客中提到,AI 本来应该每天帮助我们成千上万次,但现实中的限制因素,往往不是模型本身,而是人类输入和组织需求的速度; 他还将“人类打字速度”概括为当前被低估的瓶颈。

模拟电路前端设计的“DRC”文件

放到模拟电路设计里,这个问题可以表述得更具体一些:限制自动化效果的,往往不是模型参数规模,而是人能否把经验、约束、边界条件和关键细节整理得足够完整。

或许可以称之为模拟电路前端设计的DRC文件,模拟电路设计目前缺少的,某种程度上就是这样一套系统化的规则描述。

当然,这里的“规则”并不是简单的版图规则,而更接近一种综合性的设计约束,包括:

• 性能指标及优先级 • 模块之间的接口关系 • 参数可调范围 • 仿真与验证流程 • PVT 条件与边界情况 • 一些经验性的设计规则

如果这些内容能够被整理出来,那么很多原本依赖人工反复试探的过程,就有机会被自动化系统接管。通过Verilog-A,Matlab等对模拟电路进行行为级建模,某种程度上就是一种数学建模形式的综合性的设计约束。

知识沉淀成工程资产

如果进一步看,这其实还意味着设计者角色的一种变化。

过去,一个优秀的模拟工程师,其核心竞争力往往体现在个人经验上: 他知道某种拓扑该如何起步,知道某个模块在哪些条件下容易失稳,知道哪些参数变化最敏感,知道从仿真波形里能看出哪些隐患。这样的经验极其重要,也极具价值。

但在自动化与 AI 时代,仅仅“个人会做”可能已经不够。更有价值的能力,正在变成另一件事:能否把原本只能存在于个人脑中的经验,转化成可以被调用、被复用、被迭代的工程资产。

• 对于学生而言,这种资产可以表现为自己的知识库、脚本库、测试模板与设计笔记。 • 对于企业而言,它则意味着流程资产、模块资产、验证资产,甚至是某一类电路的设计范式本身。

一旦某类电路的知识被整理得足够完备,其重复性设计工作就会越来越容易被自动化系统接管。人类设计者的工作将逐渐从“手工完成所有步骤”,转向“定义问题、整理约束、审阅结果、修正规则”。

因此,未来更具竞争力的工程师,也许不一定只是那个“手调最厉害”的人,而更可能是那个最能把经验系统化、最能把设计流程结构化、最能构建可持续迭代框架的人。

孙龙虾!!!

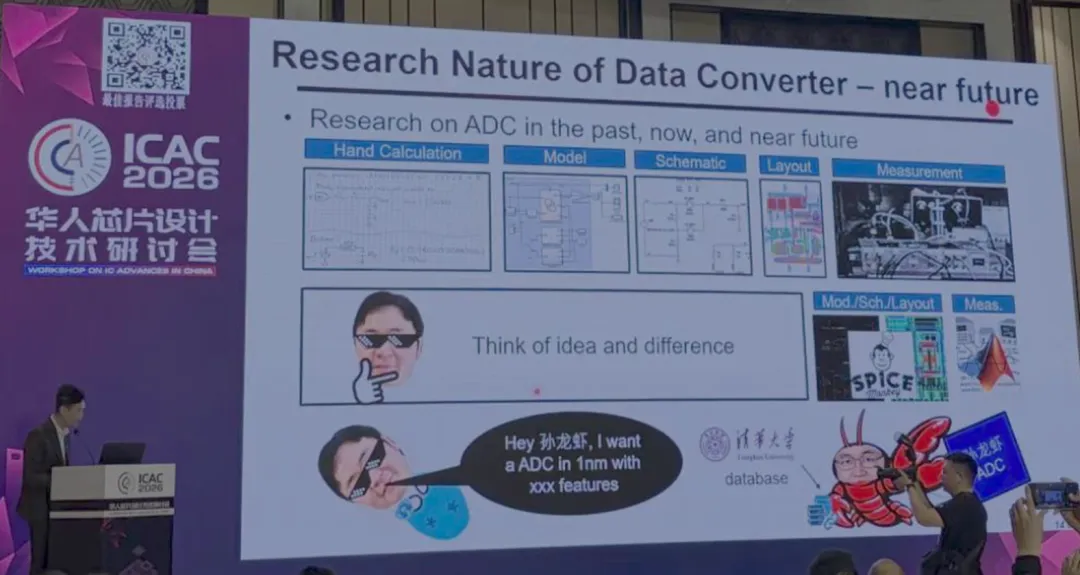

在前两天2026年的ICAC会议上,陈知行老师的分享也多少代表了教授们对目前AI for Analog的看法,

孙楠 + 清华大学的datasheet = a ADC in 1nm xxx features。

(笑)这实在是太有趣了,不是吗?

越来越多的工作已经开始从“个人手工推进”转向“流程辅助推进”。设计者依然重要,但他的角色正在变化:不再只是单纯的执行者,而是流程的组织者、数据的解读者和约束的设定者。

再往前看,一个更值得关注的趋势是:基于数据库、知识库和历史设计资产的智能生成。也就是说,设计者不再每次都从头开始,而是在已有积累上提出目标,由系统快速生成候选方案,再由人做高层决策与判断。

初级工程师们不再被需要,因为基础电路早已被内化成一套AI可以快速生成的候选方案,只需要高级工程师们参与决策与判断即可。

高级工程师们也更可能和快速的构建约束清晰,边界条件充足“DRC”,以此替代电路优化中的初级工程师们的工作。从这个角度看,AI似乎大大加剧了马太效应?

“凡有的,还要加倍给他,叫他有余;没有的,连他所有的,也要夺过来。”

要一味追求效率吗?

效率越高,工程师真的会更轻松吗

前面我们讨论了很多东西,但是最根本的目的都是追求更高的效率.如果只从技术角度看,上述演进无疑是积极的。自动化、脚本化、AI 化,都在不断提高生产效率,缩短设计周期,扩大探索空间,并降低大量重复劳动的成本。

我们一直在讨论如何更快完成设计、如何更快收敛指标、如何更快搭建流程、如何更快提高效率。让我们回忆一下王忆老师书中对效率提升之后的想象:

“在算力越来越便宜的今天,如何更充分地发挥工具的作用,不仅是解放工程师自身,更是提高生产效率的重点。”

然而,效率是越来越高了,但是工程师的工作真的会变得更轻松吗?工作体验真的会更愉悦吗?个体的幸福感真的会因此增强吗?

未必如此。

从现实经验看,更高的效率往往并不会自动换来更少的压力。相反,它常常意味着:

• 更高的交付预期; • 更紧的项目周期; • 更少的缓冲空间; • 更高密度的任务安排; • 更强的可替代性焦虑。

当工具能力增强之后,系统对个体的要求往往也会同步提高。原本需要几天完成的工作,可能会被默认一天内完成;原本需要多人协作的流程,可能会被要求由更少的人更快完成。于是,效率提升带来的不只是便利,也可能是更强的压缩效应。

在这种情况下,工程师并不一定因为工具更强而更轻松,反而可能因为系统运转更快而被卷入更高强度的工作节奏之中。

劳动者的异化

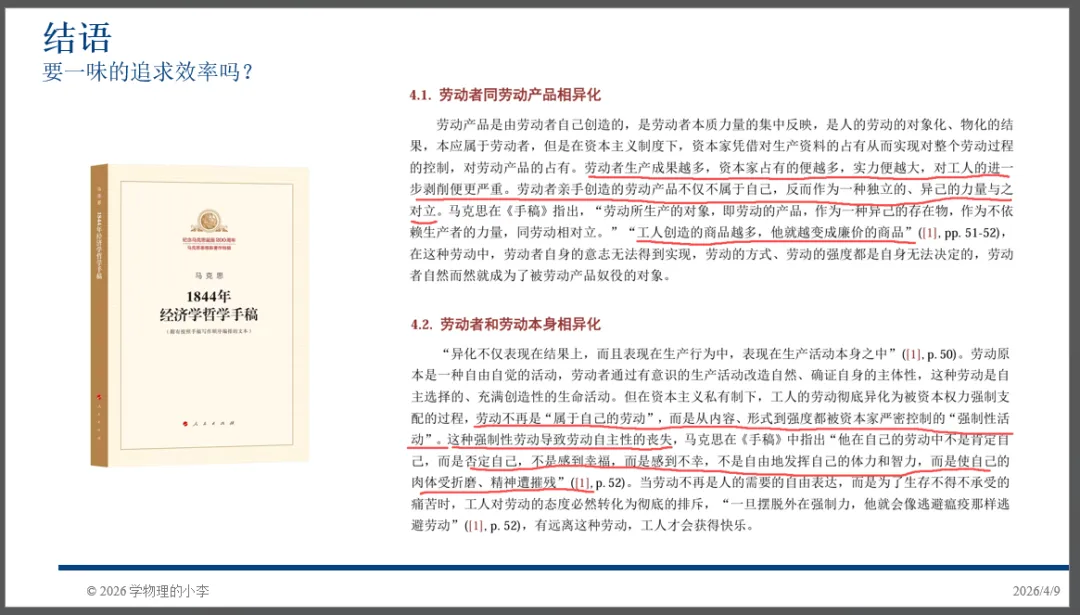

马克思早在一百多年前就已经对现状有了预测,其在《1844年经济学哲学手稿》中就有提到:

劳动者同劳动产品相异化

“劳动者生产成果越多,资本家占有的便越多,实力便越大,对工人的进一步剥削便更严重。劳动者亲手创造的劳动产品不仅不属于自己,反而作为一种独立的、异己的力量与之对立。”

“工人创造的商品越多,他就越变成廉价的商品”

劳动者同劳动本身相异化

“他在自己的劳动中不是肯定自己,而是否定自己,不是感到幸福,而是感到不幸,不是自由地发挥自己的体力和智力,而是使自己的肉体受折磨,精神遭摧残。”

“当劳动不再是人的需要的自由表达,而是为了生存不得不承受的痛苦时,工人对劳动的态度必然转化为彻底的排斥”

当然,有些同学和工程师们可能会说,我在学习和工作的过程中,充分的发挥了自己的体力和智力,我能从工作和学习中感受到幸福与满足感。

这当然是一种非常健康且良好的状态,这类同学和工程师们大多能胜任自身的工作和学习,能够游刃有余的完成任务。但是,需要警惕的是这种状态表面上看像是积极进取,实际上却可能逐渐演化为一种持续性的自我加压。

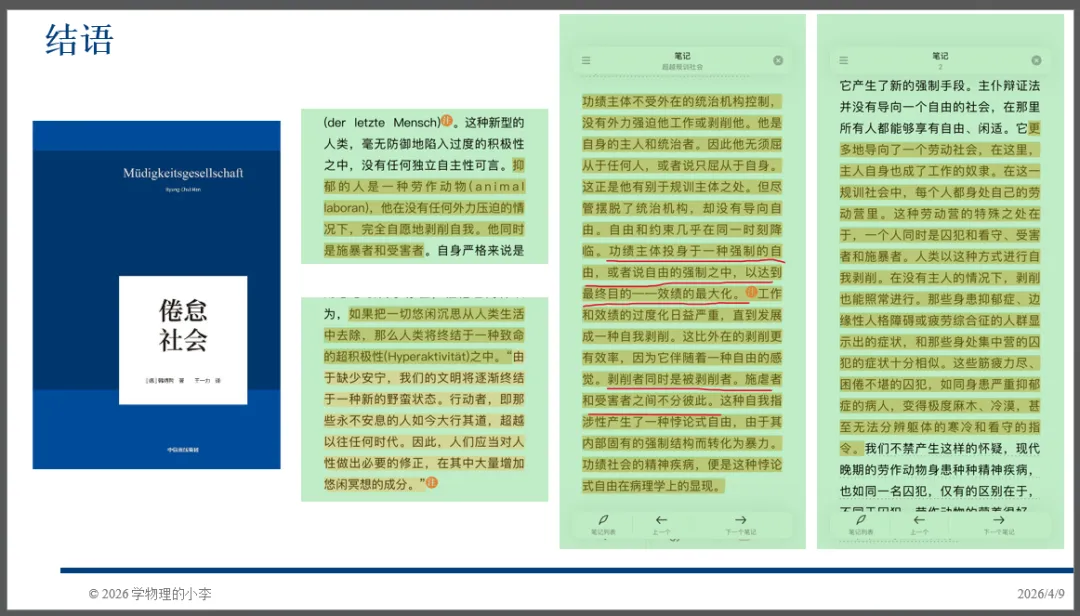

倦怠社会

在一个高度强调效率、绩效与持续进步的环境中,人很容易把效率要求内化为对自己的要求。即使没有外部强制,也会主动要求自己更快、更强、更会用工具、更能组织信息、更能适应系统。

尤其对于学生而言,这一点并不陌生。我们身处学校,没有企业对我们的kpi要求,我们也不需要通过工作来维持生存,但是学生们会不断逼迫自己掌握更多工具、学习更多框架、构建更多能力,只为了在未来的竞争中不被淘汰。

于是,一个值得警惕的变化出现了:外部压迫并未消失,但它越来越多地被转化为个体内部的自我要求。人一边享受效率工具带来的“能力增强”感,一边也更深地卷入了一种无法轻易停下来的自我驱动机制。

出生于1959年的韩裔德国哲学家韩炳哲在其《倦怠社会》中提到:

“功绩主体投身于一种强制的自由,或者说自由的强制中,以达到最终目的——效绩的最大化。”

“工作和效绩的过度化日益严重,直到发展成一种自我剥削。这比外在的剥削更有效率,因为它伴随着一种自由的感觉。”

“剥削者同时是被剥削者,施虐者和受害者之间不分彼此。”

一个更形象的比喻是:

在一个规训社会中,每个人都身处自己的劳动营里。这种劳动营的特殊之处在于,一个人同时既是囚犯和看守、受害者和施暴者。人类以这种方式进行自我剥削。在没有主任的情况下,剥削也能照常进行。

从这个意义上说,AI 时代的问题,不只是技术问题,也不只是就业问题。

回到模拟电路自动化

回到这整个系列内容本身,它的目标从来都不只是教会大家几条命令、几段脚本,或者演示如何把 Virtuoso、Spectre、OCEAN 和 Python 拼接起来。

更重要的是,希望借此提供一种新的理解框架:

模拟电路自动化设计,并不是要取消对电路本质的理解,也不是要否定传统训练的重要性;相反,它是在承认模拟设计复杂性的前提下,尝试将那些高重复、高成本、低复用性的部分,从纯手工路径中剥离出来,并进一步构建为可以持续演化的工程系统。

从这个角度看,模拟电路自动化的价值主要体现在三个层面。

• 其一,它能够提高具体工程流程的效率,减少大量机械性操作。 • 其二,它迫使设计者重新思考自己的知识结构,推动经验从“个人技巧”转向“显式规则”。 • 其三,它为未来 AI 更深层次地介入设计活动提供了前提条件。

也正因为如此,真正值得投入的,不只是某一个脚本、某一套命令或者某一个局部 demo,而是如何围绕这些内容逐步建立起自己的方法论、知识库和工程框架。

结语:自动化不是终点

模拟电路自动化设计的发展,或者说AI的发展,表面上看是工具和流程的演进,实质上却是一场关于知识组织方式、劳动形式以及工程师角色的重构。

从手工设计到脚本化流程,从优化算法到 AI agent,这条路径并不只是技术升级的自然结果,而是整个工程体系在复杂度持续上升背景下的一种必然回应。未来,设计者的价值不会消失,但其体现方式会发生明显变化:从局部实现者转向系统组织者,从经验拥有者转向知识结构化者,从单次设计完成者转向工程资产建设者。

但与此同时,我们也必须意识到,效率提升并不天然导向个体解放。 工具越强,系统越可能要求更快的响应、更高的产出和更少的停顿。AI 带来的不只是新的生产力,也可能是新的压力机制和新的劳动关系。

因此,讨论模拟电路自动化,不能只停留在“怎么做得更快”这一层面。更深的问题在于:当设计流程越来越智能、越来越高效、越来越可规模化时,工程师应如何重新理解自己的位置,如何既利用这些工具,又不完全被效率逻辑所吞没。

这或许才是自动化时代真正值得持续思考的问题,期待各位工程师和研究者在这一领域持续探索,把自己的经验、思考与创造力真正融入到自动化设计之中。

推荐阅读

模拟电路前端自动设计实战 | Part 3:构建自己的模拟电路前端自动化设计平台模拟电路前端自动设计实战 | Part 2:Virtuoso 自动化仿真基础:从网表、PSF 到 Spectre 与 OCEAN模拟电路前端自动设计实战 | Part1:模拟电路自动化技术研究现状与商业化软件模拟电路前端自动设计实战 | Part0:模拟电路小龙虾——从运放验证到SAR ADC实践

夜雨聆风

夜雨聆风