01

景芯DFT实战课

景芯团队DFT专家老师授课,一对一辅导,主打文档+服务器实战,通过3个系列课程依次完成HD6850各个关键子系统的DFT设计实战后,再完成全芯片TOP DFT实战,让您快速超越同龄人!我们不卖视频,只提供免费导学视频,景芯团队始终坚信实践和服务才是景芯训练营+design service的核心。

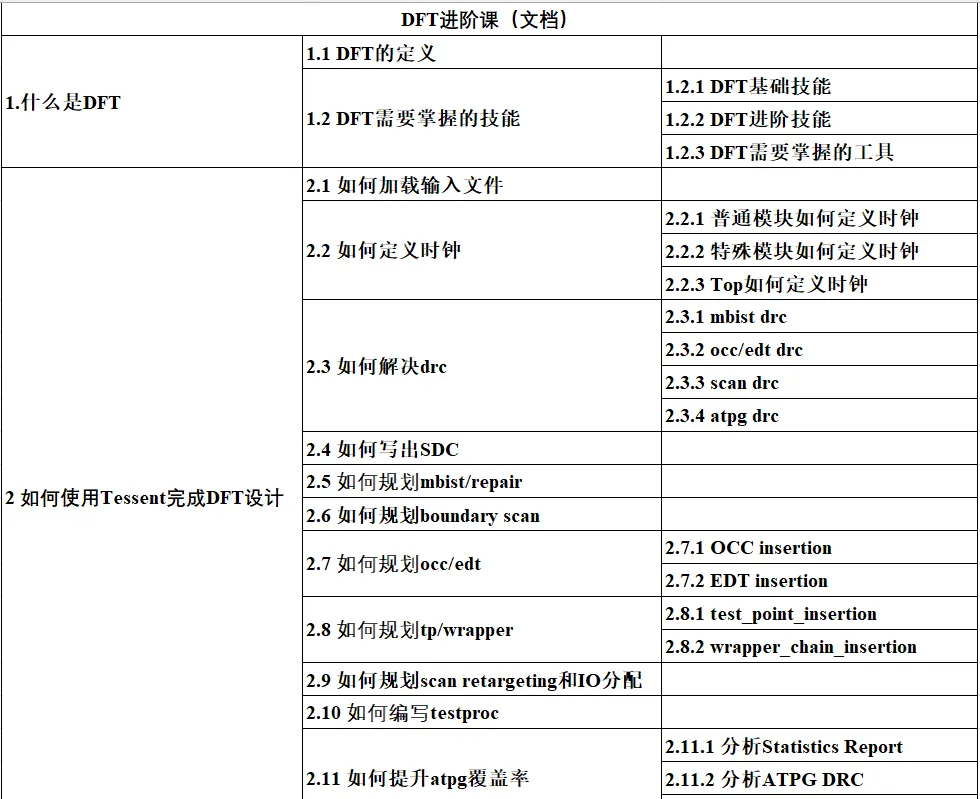

02

DFT课程1:40nm DFT hieraychy实战

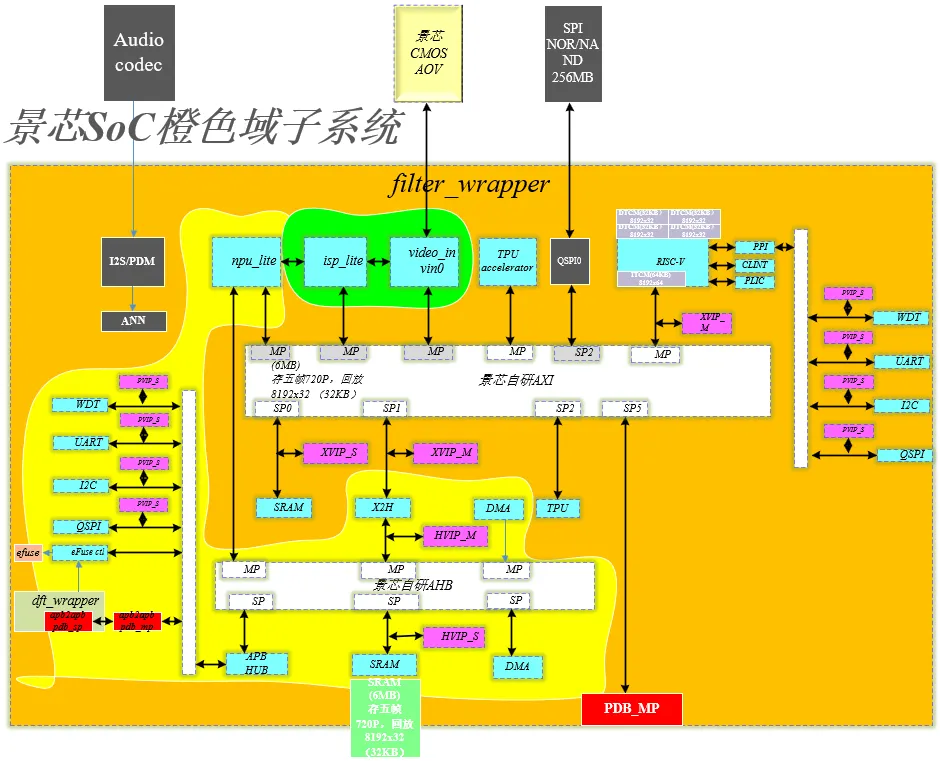

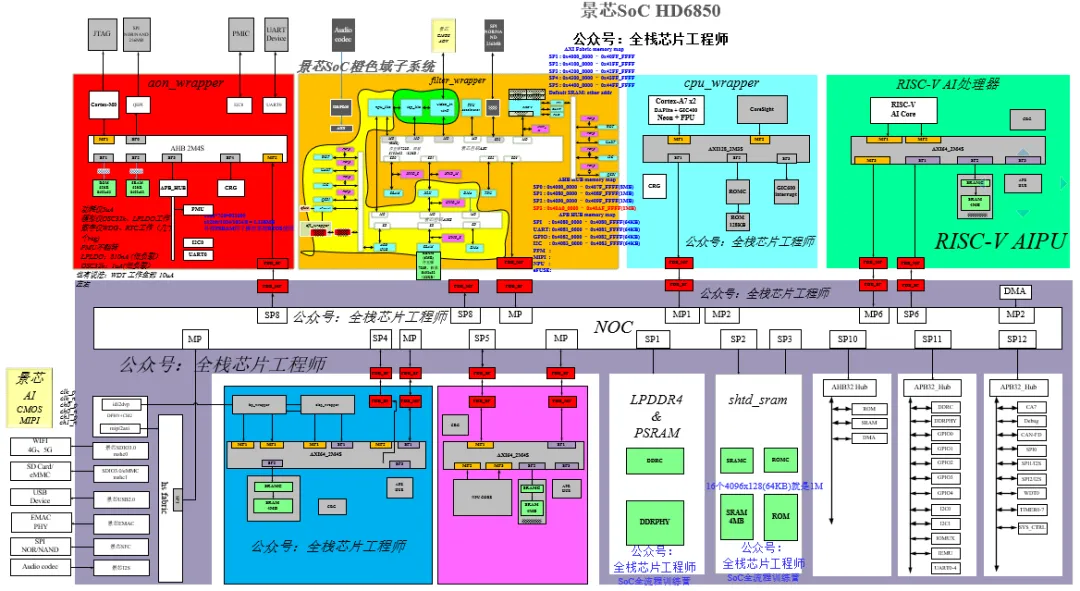

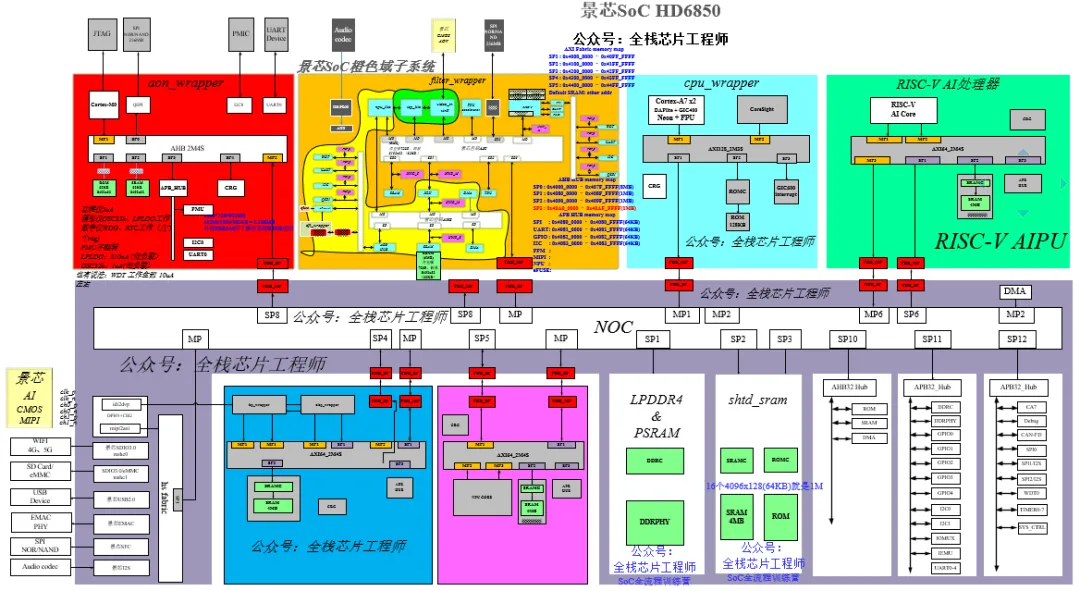

为了满足不同经验的学员需求,景芯团队DFT老师开发了hierarchy与flatten两套环境进行实战,flatten用以快速入门,而在hierarchy设计流程中,DFT工程师的工作需围绕 “模块测试覆盖” 与 “顶层集成效率” 展开,40nm实战课程采用上图橙色子系统作为全芯片实战内容。

Part.01

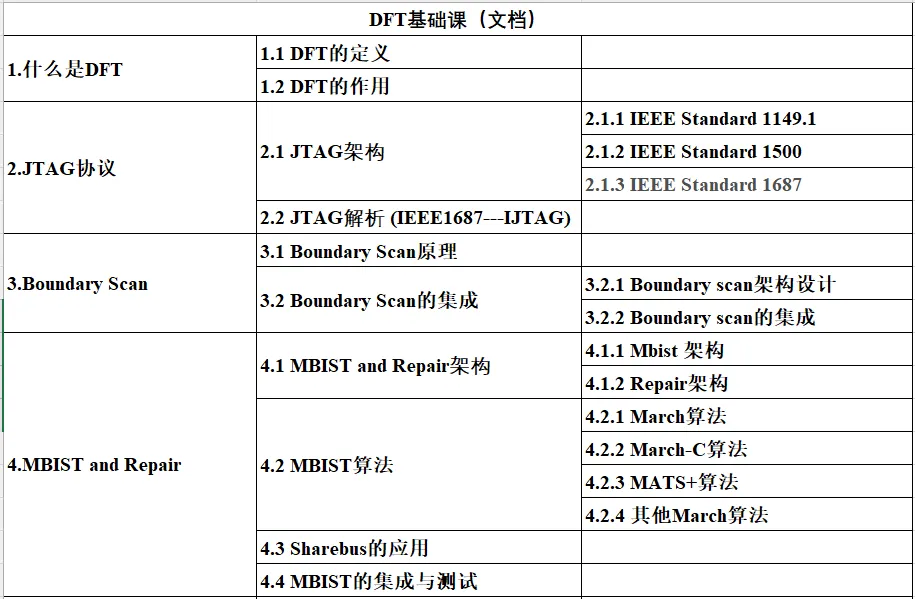

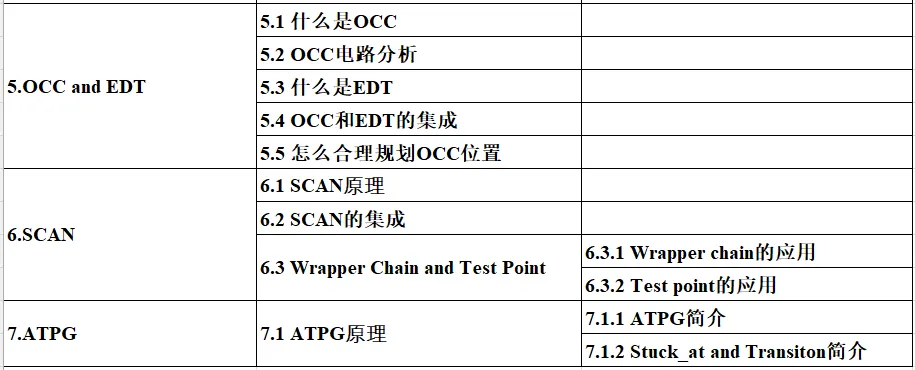

基础实战目录(flat flow)

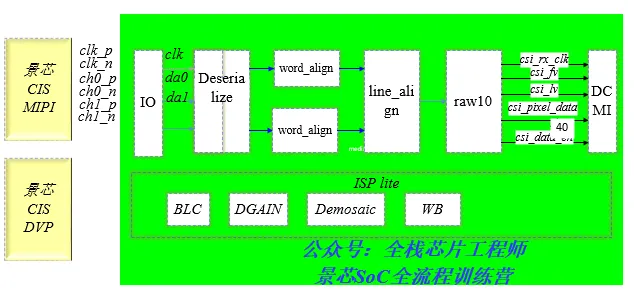

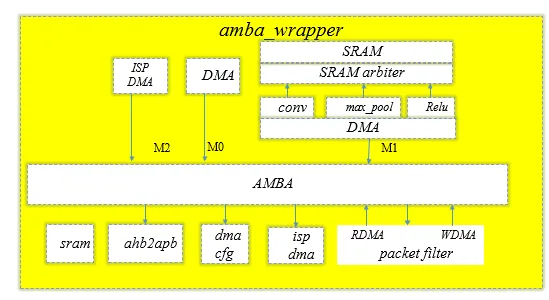

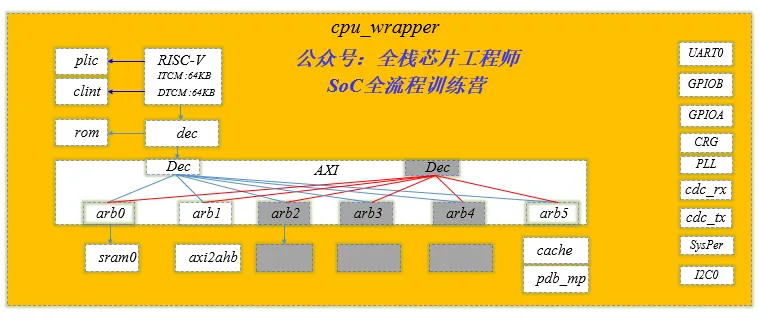

1、基础课采用橙色子系统作为单独的AI MCU芯片来进行实战,采用flatten flow进行实战。橙色域采用低功耗RISC-V自研架构,全部自研实现了AXI总线矩阵、AHB总线矩阵、MIPI DPHY软核、ISP-Lite、NPU-lite、SRAM、DMA、UART、I2C、QSPI/SPI等常用IP,项目设计验证架构如下:

Part.02

基础实战目录(flat flow)

Part.03

基础实战目录(hierarchy flow)

进阶课采用橙色子系统作为单独的AI MCU芯片来进行实战,采用hierarchy flow进行实战。景芯橙色域子系统分为三个subchip子系统,包括media_wrapper、amba_wrapper、cpu_wrapper三个subchip,完成每个子系统的DFT后,然后进行TOP的DFT实战。每个subchip的功能描述如下:

media wrapper(上图青色部分)负责MIPI图像输入、DPV图像输入、异步处理、ISP图像处理。

amba wrapper(浅黄色部分)负责接收media wrapper传递过来的经过ISP预处理过的图像,通过专用DMA搬运数据到amba wrapper系统主存SRAM,DMA搬运完成后,CPU配置NPU搬运系统主存SRAM的图像数据去做矩阵运算(卷积)。

cpu wrapper负责RISC-V CPU、TCM、自研AXI总线矩阵的译码、仲裁、AXI2AHB总线桥、中断系统、低功耗PMU管理等功能。NPU卷积完成后,RISC-V CPU执行WFI指令进入休眠模式。通过isolate信号和retain信号进行时钟门控、电源门控。

Part.04

进阶实战目录(hierarchy flow)

关键环节包括:

模块级(Block Level)Scan Wrapper 实现:为每个独立模块设计扫描wrapper电路,确保单个模块的测试点可访问、测试逻辑无遗漏,为后续集成测试打下基础;

简化模型应用:抽取模块的 Graybox(灰盒)简化模型,替代复杂的全模块模型参与顶层设计,显著降低顶层 DFT 工作的运行时间(Runtime),提升设计效率;

测试电路集成与规划:负责各模块 DFT 电路的顶层整合,同时参与模块摆放规划,确保测试信号的传输路径合理,避免因布局问题影响测试效果。

两种设计架构无绝对优劣,小型项目选Flatten可追求高效闭环,大型项目用 Hierarchy能破解复杂度难题。而DFT工程师在层次化流程中的精细化操作,正是保障复杂芯片测试覆盖率与研发效率的关键所在。

Part.06

课程报名微信,扫描咨询我们吧

景芯SoC芯片全流程实战附属【知识星球】,一个包括设计、验证、DFT、后端全流程技术的交流平台,也是景芯学员的答疑平台!若您和我一样渴求技术,那欢迎扫下面二维码加入星球,共同进步!

02

DFT课程2:12nm DFT CPU hieraychy实战

为了完成sharbus memory bist、occ、edt、12nm DC综合、scan、gray_box、ATPG、mbist仿真、dc/ac仿真、formal(rtl2rtl、rtl2netlist、netlist2netlist)等hierarchy DFT flow,我们特选取HD6850项目的多核处理器进行12nm DFT flow实战,包括12nm综合、12nm Formality等flow,全网唯一DFT高级实战课!

03

DFT课程3:12nm HD6850全芯片DFT实战

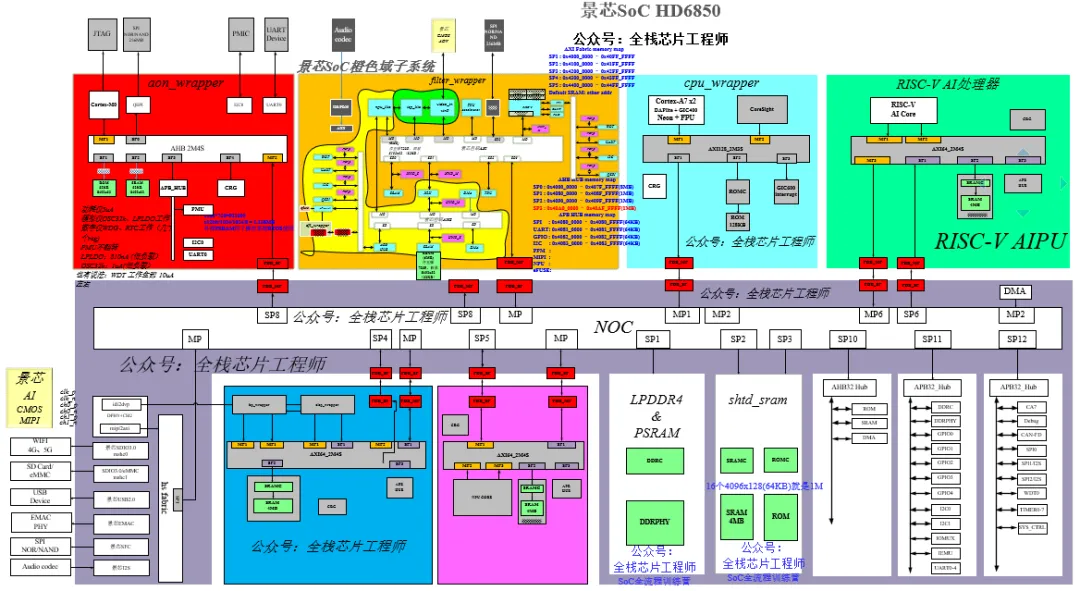

课程3将会完成景芯HD6850全芯片DFT实战设计,难度极大,芯片整体结构如下图所示:

芯片整体结构如下图所示:

Top:riscv_soc_top;

Harden block:filter_wrapper/cpu_wrapper/shtd_wrapper/aon_wrapper;其中cpu_wrapper下面又包含一个子模块cortexa7_core;

filter_wrapper/aon_wrapper是纯数字模块,按照正常流程走即可。

1.make mbist:插入mbist测试逻辑;

2.make occ_edt:插入occ和edt,为scan测试做准备;

make gen_file:将tsdb目录下的文件整理成vcs可读的filelist,方便综合和vcs仿真;

make pat_gen:生成mbist_pattern,无需改动design;

3.make syn:将做完mbist的rtl综合成netlist,可以用for_synthesis.tcl,也可以用gen_file生成的dft_filelist;

4.make scan:将所有的寄存器按照需求串chain

make graybox:抽出graybox网表(包含ijtag逻辑和wrapper逻辑),顶层block可以只带graybox网表做dft或者仿真,加速流程。

make dc_ext:根据graybox网表跑external atpg,跑通即可,无需关注覆盖率等信息

make dc:stuck at向量生成,需要read dc_ext fault,提高覆盖率

make ac:transition向量生成

5.make mbist_sim:mbist仿真

make dc_sim:stuck at仿真

make ac_sim:transition仿真

shtd_wrapper内部包含mipi phy,需要特殊处理。

1.make mbist:phy内部一般不含memory,即使有memory也不需要做mbist(phy内部自带电路测试),无需特殊处理;

2.make occ_edt:注意解决phy内部的drc;

3.make syn:吃入phy的db优化时序,也可不吃;

4.make scan/dc/ac/ext:需要读入phy的tcd文件,一般ip厂商会提供ctl文件(Synopsys专用格式),需要使用工具将ctl文件转译成tcd文件;phy内部的register需要单独串chain,不允许和shtd_wrapper内的寄存器串在同一条chain上。

5.make mbist_sim/dc_sim/ac_sim:需要吃phy的netlist;

cpu_wrapper/cortexa7_core需要做sharebus mbist,流程也会有所不同。

1.make mbist:cortexa7_core中memory的sharebus mbist逻辑已经集成在了cpu_wrapper中,无需做mbist,直接从occ_edt开始做;待cortexa7_core做完之后才可做cpu_wrapper的mbist,cpu_wrapper做完mbist后,需要将cortexa7_core部分rtl删除,只需要将tsdb中的cortexa7core.v删除即可;

2.make occ_edt

3.make syn

4.make scan/dc/ac/ext

5.make mbist_sim/dc_sim/ac_sim

riscv_soc_top为芯片的顶层,待所有block完成之后才可开始做dft;

1.make mbist:注意bscan相关IO的处理;

2.make occ_edt:无论顶层是否有logic,建议都要当作正常模块来做,这里要做好retarget准备,合理分配io数量和测试模块;

3.make syn;

4.make scan/dc/retarget_mode_transition/retarget_mode_stuck:顶层没有logic,无需做ac;

5.make mbist_sim/dc_sim/ac_sim/retarget_dc/retarget_ac:mbist仿真包括bscan和repair仿真,不需要仿真的模块可以吃graybox,加快仿真进程;

04

DFT招聘:景芯DFT学员供不应求

职位:SoC 中端工程师

岗位职责:

1、负责模块级与芯片级 Synthesis、Formal check 等工作;

2、负责完成 sdc, upf 等文件;

3、负责综合 netlist、sdc、upf 等交付工作;

4、协助后端 signoff;

5、熟悉 DFT 工具,独立进行 DFT 设计与仿真工作,包括 BSD、Mbist、Scan。

任职要求:

1、微电子、电子工程等相关专业硕士及以上学历,三年以上工作经验;

2、熟练使用 DC/Formality/PrimeTime 等 EDA 工具;

3、熟练使用 tcl/perl/shell/python/makefile 等编程语言;

4、熟练掌握 DFT 工具,能独立完成 DFT 设计与仿真者优先考虑;

5、熟练掌握 Low Power 设计者优先;

6、具有良好的表达沟通能力及团队合作精神,具有较强的独立工作能力和动手能力;

7、良好的英文阅读、文档编写能力。

Part.01

学员案列分享

1.ram周边的bypass逻辑是怎么做进去的?

答:工具自动做进去,通过memory_bypass_en即可启用。

set_config_valuescan_bypass_logic sync_mux -in/DftSpecification()/MemoryBist/Controller(c1)/Step<0>/MemoryInterface(m1)

2.如何分配MBIST内的controller的step、memory?

答:通过直接修改spec或者手动编辑命令即可设置。

DefaultsSpecification() {DftSpecification{MemoryBist{max_steps_per_controller: 4max_memories_per_step:6}}}

3. 怎么手动对memory进行分组?

答:set_memory_instance_options group_name,可以使用该命令对所有memory进行手动分组。

4.boundary scan逻辑为什么不上chain?

答:bscan和scan是两种不同的测试mode,测试方案和原理都不同;bscan会将scan关键信号如scan_en、edt_update的IO纳入测试范围,因此不能上chain。

5.对于不同功能的IO PAD,bscan会如何处理?IO PAD的IE/OE在scan和bscan过程中如何避免相互影响?

答:不管是高速IO还是普通GPIO,boundary scan都是用低速时钟测试,测试方案与IO PAD功能无关。Scan和bscan都会控制IO PAD的IE/OE,但二者是完全隔离开的,测试时不会相互影响,scan阶段IE/OE可以通过tdr自行管控,bscan阶段IE/OE由工具自行接管控制。

6.对于包含多个TAP controller的芯片,boundary_scan是如何测试的?

答:一般而言只需要一个top放置在顶层即可,底层的bscan可以和顶层串一起测试;有多个TAP controller的芯片会将顶层和底层完全分隔开,各自独立进行测试。

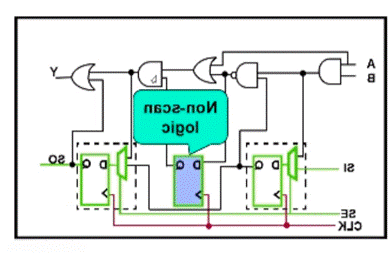

二、EDT/OCC

1.Ijtag网络的逻辑都不上chain吗?

答:少部分sti(scan test instrument)逻辑可以上chain,其余部分都不上chain。

2.occ chain和其余scan chain有什么不同?

答:occ chain是将所有occ内部待测逻辑串成一条chain,这条chain不仅有nonscan cell还有组合逻辑;其他的scan chain上只有scan cell和移位寄存器,不允许有组合逻辑。Occ chain可以与scan chain串一起,但由于其特殊结构(负沿采样、有组合逻辑等)会影响到capture pulse(降低压缩效率和覆盖率),因此occ_chain不建议与其他scan chain混在一起,Tessent工具会自行将occ单独串chain。(不是独占一个scan channel,而是单独占用一条scan chain)

3.edt_bypass是怎么实现的?

答:set_core_instance_parameters –instances $edt_instance -parameter_values {edt_bypass on};不需要单独设置edt_bypass mode。

4.如何让工具不自动修复rst?

答:set_drc_handling DFT_C9 –auto_fix off。在edt_occ_insertion过程中,工具会自动修复rst相关的违例,使用该命令可以让工具检测到rst违例后直接报错,不自动修复;工具往往会将有问题的复位信号bypass到DFT指定的复位上,但修复方式太过简单粗暴,建议将它关闭。

5.edt的压缩比该怎么选择?

答:一般来说不超过200即可。需要提前分配好retarget mode,确定每个retarget mode有多少IO可以用作scan_channel_in/out,在根据每个retarget mode所有模块的寄存器总数量除以scan_chain_length再除以IO数量再乘以2,即可得到压缩比的数值。

6.OCC上为什么会有ijtag接口,它的作用是什么?

答:在test_setup阶段,DFT可以通过ijtag网络配置需要的信号,occ内部也有ijtag控制网络,配置后使得OCC启用相应的功能。

三、SYN

1.基于触发器、锁存器的时钟门控有什么区别?

答:时钟门控是用来控制时钟关断的元器件,实际项目中会使用大量的门控来控制功耗。厂家提供的库文件中有封装好的门控单元,实际项目中可以直接调用,很大程度上避免了毛刺的产生。锁存器是高/低电平触发,寄存器是上升/下降沿触发,他们都可以用来组合成时钟门控单元,但基于面积的考虑,实际上使用锁存器居多。

四、SCAN

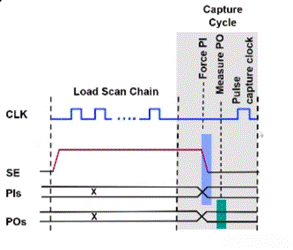

1.scancapture频率过高会有什么问题?scanshift频率过高会有什么问题?

答:scanhscapture频率和function保持一致,频率过高会导致功耗过高且时序难以收敛;scanlscapture频率和scanshift一致,scanshift频率越高DFT测试时间越短,DFT测试成本越低,对节省芯片成本有很大的好处,但频率过高会导致时序难以收敛、测试功耗过高、SE从1到0切换不及时等等。对于DFT而言Scanshift频率越高越好,scanhscapture频率由function决定。

2.PLL后面接的divider逻辑需要串chain吗?

答:对于普通SOC而言,divider不能串chain;divider一旦上chain,transition时divider因为上chain会失去分频功能,导致divider不能输出指定频率时钟,该时钟域下的寄存器无法测试。对于车规芯片,需要追求极致的覆盖率,可以让divider在stuck_at下上chain,在transition下不上chain。

3.如何判断哪些port需要插入wrapper_cell,哪些port需要被exclude?

答:插入wrapper_cell后的port在信号传递过程中被改变了,原本的值无法正常传递到core_chain内部或者从core_chain内部传递出去;在这个前提条件下,只有不关心当前状态值的port才能插入wrapper_cell。通常需要exclude的port有dft控制信号(scan_enedt_undate dft_mode 等等)、时钟输入输出信号(有些没有被定义的时钟,DFT不需要)、ijtag信号、没有组合逻辑的信号等等。Tessent工具会自动筛选一部分信号exclude,实际项目中会有一些特殊需求,经常需要手动调整exclude list。

4.什么是scan reorder?

答:后端在布局布线时,会发现有一些scan_chain上的寄存器连接顺序不合理,导致绕线困难,此时需要在不影响function的前提下对这条scan_chain重新排序,这个过程叫做scan reorder。DFT做完scan后需要交付scan netlist和scandef,scandef里面会包含reorder相关信息,后端工具会根据scandef文件自动进行scan reorder。

五、ATPG

1.chip_top跑ATPG时序如何删除DFT不相关的port?

答:delete_primary_input delete_primary_output;ATPG时经常有删除DFT不相关port的需求,若不删除,工具会对这些IO赋值导致ATE测试fail。

2.什么是force_pi和measure_po,scanshift阶段有force_pi和measure_po吗?

答:scanshift阶段会将scan_channel_in的数据逐步shift到每一级scan register中(或shift out),此时没有force_pi和measure_po,在scancapture clock pulse到来之前会先进行force_pi和measure_po。对于block而言,工具会将输入输出端口视作PI/PO,通过对这些端口赋值(force_pi),经过一些列组合逻辑传导之后对输出端口进行观测(measure_po)。实际芯片测试中,由于各种条件限制往往会删掉多余的input/output io,舍弃这部分coverage。

2. retarget的作用是什么?retartget mode和top的edt_mode会分时起作用吗?

答:大型SOC所有模块同时测试所需的io数量过多,芯片的io数量是有限的,不够用,因此引入了retarget。Top的intest会带底层block的extest一起测试,所以top_only需要单独作为一个测试mode,;其余block按照层次可以分为retarget1~n,不同retarget之间不能同时测试,同一个retarget内部的模块可以同时测试,Top_only视为一个特殊的retarget_mode。

3.对于int_edt和ext_edt架构,生成graybox时需要将channal_output设置为ignore_for_graybox吗?

答:不需要,工具会自行处理好相关逻辑。Graybox需要保留好int/ext edt、wrapper_chain等相关逻辑,后期retarget时需要用到,减少atpg和仿真时间。

4.tessent atpg有restore_session相似的操作吗?

答:write_flat_model写出flat_model,然后set_context pattern –scan,read_flat_model即可。

5.跑atpg时,什么情况下需要吃sdc?

答:在后仿阶段跑atpg需要吃sdc,前仿阶段不需要。在signoff过程中往往会有些高速路径是假path或者时序收不下来,需要设置mcp或者false_path放掉,工具会根据这些sdc自行推到相应的pattern避免出现violation。Dc一般不需要吃sdc,慢速路径一般不会出现问题;ac需要吃sdc,出问题的路径,往往都是高速路径。

6.为什么atpg覆盖率报告里有一些选项,但是脚本中没有,例如mask_po?

答:当不想对某些output port进行观测时,可以用add_po_mask将其屏蔽掉;工具会有很多默认选项,不需要用户一个个设置,大大简化了atpg流程,如果确实影响到了design,才需要用户手动调整。

六、SIM

1.DFT过程中PLL设置成了black_box,vcs仿真过程中PLL怎么震荡出高频时钟?

答:black_box是DFT过程中的概念,vcs没有black_box的说法。只要吃入了PLL model,并咋向量中配置好了分频系数、参考时钟等参数,PLL即可正常工作。

七、STA

1.scanshift和scanlscapture可以合并为一个mode进行signoff吗?

答:不同芯片有不同的signoff策略。大型SOC时钟频率较高,时序复杂,不建议合并任何一个mode;小芯片时钟慢,时序简单,可以随意合并。

2.tessent_set_ltest_madal_edt_fast_capture为什么约束scan_en为0但slow_capture不约束scan_en,fast_capture需要约束fast_capture_mode吗?

答:tessent sdc里面的proc只提供最简单的约束,在大型SOC中需要手动补齐其他sdc,例如scan_en的值需要自己写sdc来定义(配合公司的signoff策略)。Fast_capture_mode是通过ijtag网络配置的信号,在fast_capture_mode不能直接case,为了保证occ的输出是fast_clock,可以case在occ的clkoutmux的S端。

3.STA该分为几个mode进行signoff比较合理?

答:一般有scanhscapture、scanlscapture、scanshift、func、mbist五个sta mode,其中mbist mode时钟与function几乎一致,可以将mbist和func合并。而repair mode和boundary scan需要用到ijtag_tck和ref_clk(慢速时钟的时序比较宽松),可以合并到func mode。Scanhscapture和scanlscapture时钟来源不一样,不建议合并;scanhscapture和func路径大部分重合但是时钟同异步关系可能不一样(和signoff策略相关),部分时序路径也不一样(dft路径和func路径不一样),不建议合并;scanshift和scanlscapture时钟来源一样但是走的路径不同(SI/D),虽然都是慢速时钟,但合并后会有太多虚假路径,不建议合并。

4.sta中为什么要set_false_path?

答:由于design中包含了function路径和dft路径,在signoff阶段很难通过sdc将二者完全区分开来。例如在dft scanhscapture mode下经常能够看到经过memory的时序路径,但是scanhscapture是检查寄存器之间的路径,不涉及到经过memory的时序路径;此时就需要通过sdc来去掉这些虚假的路径,可以通过set_false_path的方式让工具不去检查,也可以通过set_disbale_timing的方式等等,只要达成目的即可。

八、DFT plan

1.当拿到一颗芯片时,如何开展DFT规划?

答:首先针对芯片工艺、面积、用途可以大致规划DFT覆盖率和良率要求,之后便可以开始规划应用哪些DFT技术例如mbist、scan、repair、bscan、sharebus、ram_seq、wrapper、test_point等等,确认好之后需要知道IO数量和分布,以此来规划DFT IO复用。DFT方案确认好之后就是各种细节制定例如mem group、chain_balance、io group等等,视项目具体情况而定。

2.dft有哪些时钟,分别有什么作用?

答:dft总共有ijtag_tck、test_clock(scan_clock),func_clock。其中ijtag_tck是ijtag网络专用时钟,test_clock是scanshift和scanlscapture时钟,func_clock是复用的function 高速时钟,用来测试mbist和scanhscapture。

Part.05

课程报名微信,扫描咨询我们吧

景芯SoC芯片全流程实战附属【知识星球】,一个包括设计、验证、DFT、后端全流程技术的交流平台,也是景芯学员的答疑平台!若您和我一样渴求技术,那欢迎扫下面二维码加入星球,共同进步!

夜雨聆风

夜雨聆风