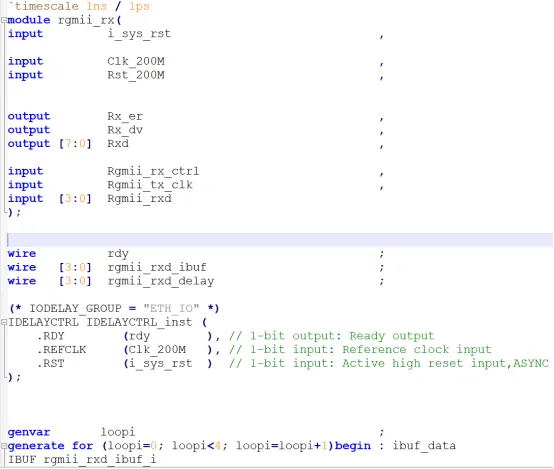

Xilinx IDELAY2使用说明

各位小伙伴在FPGA设计中一定遇到过需要输入的多条数据线与随路时钟对齐的情况。为了解决这一问题,xilinx向用户提供了IDELAYE2模块,可以用来调整数据与时钟之间的相位关系。下面我们将对IDELAYE2如何使用做出说明。

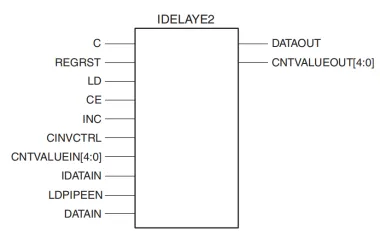

1、IDELAYE2模块

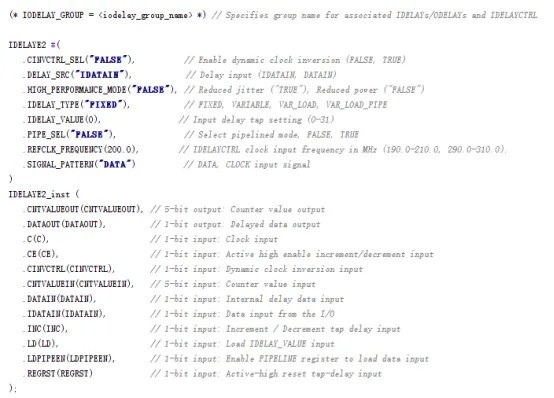

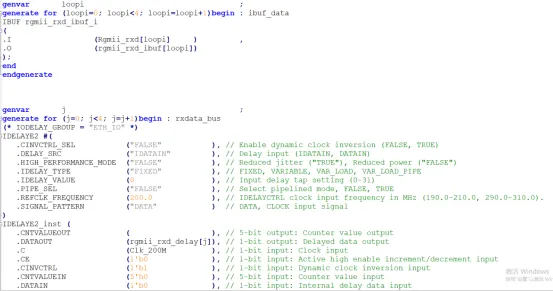

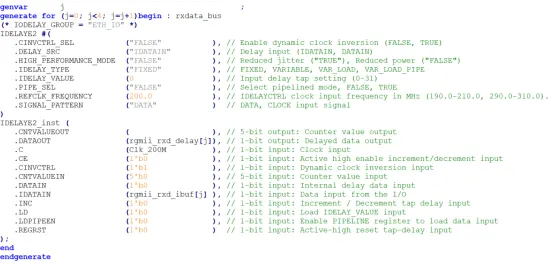

模块接口如上图所示,调用原语如下所示:

首先为大家介绍一下原语调用时各个属性和接口的含义:

1)、属性

IDELAY_TYPE :用于设置模块工作模式,分为四种:

|

属性 |

含义 |

|

FIXED |

延时为固定值,通过延时值IDELAY_VALUE属性设置,一旦配置完成不能改变 |

|

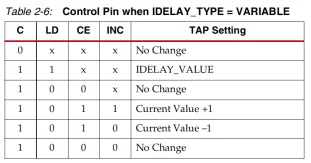

VARIABLE |

需要通过LD将IDELAY_VALUE初始值加载,延时值可通过CE、INC信号进行增减 |

|

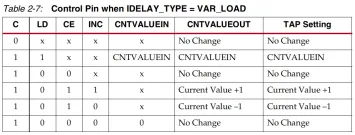

VAR_LOAD |

需要通过LD将CNTVALUEIN信号表示的初始值加载,延时值可通过CE、INC信号进行增减(LD有效时CNTVALUEIN必须是稳定的) |

|

VAR_LOAD_PIPE |

需要通过LDPIPEEN将CNTVALUEIN信号表示的初始值先放置在Pipeline寄存器,当LD有效时将Pipeline寄存器加载,延时值可通过CE、INC信号进行增减(此模式下CNTVALUEIN值可以预先写入,相隔一段时间LD有效加载延时值) |

IDELAY_VALUE :用于设置延时初始值,范围为0-31,默认值为0。(VAR_LOAD 和VAR_LOAD_PIPE模式下此属性无效)

HIGH_PERFORMANCE_MODE:设置为TRUE时,会减少信号抖动,但是会增加模块功耗。

SIGNAL_PATTERN :时钟信号与数据信号具有不同的电气特性,因此在通过IDELAY链时会累积不同程度的抖动。通过设置 SIGNAL_PATTERN 属性,用户可让时序分析器在计算时序时恰当地考虑抖动效应。模块处理的是DATA信号时,此属性设置为DATA,模块处理的是DATA信号时,此属性设置为CLOCK。

DELAY_SRC:选择输入数据来自端口IDATAIN还是DATAIN。

REFCLK_FREQUENCY:设置参考时钟频率,频率范围原语模块后面注释有标注。

CINVCTRL_SEL:是否允许通过外部引脚CINVCTRL来动态翻转控制时钟(C)的极性。

PIPE_SEL:VAR_LOAD_PIPE模式时设置为TRUE。

2)、引脚

IDATAIN:模块输入,信号源来自IOB;

DATAIN:模块输入,信号源来自FPGA逻辑;

DATAOUT :IDATAIN或DATAIN经过延时处理后的输出,可以驱动到ILOGICE2/ISERDESE2 或者ILOGICE3/ISERDESE2以及FPGA逻辑;

C:参考时钟,所有控制信号(REGRST, LD, CE,INC) 与它都是同步的。

LD:延时值加载信号,高有效,使用在IDELAY_TYPE属性介绍已经讲过。

CINVCTRL:时钟极性翻转信号,有效后两个时钟周期IDELAYE2模块不能使用。

CNTVALUEIN:用于动态加载延时值。

CNTVALUEOUT:表示当前延时值为多少。

LDPIPEEN:高有效,将CNTVALUEIN信号表示的初始值先放置在Pipeline寄存器。

REGRST:高有效,将Pipeline寄存器复位为0。

CE, INC:用来增减当前延时值。

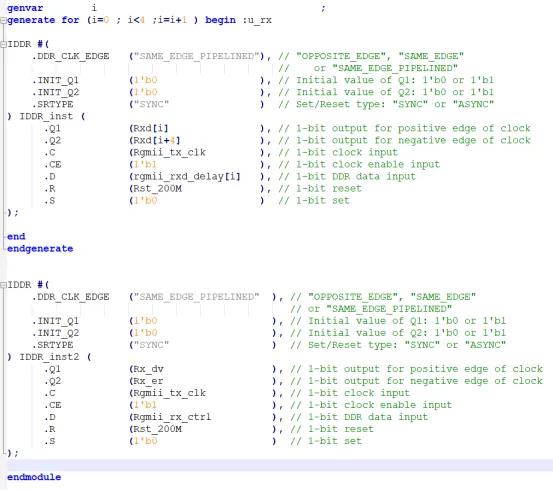

介绍完毕后,那么我们现在举一个例子,在千兆网 RGMII 接口中我们常常会用到IDELAYE2来调整时钟和数据之间的相位关系,故以此为大家举例:

这就是一个完整的千兆网的接收端数据延时采样的程序,这里使用的为FIXED模式。

大家阅读过程中有什么问题欢迎留言。

夜雨聆风

夜雨聆风