重要提示:推文由公众号编译,可能存在技术或者翻译错误,仅供读者参考。原文地址:https://ieeexplore.ieee.org/document/11150547 内容梗概: 1)研究问题:①在传统的混合型DCX拓扑(如SC-SRC)中,开关电容单元和变压器单元各自拥有独立的谐振腔,导致电路中存在多个离散的磁元件(如谐振电感 2)文章亮点:①通过电流环耦合的方式,将SC单元和变压器单元的谐振腔合并为一个共享谐振腔,实现了两个独立谐振腔的融合,为后续磁元件的全集成创造了条件。②针对三绕组耦合变压器,建立了一种双漏感模型,将两个谐振电感分别对应于两个原边绕组的漏感,从而实现了谐振电感和变压器的磁集成,简化了电路分析和设计。③设计了具有6个边柱和1个中心柱的矩阵变压器,采用平面磁芯和分数匝PCB绕组,将同步整流器和输出电容集成在变压器结构中,支持150A高输出电流,提升了功率密度。 |

1、研究背景

以ChatGPT为例,人工智能生成内容的THE出现引发了计算基础设施扩展和升级的全球趋势。平均而言,处理单个ChatGPT查询的能耗大约是典型谷歌搜索的十倍。这一差异在于数据中心的功耗和成本即将发生巨大变化。据估计,到2030年,数据中心的电力需求将激增160%。这种快速增长也加速了数据中心电力架构从传统的12 V总线向更高效的48 V总线电力系统的过渡。 然而,考虑到四倍的电压转换负担,这种转变在设计用于48 V到负载点(PoL)电源转换的电压调节模块(VRM)方面带来了挑战。

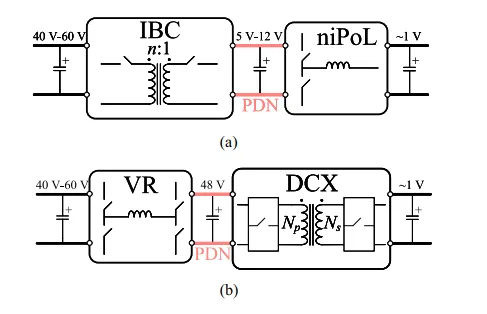

两级架构是48v VRMs的首选解决方案,因为它的解耦设计将稳压级与固定比降压级分开。两种常见的实现是中间总线体系结构(IBA)和因数化电源体系结构(FPA)。如图1(a)所示,IBA包括前端中间总线转换器(IBC)和多个非隔离PoL调节器(niPOLs,典型的多相降压拓扑)。IBC将48v输入降压至12v, niPoLs进一步将12v降压至特定负载电压。然而,在大功率负载附近放置大电流稳压器(VR)需要大量的niPOL来支持高功率。此外,niPoL阵列中12v到sub- 1v的转换受到占空比限制。

图1.两阶段架构(a)IBA (b)FPA

另外,FPA具有多种优势,包括降低输电网络损耗,增强高中压下的能量存储,改善占空比和可扩展的输出电流。FPA由VR和无规直流变压器(DCX)组成。前端VR将变化的输入电压(例如,40 V - 60 V)调节到稳定的母线电压(通常为48 V),而DCX将这48 V降至1 V,用于终端负载,如图1(b)所示。然而,由于极高的电压转换比(48:1)和大输出电流(> 100A),DCX设计变得具有挑战性。

通常,DCX设计可以分为两大类:基于开关电容(SC)的解决方案和基于变压器的解决方案。基于SC的DCX,通过采用大量开关来实现高降压比,这增加了电路复杂性和成本。相比之下,基于变压器的DCX更适合高压转换比(HVCR)和大电流场景。其中,LLC DCX由于其出色的软开关特性而广受欢迎。为了进一步提高LLC DCX的性能,已经提出了各种磁集成技术,包括定制的矩阵变压器设计和分数匝绕组。然而,设计高匝数比和大负载电流的HVCR变压器仍然具有挑战性。

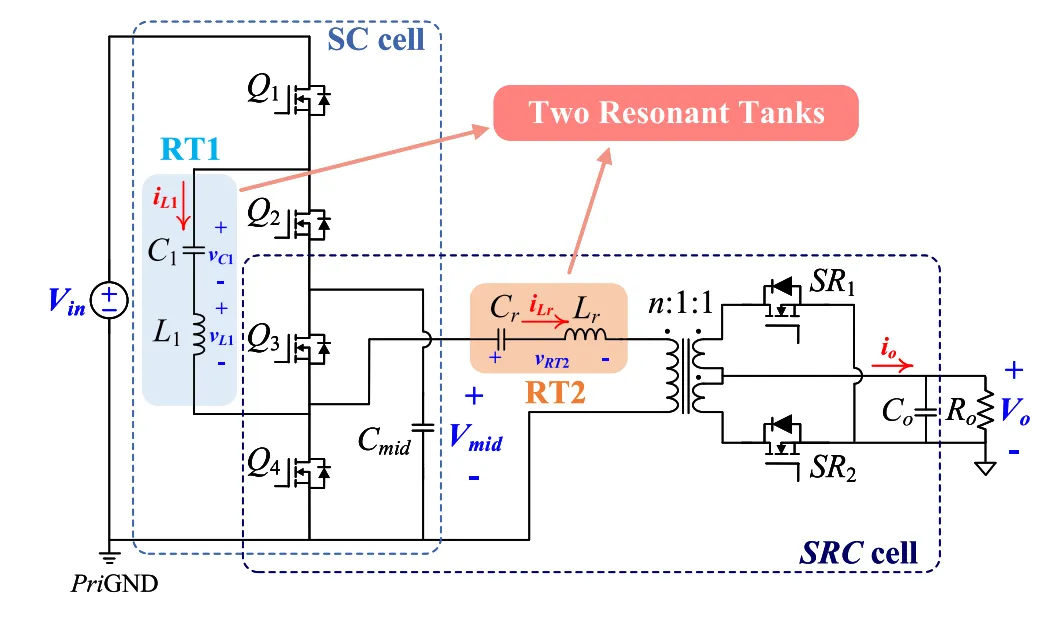

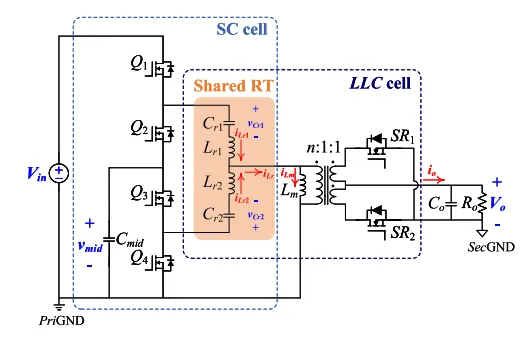

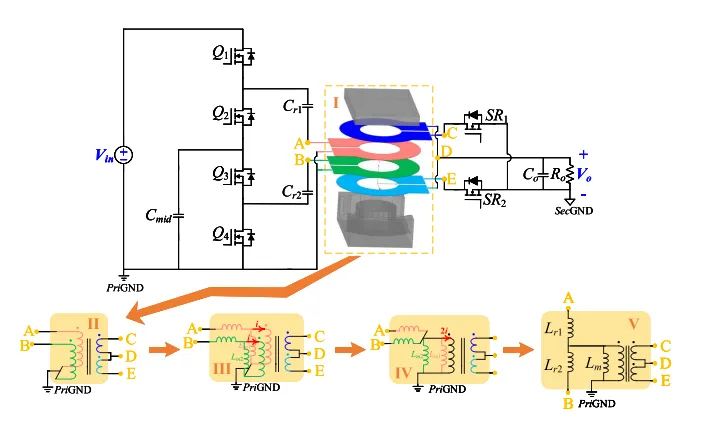

作为一种有前途的替代方案,混合DCX拓扑结合了SC电池和基于变压器的电池,适用于HVCR应用。这些解决方案充分利用了简化变压器设计、降低匝比和低压开关优于高压开关的优点。图2显示了混合开关电容器和串联谐振变换器(SCSRC)的原理图。它仅使用n:1匝比变压器就实现了4n:1的电压转换比,并且在初级开关上保持相对较小的电压和电流应力。这些特性使其成为FPA中DCX的一个有吸引力的候选者。然而,与传统的LLC或SRC设计相比,SC电池中包含了一个额外的谐振槽,这给磁集成设计带来了新的挑战。

在本文中,我们提出了一种优化的混合DCX拓扑来解决这些挑战。所提出的拓扑结构通过电流环耦合将上述混合DCX中两个谐振槽的工作状态连接起来,然后通过在SC单元和基于变压器的单元之间共享谐振槽来实现完全集成的磁性。建立了双漏感模型,简化了电路分析和设计,便于印制电路板(PCB)绕组布局的实现。此外,设计了一种具有PCB绕组、同步整流器(SRs)和电容器异质集成的矩阵变压器,以提高功率密度并支持高负载电流。

2、基于共享谐振槽的开关电容器和LLC变换器(SRT - SCLLC)

在混合拓扑中,如图2所示,SC和SRC单元都有独立的谐振槽。尽管SRC单元中的谐振电感Lr可以利用泄漏电感集成到变压器中,但整个变换器仍然包含两个不同的磁性元件:电感L1和集成泄漏电感的变压器。多个分立磁性元件的存在不仅降低了整体功率密度,而且还需要对每个元件进行单独优化,这可能会损害性能并增加硬件成本。

为了解决这些限制,本研究旨在开发基于该拓扑结构的一体化磁集成设计,利用其在高降压条件下实现低匝比的优势,同时简化磁设计过程。具体来说,通过耦合电路中所有磁性元件的工作状态,这种方法可以实现离散磁性元件的完全集成。这一举措不仅简化了磁性设计过程,而且具有显着提高效率和功率密度的潜力。

图2.混合SCSRC

A.拓扑推导

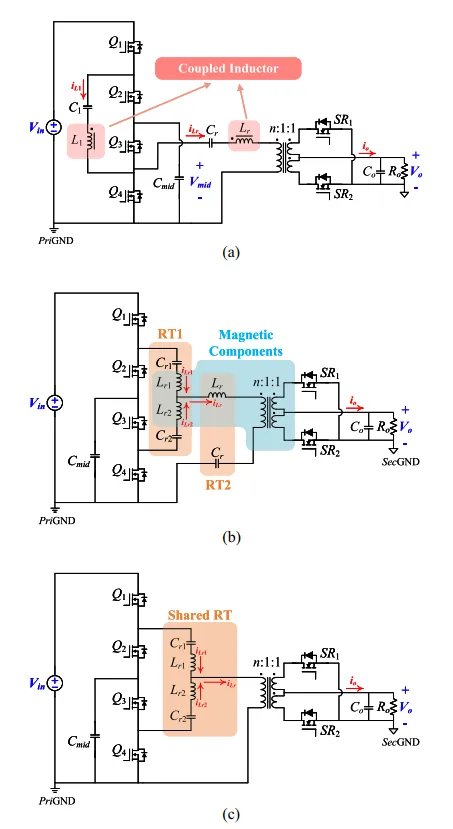

为了实现两个谐振槽中磁性元件的集成设计,关键在于耦合它们的工作状态。主要的耦合方法可以分为两种方法:磁通量耦合和电流环耦合。

从理论设计的角度来看,磁通量耦合可以通过将L1和Lr构建为耦合电感来实现,如图3(a)所示。然而,在实际实现中,Lr通常作为变压器的漏感来实现,这使得与L1的有效耦合设计具有挑战性。实现精确耦合需要复杂的磁路和额外的铁心腿,增加铁心体积并降低功率密度,从而限制了磁集成的好处。直接磁耦合是将变压器插入SC电池的谐振槽中。然而,直接将变压器集成到SC槽中会导致堆叠桥LLC结构。这从根本上改变了原始SC电池的电荷转移和工作原理,并中和了其电流应力降低的好处。

图3.拓扑派生 (a)带磁通耦合的SCSRC (b)电流环耦合的SCSRC (c)带有共享谐振槽的SCSRC

另一种方法是电流环耦合,如图3(b)所示。在该拓扑中,谐振槽1 (RT1)被分成两个完全对称的支路,这些支路之间的中点连接到谐振槽2 (RT2)的一端,从而耦合了两个谐振槽的电流回路。由于RT1中上下支路的对称设计,使得两个支路的谐振状态保持一致,并且它们的电流总和始终等于RT2中的电流。在这种配置下,RT1可以等效地建模为与RT2处于相同谐振状态的单个谐振槽。此外,由于RT1和RT2是串联的,因此可以在不影响整个电路运行的情况下去除RT2。得到的等效电路如图3(c)所示。通过上述拓扑推导和优化,SC电池和SRC电池的谐振槽最终实现了共享,为后续磁性元件的全面集成创造了有利条件。

然而,耦合谐振槽RT1和RT2后,在零电压开关(ZVS)过程中,SRC单元不再与SC单元解耦。这将导致在死区时间内电路行为的显著变化。与SCSRC拓扑结构不同的是,在新的拓扑结构中,来自RT1两个支路的电流汇聚形成变压器的磁化电流,不可避免地在变压器内部引入循环电流。

图4.所提出的SRT-SCLLC

为了保证开关的软开关工作,必须设计合适的变压器磁化电感Lm。更新后的拓扑如图4所示,命名为基于共享谐振槽的SC和LLC转换器(SRT - SCLLC)。值得注意的是,SRT-SCLLC保留了原有SCSRC拓扑结构的主要优点,即高降压比、低匝数比和低开关应力。因此,它非常适合于高降压、高功率密度的应用,例如数据中心中的48v到1v转换器。

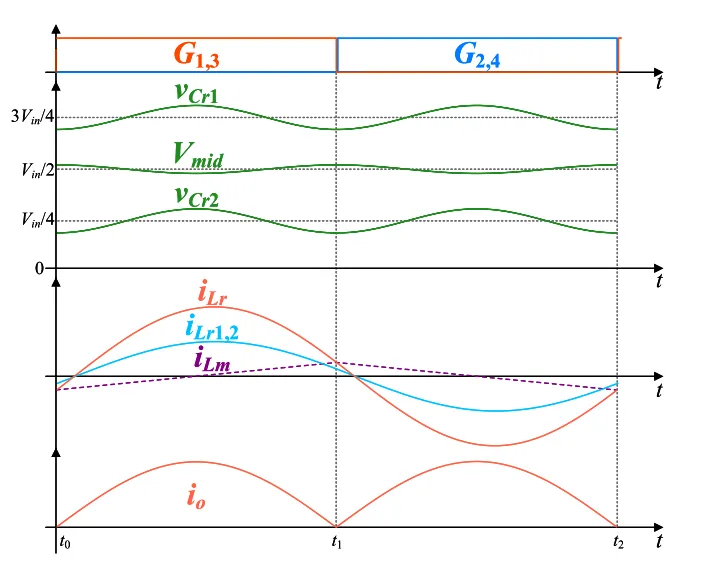

图5.所提出的变换器在稳态时的理想开关波形

理想稳态波形如图5所示。忽略死区时间,存在一对互补的栅极信号,占空比为50%:栅极信号  用于

用于  和

和  ,而栅极信号

,而栅极信号  用于

用于  和

和  。开关频率调谐至谐振腔的谐振频率,以确保最佳效率。在开关电容单元中,RT 和

。开关频率调谐至谐振腔的谐振频率,以确保最佳效率。在开关电容单元中,RT 和  的直流偏置均为

的直流偏置均为  ,而

,而  和

和  的直流偏置分别为

的直流偏置分别为  和

和  。谐振电流

。谐振电流  相同,且等于

相同,且等于  的一半。

的一半。

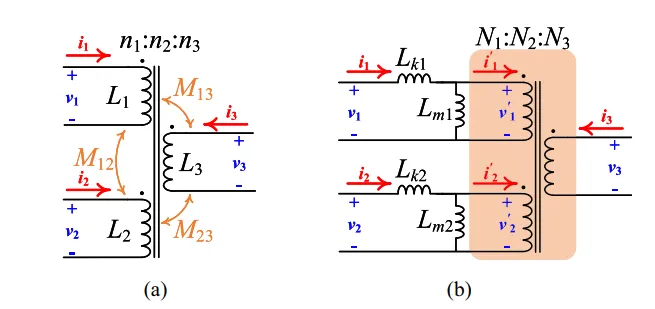

B.双漏感模型

两个谐振槽在SCSRC拓扑结构中的耦合和合并操作为实现新的SRT - SCLLC拓扑结构的全磁集成提供了基础。本文提出了一种具有双漏感的三绕组变压器模型,其中两个谐振电感Lr1和Lr2可以利用变压器的漏感进行集成。本节详细介绍双漏感模型的推导过程。

图6.变压器模型 (a)三绕组耦合变压器 (b)双漏感模型

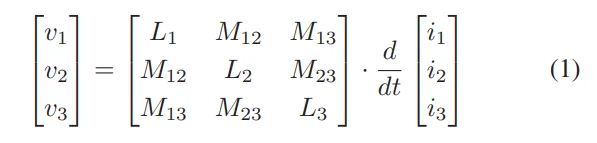

首先,两个谐振电感需要连接到两个不同的初级绕组,而中心抽头的次级绕组可以用单个全波绕组代替,以简化分析。因此,采用匝数比为n1:n2:n3的三绕组耦合变压器,如图6(a)所示。Ln (n∈{1,2,3})表示第n个绕组的自导度。它们之间的互感分别为M12、M23、M13。耦合关系的电感矩阵可以表示为:

其中vn是绕组n两端的电压,in是流入绕组n虚线端的电流。

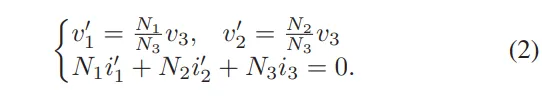

当使用有限元分析(FEA)工具(例如ANSYS Maxwell)设计变压器时,提取的结果通常是全电感矩阵的形式,它不直接分离每个初级绕组的漏感。为了简化电路运行的分析,三绕组耦合变压器可以解耦为双漏感模型。图6(b)说明了解耦的双漏感模型,由两个漏感、两个磁化电感和一个N1:N2:N3的理想变压器组成。理想变压器初级侧绕组两端的电压为vn,而流入变压器初级侧绕组的电流为in。根据理想变压器的基本原理,电压和电流的数学关系可以表示为:

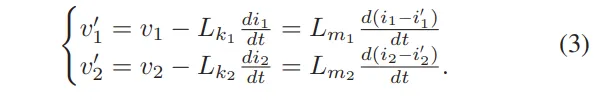

将基尔霍夫电压定律(KVL)应用于两个初级绕组可以得到:

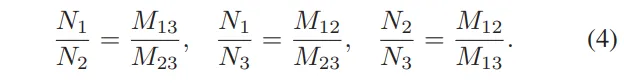

基于由(1)-(3)导出的数学关系,匝数比可以用磁化电感表示为:

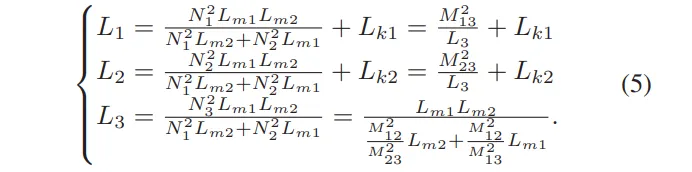

漏感和励磁电感可以由耦合电感的自感和互感导出如下:

为了直观地理解双漏感模型的实际连接,具有EI铁芯和四层PCB绕组的双漏感变压器的实际示例如图7所示,应用于所提出的SRT-SCLLC拓扑。模型I对应于实际PCB绕组模型。中间层(红色和绿色)代表初级侧绕组。这些绕组中的每一个的一个端子连接到初级侧接地(PriGND),而另一个端子连接到串联谐振电容器。顶层(深蓝色)和底层(浅蓝色)分别代表次级侧绕组。每个次级绕组的一个端子连接到输出Vo,而另一个端子连接到两个SR的漏极。

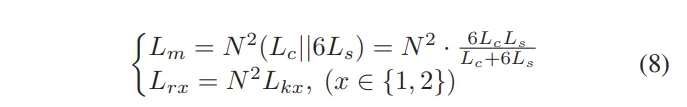

模型I的电路模型是一个三绕组耦合模型,对应于图7中的模型II。接下来,模型III说明了解耦的双漏感模型。由于两个初级侧绕组共享一个公共接地并且具有相同的匝数比,它们可以组合成一个电流加倍的等效绕组。因此,磁化电感Lm1和Lm2有效地并联,导致模式IV中的等效电路。这两个电感可以进一步组合成一个等效磁化电感Lm=Lm1||Lm2,如模型V所示,它与图4中的电路相匹配。

图7 应用于SRT-SCLLC的双漏感变压器的实际示例

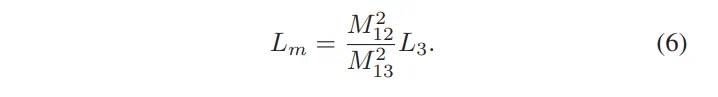

在这种特殊情况下,由于对称结构,M13可以被认为等于M23。然后,磁化电感,记为Lm,可以简化为:

因此,双漏感模型可以解耦磁化电感和与每个初级绕组相关的漏感,并且实际上有利于设计谐振参数,促进磁性设计和优化过程。

3、异构集成平面变压器设计

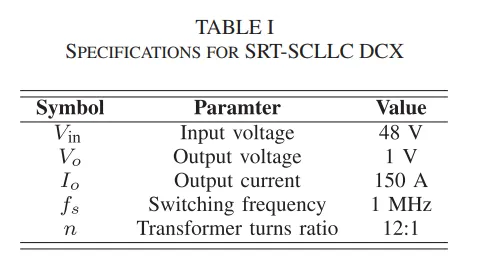

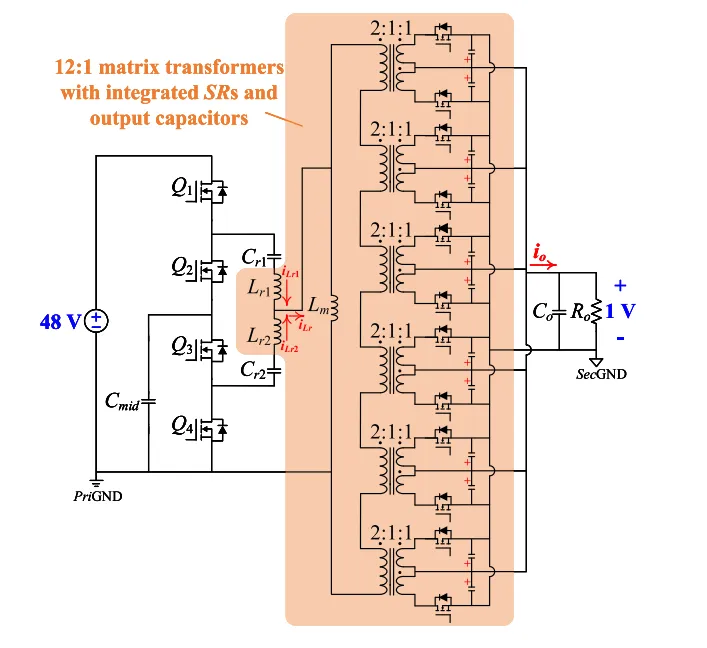

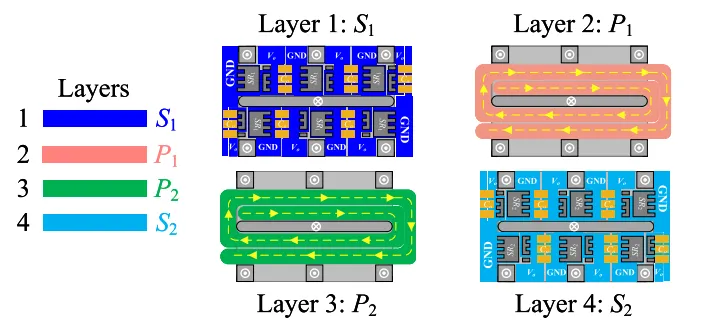

基于上述分析,所提出的SRT-SCLLC变换器非常适合用作需要HVCR的DCX。表1总结了所需SRT-SCLLC DCX的规格。标称输入电压为48 V,输出电压为1 V,负载电流为150 A。由于负载电流高,变压器次级侧绕组设计为一匝。因此,变压器匝数比n是一个整数,等于初级侧绕组的匝数。在本设计中,变压器采用六个相同的子变压器,每个子变压器的传输比为2:1,只有12:1的总匝数比才能达到48:1的电压转换比。

图8显示了所提出的集成SRs和输出电容的矩阵变压器的原理图。谐振电感Lr1和Lr2代表变压器的漏感,而Lm是磁化电感。为了支持高输出电流和提高功率密度,这些变压器的设计中采用了平面磁芯和分数匝PCB绕组。变压器的布局如图9所示。磁芯由六个侧腿和一个中心腿组成。PCB的顶层和底层用于二次绕组,而中间两层用于一次绕组。每个一次绕组层都有两个绕组缠绕在中心腿周围。围绕中心支腿的次级绕组的全匝分为六段,在分数匝次级绕组上分布有六组SRs和输出电容,形成六种中心抽头全波整流结构,在正半周期间,底部SRs全部导通,而在负半周期间,顶部SRs全部激活。

图8.具有异构集成矩阵变压器的48 V-1 V SRT-SCLLC示意图

图9 异质集成矩阵变压器的PCB布局

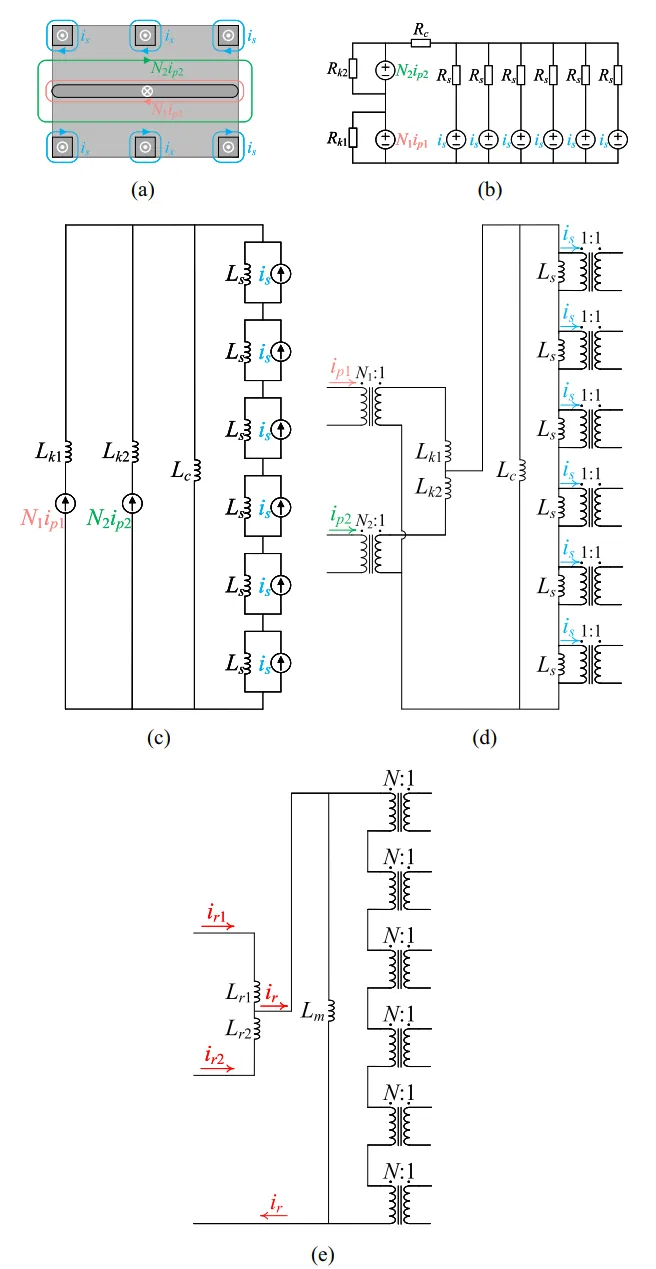

A.基于磁路的等效电路建模

图10(a)显示了正半周期内的电流回路。围绕中心磁柱有两个原边绕组电流回路,围绕每个边柱有六个副边绕组电流回路。 和

和  分别表示第

分别表示第  个原边绕组的匝数和电流(

个原边绕组的匝数和电流( ,且

,且  )。由于副边整流器的并联结构,所有副边电流均表示为

)。由于副边整流器的并联结构,所有副边电流均表示为  。

。

相应的磁路模型如图10(b)所示。Rc为中心腿的磁阻,Rs为侧腿的磁阻。Rkx为第x次初级绕组的漏磁阻,对应第x次初级绕组与其他绕组之间的漏磁通径。在该模型中忽略了与整个铁心外漏磁相关的外磁阻。

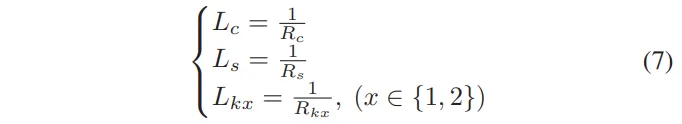

磁路模型可以通过拓扑对偶性转换成等效电路模型,如图10(c)所示,在这种转换中,磁动势被转换成电流源,电感是磁阻的倒数,表示如下:

其中Lc是中心支路电感,Ls是侧支路电感,Lkx是从次级侧观察到的漏感。

为建立绕组与电路中其他元件之间的连接,电流源用理想变压器代替,此电路可进一步转化为等效电路,如图10(d)所示,一次电流N1ip1和N2ip2分别用匝数比为N1:1和N2:1的理想变压器代替,二次电流is用匝数比为1:1的理想变压器代替。

如图10(e)所示,在N1=N2=N的条件下,通过将所有电感推到初级侧并合并变压器,可以导出一个简化的等效电路模型。这个最终的等效电路模型对应于II-B节中定义的双漏感变压器模型。因此,磁化电感Lm是侧腿电感Ls和中心腿电感Lc的组合,谐振电感Lr1和Lr2分别对应漏感Lk1和Lk2。

其中N=2在这个设计中。

图10 双漏感变压器的等效电路建模 (a)设计了带电流回路的铁心结构 (b)磁路 (c)带电流源的电路 (d)带理想变压器的电路 (d)带双漏感变压器的最终电路

B.优化和模拟

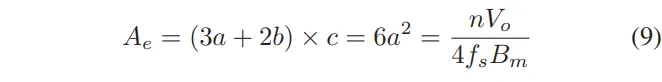

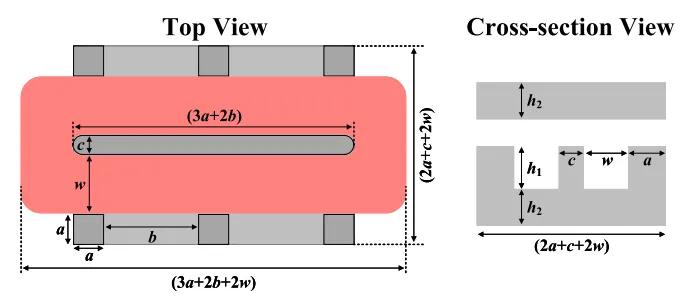

设计的矩阵变压器的尺寸优化对于在所提出的DCX中实现高效率和高功率密度至关重要。主要目标是平衡变压器的损耗和占用空间。在本设计中,选择了DMEGC提供的高频磁性材料DMR51 W,用于在1 MHz开关频率下工作。磁芯由六个侧腿和一个中心腿组成,其尺寸在图11中参数化。侧腿的横截面积假定为边长a的正方形。b代表相邻侧腿之间的距离。它由SRs和输出电容器的封装尺寸决定,因为它们集成在PCB绕组中。中心腿的尺寸可以估算为长×宽为(3a+2b)×c的矩形,中心腿的截面积等于芯的有效截面积,也等于侧腿的六倍,可以计算为:

其中Bm为峰值磁通密度。w为绕组宽度。h1为窗口区域的高度,由PCB板、SRs、输出电容的厚度决定。顶板和底板的厚度取决于岩心的有效截面积。

图11 核心尺寸图

因此,变压器的总占地面积为:

在这个表达式中,只有参数a和w是优化铁心结构和功率损耗的可调变量。变压器的铁心损耗和绕组损耗可以分别通过Steinmetz方程和Dowell模型进行评估。

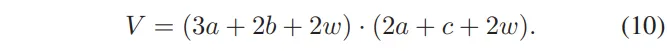

图12(a)显示了变压器总损耗轮廓线随边腿长度a和绕组宽度w而变化,不同占地面积的最佳损耗由交叉点表示。这些点在图12(b)中重新绘制。为了在效率和功率密度之间取得平衡,最佳设计点确定在占地面积为448 mm2和总损耗为8.2 W。在这种情况下,a和w分别为2.4 mm和4.1 mm。

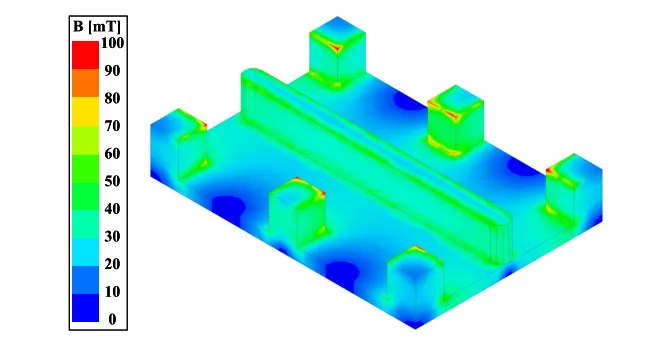

开发了ANSYS Maxwell 3-D模型来分析和验证变压器的设计铁心结构。基于II-B节中提出的双漏感模型,模拟的漏感和激磁电感分别为60 nH和3.1795μH。如图13所示,观察到设计铁心中的磁通分布是对称和平衡的。

图12 (a)损耗和占地面积轮廓线,具有不同的侧腿长度a和卷绕宽度w (b)损耗与占地面积

图13 设计的堆芯结构的磁通分布

C.谐振罐的设计注意事项

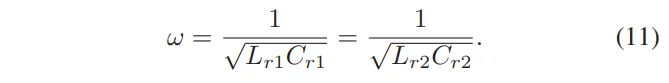

在理论分析中,假设共享谐振储能器中的两个谐振支路是对称的,并携带相同的电流。然而,支路之间谐振参数的任何不匹配都可能导致不平等的电流共享,从而导致初级侧器件上的不平衡电流应力和热分布。由于转换器在谐振下工作,通过确保两个储能器之间紧密匹配的谐振频率,可以在稳态条件下保持相等的电流共享。从数学上讲,这需要谐振储能器之间的阻抗匹配。

为了确保阻抗匹配,需要几个设计考虑来确保谐振支路的对称性并最大限度地减少失配。首先,两个初级绕组在同一中心芯腿上缠绕相同的PCB布局。这种方法有助于确保两个初级绕组的漏感尽可能保持一致,最大限度地减少源端的失配。另一方面,在实践中不可避免地出现漏感偏差的情况下,可以稍微调整谐振电容器的值以补偿失配。这确保了两个谐振槽达到相同的谐振频率。

图14 提议的SRT-SCLLC的原型

4、结论

在本稿件中,提出了一种基于SCSRC的改进的混合DCX拓扑以实现全磁集成,称为基于共享谐振槽的SCLLC,该拓扑通过电流环耦合将SC单元和基于变压器的单元中的两个谐振槽合并,并且该修改为离散磁元件的全集成创造了有利条件,构建了变压器的双漏感模型,以便于在实际工程应用中实现这种集成磁设计。此外,设计了一个基于双漏感模型的12:1矩阵变压器,为SRT-SCLLC DCX实现48:1的电压转换比。为了支持高输出电流和提高功率密度,变压器设计中采用了平面磁芯和分数匝PCB绕组。

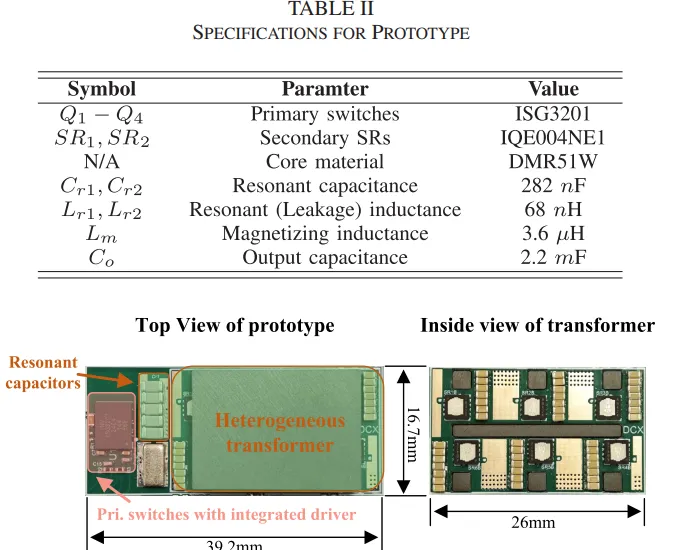

一个具有完全集成磁学的1 MHz、48 V输入、1 V/150 A输出硬件原型已经成功实施和测试。实验结果不仅验证了dual-leakage-inductance-based变压器的功能,仅用四层PCB就实现了93.8%的满载效率。这项工作展示了所提出的DCX拓扑在满足48 V总线数据中心电力系统中HVCR苛刻要求方面的巨大潜力。

公众号发布内容仅限于国内外研究前沿荐读,不产生任何经济效益,如有侵权请私信本公众号删除。 |

夜雨聆风

夜雨聆风