掩模板(PhotoMask)——芯片图案的母版,半导体制造中成本最高的消耗材料之一

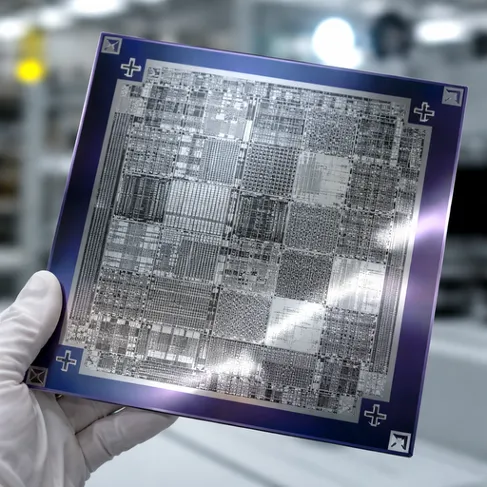

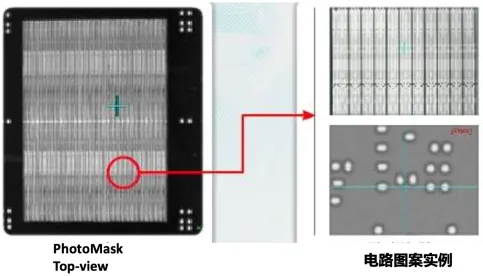

在半导体光刻工艺中,掩模板(PhotoMask/Reticle)的作用类比于传统摄影的底片——芯片设计图案首先被精确写入掩模板,再通过光刻机将掩模板图案缩小投影到晶圆上重复曝光,在每颗Die上形成一致的电路图案。掩模板质量直接决定了芯片图案精度和良率。

•价格极高:EUV掩模单张成本约50~150万美元;一套先进节点掩模组(100~200张)成本达500~1000万美元

•技术垄断:EUV Blank Mask超低热膨胀基板由HOYA/AGC/Schott垄断;EUV掩模AIMS验证设备全球仅Zeiss独供;掩模缺陷检测KLA约占90%市场

•良率放大效应:掩模上任何一个可打印缺陷,都会在晶圆上每颗Die同位置复制——一个掩模缺陷等于批次性良率崩溃

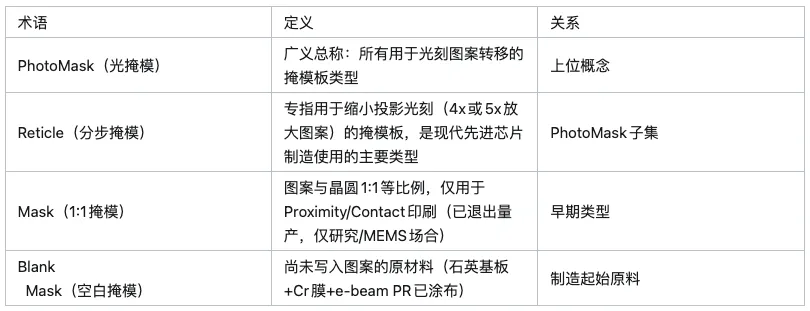

•EUV掩模革命:从DUV透射型转变为反射型(Si/Mo多层膜反射镜),带来全新制造、检测和Pellicle挑战

▌ 本文目录

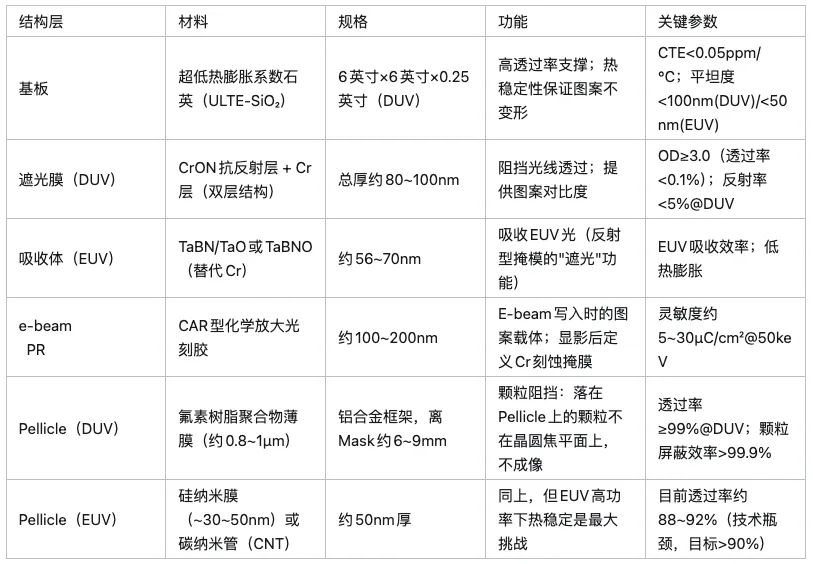

MSK-1 PhotoMask基本定义与结构:石英基板 + Cr遮光膜 + Pellicle

MSK-2 透射型掩模(DUV)vs 反射型掩模(EUV):物理机制与结构差异

MSK-3 图案转移方法演进:Contact / Proximity / Stepper / Scanner

MSK-4 Scanner(Step & Scan)工作原理与投影光学系统深度解析

MSK-5 分辨率方程 R=K1×λ/NA 与四大RET(分辨率增强技术)

MSK-6 OPC(光学邻近效应修正):光学失真的预补偿工程

MSK-7 PSM(相移掩模):利用干涉相消实现分辨率突破

MSK-8 PhotoMask完整制造流程:从Blank到Pellicle封装的10道工序

MSK-9 掩模板质量管控:CD测量 · 缺陷分类修复 · Registration检测

[MSK-1] PhotoMask基本定义与结构:石英基板 + Cr遮光膜 + Pellicle

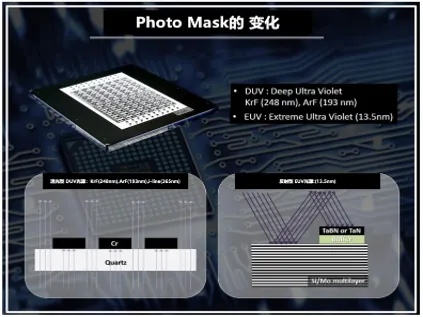

▌一、PhotoMask的术语层级

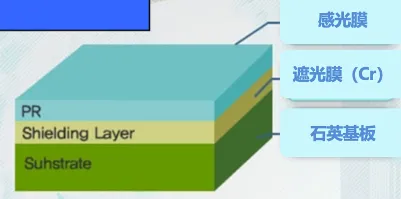

▌二、PhotoMask的物理结构(DUV标准版)

【PhotoMask截面结构图 — 从下到上:ULTE石英玻璃基板(6英寸×6英寸×0.25英寸,CTE<0.05ppm/°C);Cr遮光膜(CrON抗反射层+Cr层,总厚约80~100nm);e-beam光刻胶(制造过程中使用,完成后去除);顶部:Pellicle保护膜(铝合金框架+聚合物薄膜,离Mask表面约6~9mm)】

EUV Pellicle是当前整个EUV产线最大的未解工程难题之一——EUV光子能量是ArF的14倍,会加热Pellicle薄膜(即使只吸收10%也会使50nm薄膜温度骤升),导致变形甚至破裂。台积电、三星、英特尔均在部分关键层次采用无Pellicle方案(靠频繁检测和清洗维持质量),这是EUV产线产能低于理论值的重要原因之一。

[MSK-2] 透射型掩模(DUV)vs 反射型掩模(EUV):物理机制与结构差异

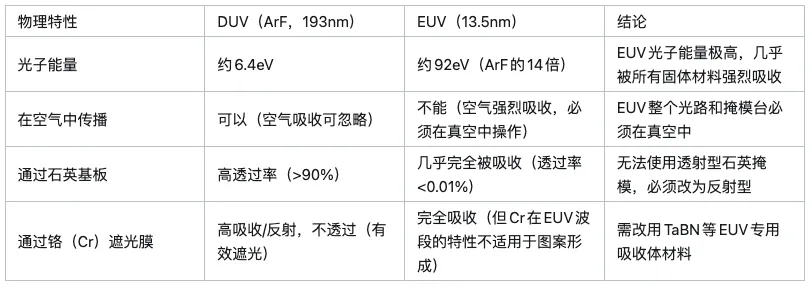

▌一、为什么EUV必须用反射型掩模?

▌二、EUV反射型掩模的结构详解

【EUV反射型掩模截面图(从下到上):LTES超低热膨胀基板(CTE约0~0.005ppm/°C);背面导电层(Cr,用于静电夹持);40对Si/Mo多层反射膜(ML:Mo约2.8nm + Si约4.2nm,周期约7nm,40周期总厚约280nm,峰值反射率约67~70%@13.5nm);Ru缓冲层(约2~3nm,保护ML在检测修复时不被损伤);TaBN/TaBO吸收体图案(约56~70nm,图案化后形成电路图案——有图案处EUV被吸收,无图案处EUV被ML反射);顶部可选EUV Pellicle(Si或CNT薄膜,约50nm)】

⚠️ EUV Blank Mask的核心供应商全球仅有三家:HOYA(日本,市占约60%)、AGC旭硝子(日本,约30%)、SCHOTT(德国,约10%)。任何一家供货中断,将直接波及全球所有EUV光刻产能。中国大陆目前无法自产满足EUV规格的Blank Mask基板材料,且受出口管制影响,这是当前整个半导体产业链中最脆弱的单点故障之一。

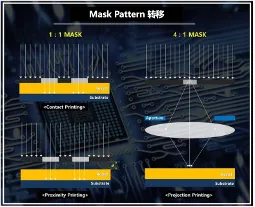

[MSK-3] 图案转移方法演进:Contact / Proximity / Stepper / Scanner

▌一、三代图案转移技术对比

▌二、4x/5x缩小投影的工程优势

•制造容差放大4x/5x:掩模上图案是晶圆目标尺寸的4~5倍,E-beam写入误差容限同比放大,大幅降低掩模制造难度

•缺陷自然过滤:小于投影成像系统分辨率下限的掩模缺陷不会在晶圆上成像,等效提高缺陷容忍度

•高通量:一张掩模可在整张晶圆上重复步进曝光数百次(每次一个Die区域),生产效率高

•MEEF(掩模误差增强因子):掩模CD误差被成像系统放大约2~4倍印到晶圆上;MEEF是掩模CD规格的核心约束之一

工程换算要点:现代光刻机使用的Reticle(掩模)图案比晶圆最终图案大4倍(4x缩放)。当工程师说"掩模CD = 100nm"时,对应晶圆实际CD = 25nm(4x缩小)。掌握这个换算关系,是解读掩模规格与晶圆工艺规格之间转换的基础。

[MSK-4] Scanner(Step & Scan)工作原理与投影光学系统深度解析

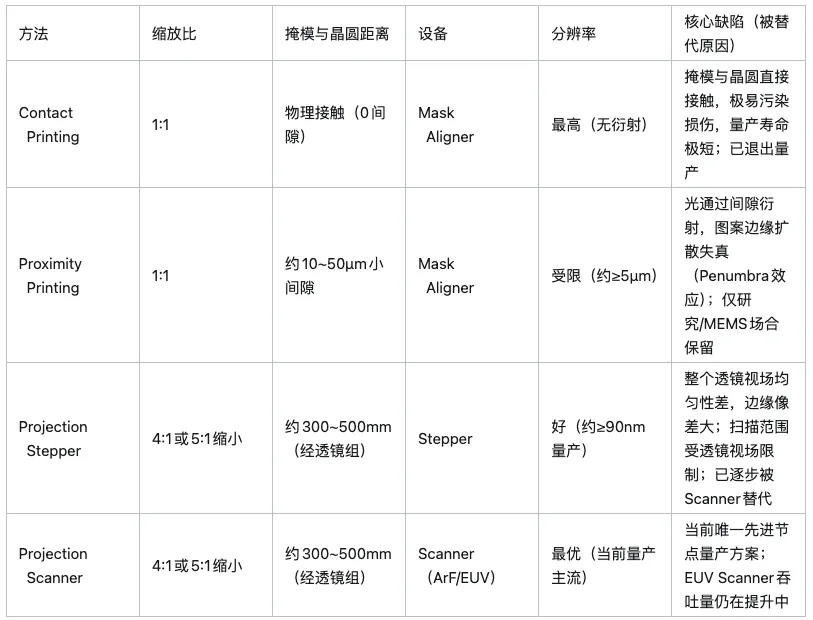

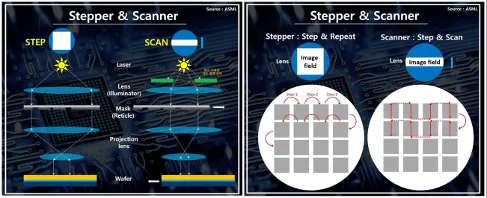

▌一、Stepper vs Scanner:Scanner胜出的本质原因

【Stepper&Scanner光路示意图 — 外部密闭腔体(DUV:N₂/Ar惰性气体;EUV:高真空);从上到下:激光光源(ArF 193nm excimer/EUV LPP光源)→ 照明光学系统(Illuminator,含孔径和照明模式控制)→ 掩模台(Reticle Stage,扫描方向移动)→ 投影透镜组(30+组石英/CaF₂透镜或EUV反射镜)→ 晶圆台(Wafer Stage,与掩模台同步反向扫描)→ 晶圆。Scanner特征:每次曝光只使用约26mm×8mm的透镜中心细缝(Slit)区域,通过同步扫描逐步曝光整个Die(约26mm×33mm)】

▌二、投影透镜系统核心工程参数

•透镜片数:通常>30组石英(SiO₂)或CaF₂(氟化钙)透镜片;每片面形精度要求纳米级;一套ArF透镜价值约占整机成本30~40%

•聚光镜(Condenser Lens):收集光源发散光,整形为特定照明模式(传统/偶极/四极/环形/自由形式)照射掩模

•物镜(Objective Lens):收集掩模图案衍射光,按4x/5x缩小比率聚焦成像在晶圆光刻胶表面

•像差(Aberration):透镜几何偏差使同一物点发出的光无法汇聚到晶圆上同一点,产生图案模糊或畸变;Scanner只使用透镜最优中心区域是其核心改进

•沉浸技术(ArF-i):在投影透镜最底部与晶圆之间充入超纯水(n=1.44@193nm),等效将NA从0.93提升至1.35,分辨率提升约40%

📌 NA(数值孔径)= n×sin(θ),n为介质折射率,θ为透镜最大收光半角。ArF干式最大NA约0.93(空气n=1.0);ArF沉浸式NA约1.35(水n=1.44)。这是193nm波长仍能用于5nm/3nm节点的核心工程原理——利用沉浸介质在相同θ下将NA提升44%。

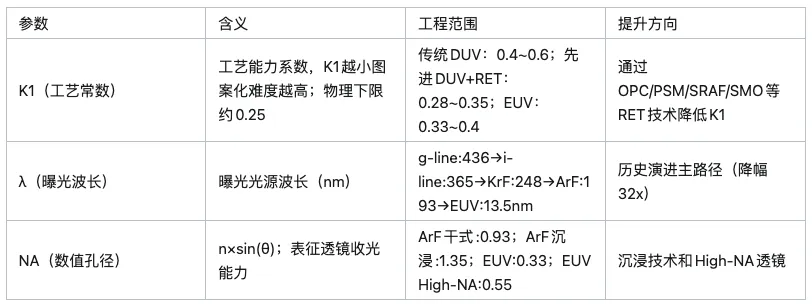

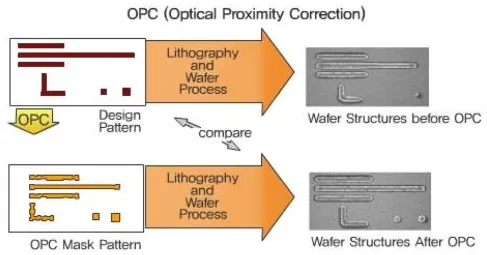

[MSK-5] 分辨率方程 R=K1×λ/NA 与四大RET(分辨率增强技术)

▌一、瑞利分辨率方程详解

Resolution(R)= K1 × λ / NA

实际工程算例(5nm节点,半节距约15~20nm): ArF-i多重图案化:λ=193nm,NA=1.35,K1≈0.27 → 单次曝光R≈39nm,需SADP/SAQP达到15nm目标EUV单次曝光:λ=13.5nm,NA=0.33,K1≈0.35 → R≈0.35×13.5/0.33≈14.3nm(单次可达!) → EUV在5nm以下节点的最大价值:用单次曝光替代ArF-i的2~4次多重图案化,大幅降低工序数和成本

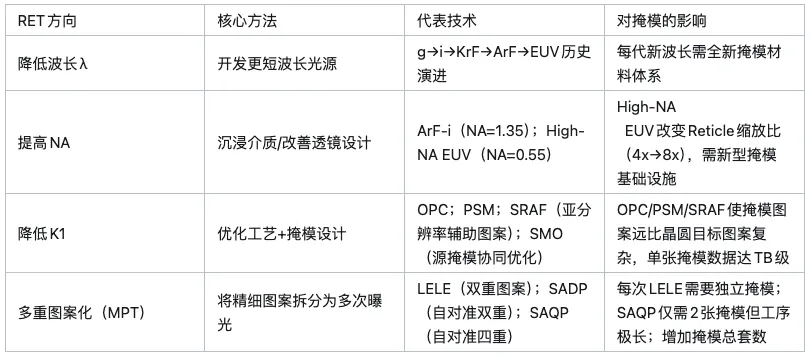

▌二、四大RET(分辨率增强技术)

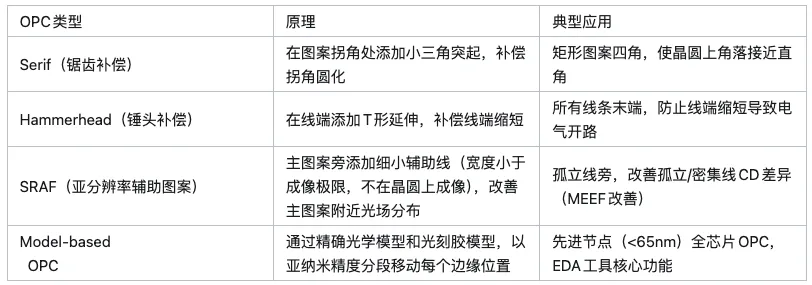

[MSK-6] OPC(光学邻近效应修正):光学失真的预补偿工程

▌一、光学邻近效应(OPE)的三大失真类型

•线端缩短(Line End Shortening):密集线条末端在成像时圆化和缩短(通常10~20%),导致实际图案比设计短,电气开路风险

•图案圆化(Corner Rounding):掩模直角拐角在光刻后变为圆角,极小尺寸特征中可能导致功能失效

•密度效应(Density Effect):孤立线(Isolated Line)和密集线(Dense Line)在相同掩模CD下,晶圆上印刷CD不同——孤立线通常比密集线宽(孤立线周围无干涉抑制),是"邻近效应"的命名由来

【OPC原理对比图 — 上行(无OPC):矩形掩模图案→ 光学邻近效应(衍射+干涉)→ 晶圆上图案圆角、线端缩短、孤立/密集线CD差异;下行(有OPC修正后的掩模图案):添加Serif锯齿(补偿角落圆化)+ Hammerhead(补偿线端缩短)+ SRAF辅助线(改善孤立图案对比度)→ 经相同光学效应后 → 晶圆上图案接近设计目标】

▌二、OPC主要技术类型

OPC处理后,一条简单直线可能被分割为数百个子段,每段边缘独立调整。先进节点(5nm)Logic层单张掩模OPC数据文件可达数TB,OPC计算时间即使在高性能服务器集群上也可能长达数周。OPC是EDA工具(Synopsys、Cadence、Mentor)最高技术壁垒之一,也是国产EDA软件最难突破的关键环节。

[MSK-7] PSM(相移掩模):利用干涉相消实现分辨率突破

▌一、PSM的物理原理

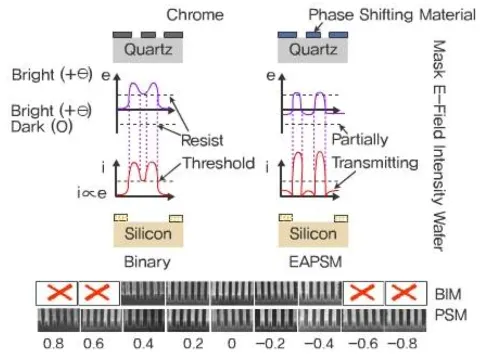

普通掩模(Binary Mask)只控制光的透/阻,所有透光区相位相同(均为0°)。PSM通过引入180°相位差,使相邻透光区的光在图案边界处产生相消干涉(Destructive Interference),光强降至零,大幅提升边界对比度:

相移层厚度 = λ / (2×(n−1))例:ArF(193nm)→ 刻蚀深度 ≈ 193/(2×0.56) ≈ 172nm

【PSM原理对比图 — 上行(Binary Mask):两相邻透光缝隙同相位(0°)透光,中间光强分布双峰但峰谷不为零,对比度差,两线难分辨;下行(Alt-PSM):相邻缝隙一个0°(普通石英),一个180°(刻蚀石英约172nm),两束光在边界处完全相消干涉,光强降至零,边界对比度极高,两线清晰分辨,等效分辨率提升约1.5~2倍】

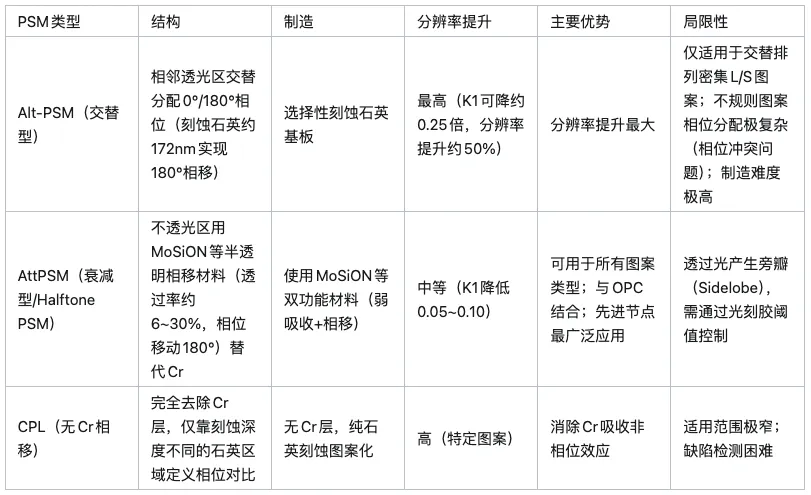

▌二、PSM主要类型对比

AttPSM(Halftone PSM)是目前ArF-i(7nm~14nm)和EUV节点的标准掩模配置——几乎所有关键层次(Gate/Contact/Metal)均采用AttPSM + OPC协同方案。PSM+OPC的组合,是在193nm波长下实现7nm级图案化的核心技术,也是"波长远大于图案尺寸"的光刻技术坚持超过10年的工程奇迹。

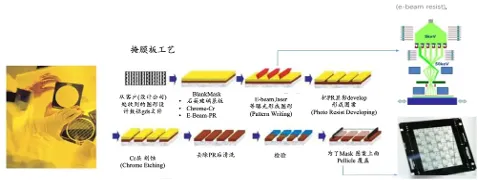

[MSK-8] PhotoMask完整制造流程:从Blank到Pellicle封装的10道工序

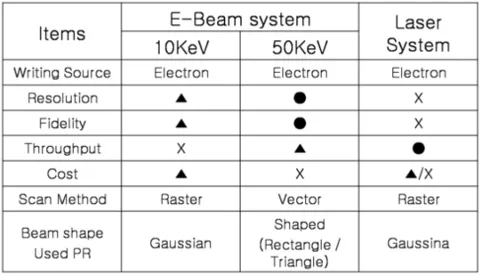

▌一、掩模制造的特殊起点:E-beam直写,无需上级掩模

逻辑起点: 芯片GDS/OPC处理后数据 → E-beam Writer直接写入掩模PR(无需上级掩模)→ 显影→ Cr刻蚀 → 完成掩模 → 掩模送入光刻机 → 4x/5x缩小投影到晶圆掩模是整个半导体制造"零级"图案,不依赖任何更高级别的模板,是纯粹的"数据→实体"转换过程。

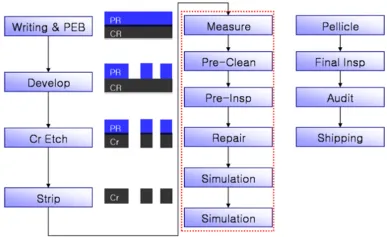

▌二、10道制造工序全流程

1.Blank Mask准备:选用合格Blank Mask(石英基板+Cr膜+e-beam PR已涂布)。基板质量(平坦度/CTE/光学透过率)是掩模精度的物质基础

2.图案写入(Writing / E-beam Exposure):E-beam Writer按GDS/OPC数据逐点扫描曝光PR。能量:10keV(低分辨率)或50keV(先进节点高精度)。先进节点单张写入时间可达十几到几十小时

3.后曝光烘烤(PEB):约90~110°C烘烤,激活CAR型e-beam PR的化学放大去保护反应,完成潜像化学放大

4.显影(Development):TMAH显影液去除已曝光区PR,形成PR图案并露出下方Cr膜。显影后立即进行PR图案CD确认

5.铬层刻蚀(Cr Etching):以PR图案为掩膜刻蚀Cr膜。干法刻蚀(Cl₂+O₂等离子体,各向异性佳,CD控制精确,主流)或湿法刻蚀(铈铵硝酸盐溶液,侧向刻蚀较大,已逐步被干法取代)

6.去胶(Strip):浓硫酸(H₂SO₄,120°C以上)或等离子体O₂灰化(Ashing)去除残余PR,暴露完整Cr图案

7.清洗(Cleaning):系列化学清洗去除颗粒/有机物/金属污染。标准清洗序列:SPM(H₂SO₄+H₂O₂,Piranha,去重有机物)→ QDR/Rinse冲洗 → SC1/APM(NH₄OH+H₂O₂+H₂O,去颗粒)→ Megasonic超声辅助去颗粒 → IPA蒸汽干燥(防水渍Watermark)

8.检测与修复(Inspection & Repair):KLA系列设备全图案检测,发现缺陷后针对性修复(见MSK-9详述)

9.Pellicle封装:清洗合格的掩模在超净间安装Pellicle(框架+薄膜用特殊粘合剂固定,DUV离Mask表面约6~9mm),完成最终物理保护

10.最终质检与出货:CD测量(Final CD Metrology)+ Registration检测 + 外观检查,所有指标满足客户Spec后出货

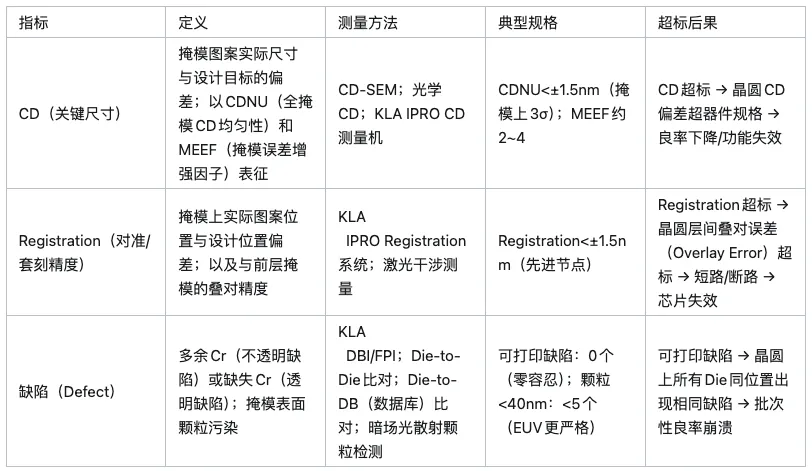

[MSK-9] 掩模板质量管控:CD测量 · 缺陷分类修复 · Registration检测

▌一、三大核心质量指标

▌二、两类缺陷的修复策略

◆ ① Opaque Defect(不透明缺陷 / 铬缺陷)

定义:应透光区域存在多余铬(Cr),导致光被遮挡,晶圆对应位置出现多余遮光图案(等效"多余实心"缺陷)。

•成因:Cr刻蚀残留(过刻蚀不足);颗粒污染落在透光区形成类Cr遮光点

•修复方法:激光消融修复(聚焦激光束精确烧蚀去除多余Cr);或FIB(聚焦离子束铣削,精度更高但速度慢)

•修复难点:激光能量必须精确控制,避免损伤下方石英基板(损伤基板会改变EUV相位或DUV相位透过率)

◆ ② Clear Defect(透明缺陷 / 缺铬缺陷)

定义:应遮光区域缺失铬(Cr),导致光意外透过,晶圆对应位置出现多余透光图案(等效"缺失孔"缺陷)。

•成因:过刻蚀(Over-etch)导致Cr被过多去除;E-beam写入错误使应保留区域的PR被错误曝光后Cr被刻蚀

•修复方法:EBID(电子束诱导沉积)——注射有机金属前驱体气体,用聚焦电子束诱导分解沉积碳质/金属薄膜填补缺失遮光层

•修复后验证:修复材料光学特性需与原始Cr接近;修复区域CD满足规格后需重新进行AIMS打印验证

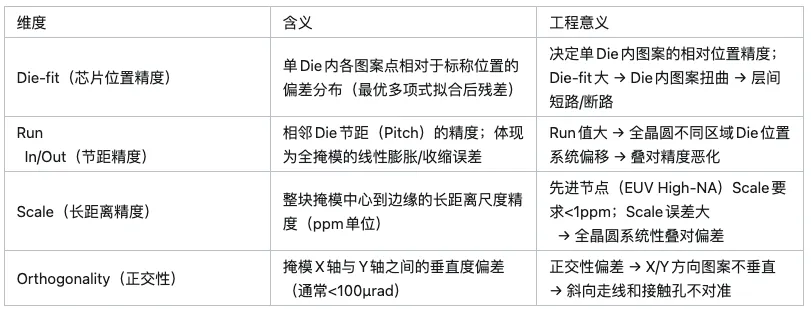

▌三、Registration(对准精度)的四维表征

▌四、掩模检测设备供应链格局

本文要点总结

•PhotoMask = 石英基板+Cr遮光膜+Pellicle;Reticle是4x/5x缩小投影掩模;Blank Mask是未写图案原材料

•DUV透射型(Cr图案+石英透光);EUV因光子能量92eV必须用反射型(40对Si/Mo多层膜反射率67~70%+TaBN吸收体图案)

•图案转移演进:Contact→Proximity→Stepper→Scanner;Scanner只使用透镜中心高质量细缝区域(26mm×8mm),CDU和像差表现更优

•分辨率方程 R=K1×λ/NA;四大RET:降λ(历史路线)、提高NA(ArF-i沉浸/High-NA EUV)、降K1(OPC/PSM/SRAF)、多重图案化(SADP/SAQP)

•OPC:线端Hammerhead/角落Serif/亚分辨SRAF/Model-based多种类型;先进节点OPC数据达TB级,计算数周

•PSM:AttPSM(透过率6~30%+180°相移,先进节点标准配置);Alt-PSM(分辨率最高但仅适合密集L/S);PSM+OPC是ArF-i实现7nm的核心

•制造10步:Blank→E-beam写入(NuFlare垄断)→PEB→显影→Cr刻蚀→去胶→SPM/APM/Megasonic清洗→检测修复(KLA)→Pellicle封装→质检出货

•质量三指标:CD(CDNU<±1.5nm);Registration(<±1.5nm,含Die-fit/Run/Scale/Orthogonality);Defect(可打印缺陷零容忍)

•供应链卡脖子:E-beam机(NuFlare)、掩模检测(KLA)、AIMS验证(Zeiss 100%垄断)、EUV Blank基板(HOYA/AGC)、EUV Pellicle(Canatu)——五大环节几乎全部受控于出口管制

💡 掩模板产业链是半导体供应链中"卡脖子"最集中的领域之一。从E-beam写入机到AIMS验证设备,从EUV Blank基板到EUV Pellicle,几乎所有关键环节均由欧美日企业垄断,且多为全球唯一供应商或双供。任何一个环节中断,均意味着全球最先进芯片制造的停摆。

下期预告

下期将深入解析 光刻材料i-line/DUV/EUV 光刻胶原材料关键参数对比核心问答正负型PR DNQ/Novolac CAR化学放大型 PAC vs PAG EUV无机PR Dry Resist。

关注 ChipNote芯笔记,持续深入半导体制程与良率提升

第七章真实DRC违规案例深度解析DRC:Case Study核心案例 | M2面积违规 · GT间距违规 · DG包围违规 · PAD规则 · CT位置违规 · M1封装改版

第六章典型存储器设计规则:DRC:Typical Memory Design Rule核心问答 | 存储器三区域规则体系·Cell/Core/Peri差异·SRAM位单元几何约束

第五章芯片密度规则与天线规则深度解析:DRC:Density&Antenna Rule核心问答|图案密度·Al/Cu工艺差异·CMP碟形缺陷·天线效应·修复策略

第四章芯片标准设计规则深度解析:DRC:Standard Design Rule核心问答 | AA规则 · GT规则 · CT规则 · Metal规则 · LDD阴影效应

第三章芯片设计规则术语精确定义:DRC:Terminology in Design Rule Define设计规则术语精确定义核心问答 | Width·Space·六大关键术语

第二章芯片设计规则基础入门:DRC:Design Rule Introduction核心问答 | 设计规则的定义·三大核心意义Drawing/Mask/Si-rules三层规则体系

第一章芯片设计规则检查:基础入门DRC(Design Rule Check)核心问答 | 什么是DRC · 验证流程 · Gating机制 · 工具资源配置

Dry Resist(干式光刻胶)深度解析-核心问答 | 半导体生产工序必备知识点

夜雨聆风

夜雨聆风