AI SoC验证实战课——专家1v1实战

00

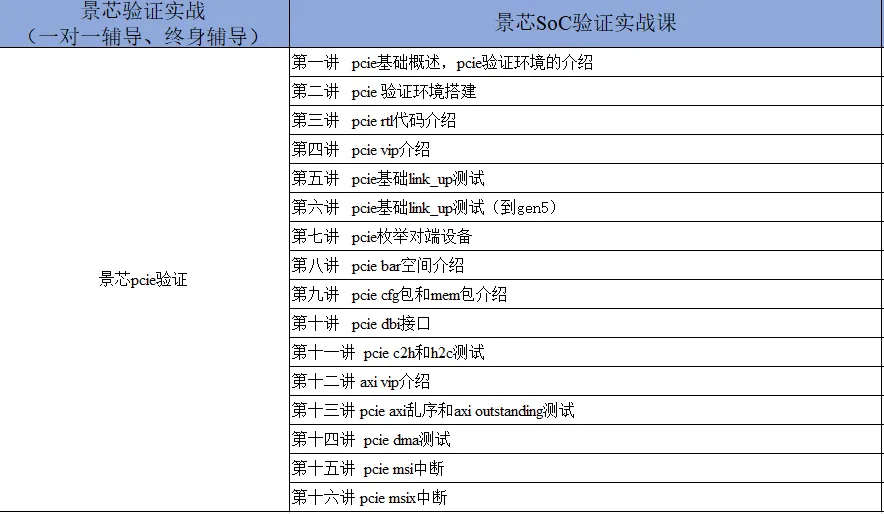

景芯SoC验证实战课汇总

景芯验证专家老师1v1辅导学员,让您快速超越同龄人。景芯训练营主打文档+服务器实战,我们不卖视频,只提供免费导学视频!希望您成为公司的中流砥柱后,给景芯团队介绍design servie业务(有提成)!支持学员自己组团拼课,3人成团优惠500/人!

-

验证实战课1:基础课(sv+uvm、afifo、ahb2apb、uart、i2c、qspi、wdt)

-

验证实战课2:进阶课(景芯SoC橙色域子系统验证)

-

验证实战课3:PCIE验证实战课

-

验证实战课4:DDR验证实战课(工程就绪,我忙不过来,招聘讲师中)

-

验证实战课5:CAN验证实战课

01

验证实战课1:基础课

验证实战课2:进阶课

Part.01

验证基础课

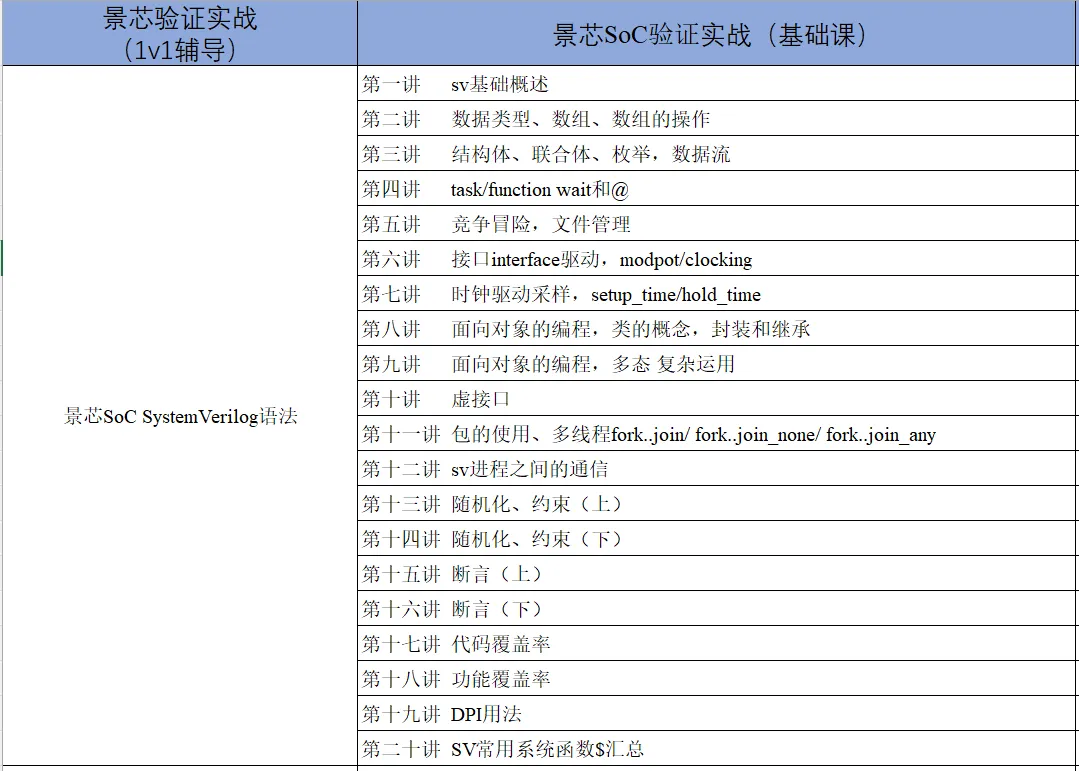

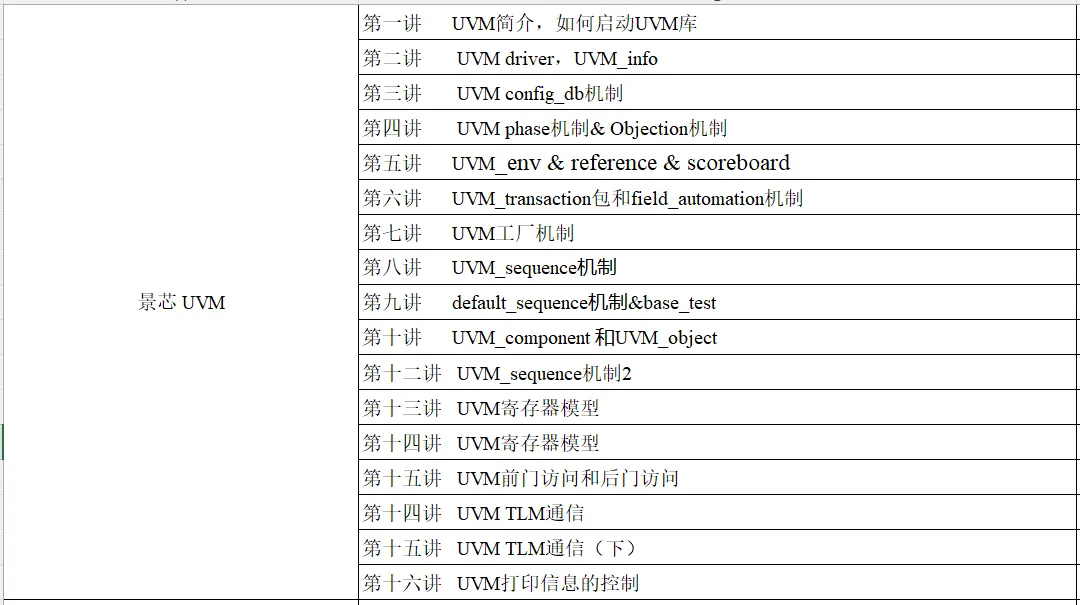

一对一辅导是景芯SoC训练营的特色!景芯SoC验证实战基础课最新课表如下:

总结起来,景芯SoC验证基础课包含如下内容:

-

景芯sv+uvm验证实战精讲

-

景芯异步fifo设计验证实战

-

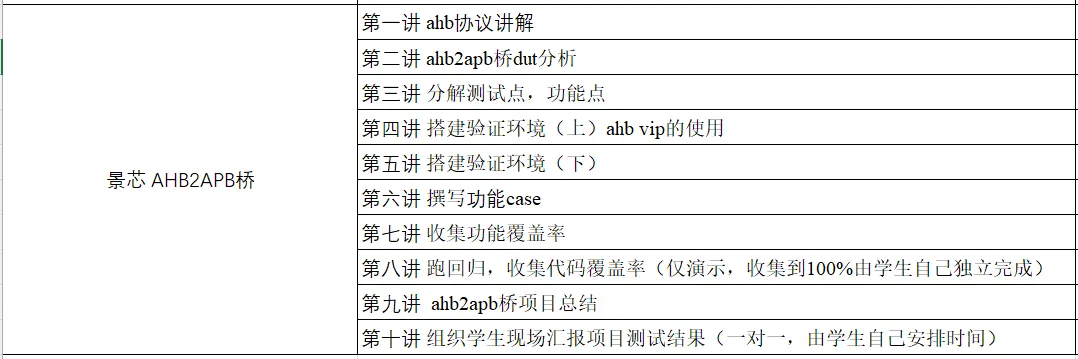

景芯自研ahb2apb验证实战

-

景芯自研uart设计+uvm验证

-

景芯自研i2c 设计+uvm验证

-

景芯自研qspi设计+uvm验证

-

景芯自研wdt设计+uvm验证

Part.02

验证进阶课

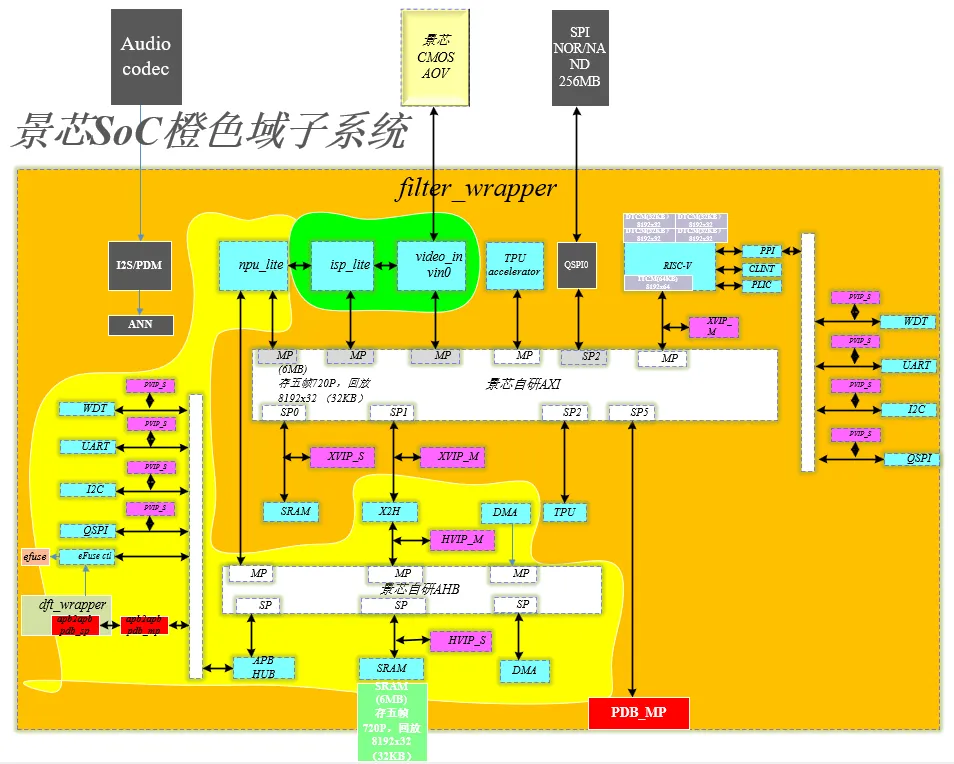

橙色子系统采低功耗RISC-V自研架构,全部自研实现了AXI总线矩阵、AHB总线矩阵、MIPI DPHY软核、ISP-Lite、NPU-lite、SRAM、DMA、UART、I2C、QSPI/SPI等常用IP,项目架构图如下:

橙色子系统验证采用UVM验证方法学、C驱动等方式对SoC子系统进行验证,ENV环境集成了UART UVC子系统验证环境,将UVM验证方法学常用的知识一网打尽,再联合VIP+AMBA总线+SRAM+DMA进行系统级仿真。特别是新增packet filter模块,针对超长包、超短包、毛刺包、包头错、包尾错等错误case进行构造,并通过收集各种corner case的覆盖率来提升验证的实践能力。景芯SOC验证AXI VIP实战

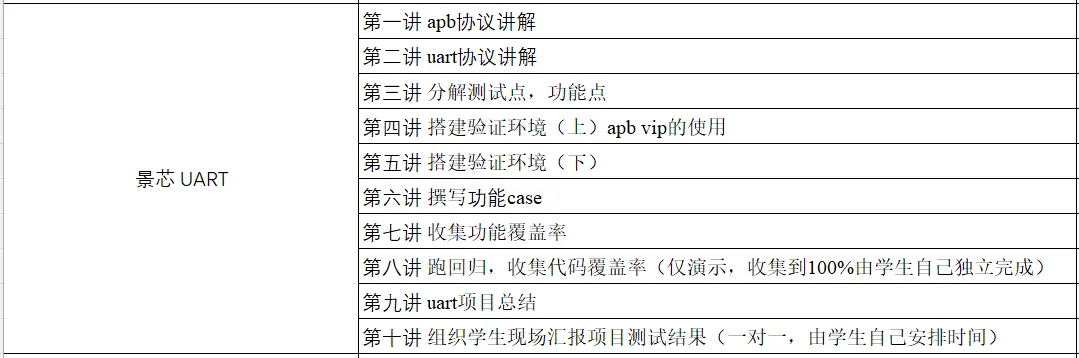

景芯SoC验证进阶课最新课表如下(买进阶课、送基础课):

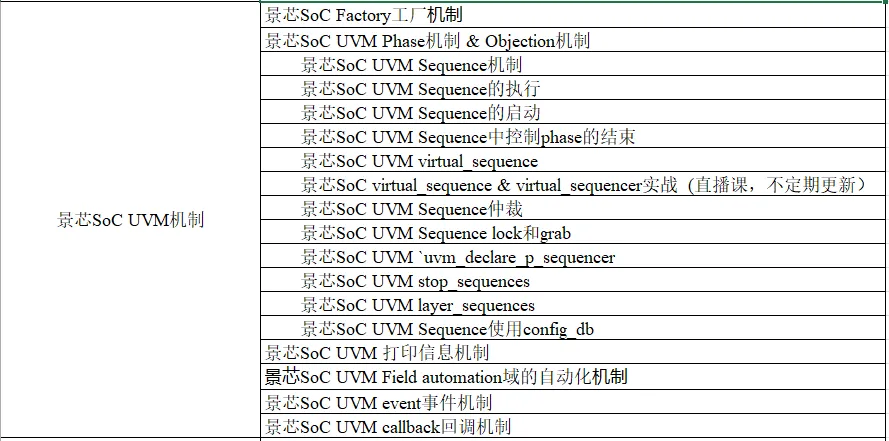

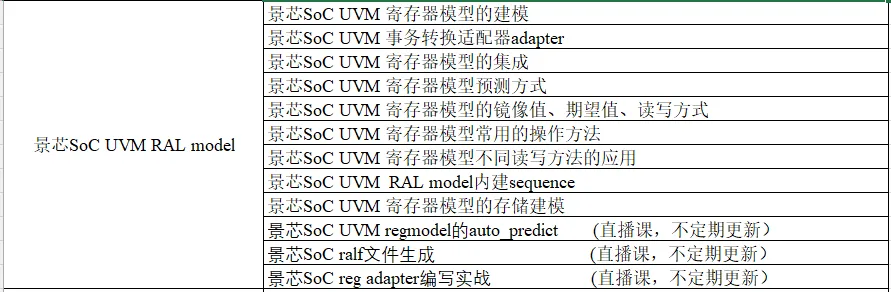

总结起来:景芯SoC验证进阶课

-

景芯SoC系统验证UVM环境搭建

-

景芯SoC系统验证VIP搭建

-

景芯SoC系统验证UVC搭建

-

景芯SoC系统验证上电启动

-

景芯SoC系统验证复位流程

-

景芯SoC系统验证时钟

-

景芯SoC系统验证中断

-

景芯SoC系统DMA+SRAM验证

-

景芯SoC MIPI+ISP+NPU软硬件协同验证

-

景芯SoC系统packet验证

-

景芯自研axi2apb验证实战

04

PCIE验证实战课

如果您渴望成为数字IC领域的顶尖高手,PCIe子系统设计就是你必须征服的终极关卡!

本次IC设计课程,我们精心打磨了一套“理论+工具+项目”三位一体的PCIe教学体系,助你快速突破技术壁垒! 抢占数字IC领域的技术制高点,开启你的 PCIe技术进阶之旅,下一个数字IC高手,就是你!

Part.01

PCIE验证实战课

总结起来,专用IP的验证课程总结如下:

-

景芯pcie uvm验证实战

-

景芯ddr uvm验证实战

-

景芯can uvm验证实战

-

景芯psram uvm验证实战

-

景芯sdio/emmc验证实战

-

景芯gmac uvm验证实战

-

景芯usb uvm验证实战

-

景芯axi icache设计验证实战

-

景芯axi l2 cache设计验证实战

Part.03

课程报名微信,扫描咨询我们吧

景芯SoC芯片全流程实战附属【知识星球】,一个包括设计、验证、DFT、后端全流程技术的交流平台,也是景芯学员的答疑平台!若您和我一样渴求技术,那欢迎扫下面二维码加入星球,共同进步!

03

验证岗位招聘

业内明星公司主要招聘需求如下:景芯SoC学员供不应求了

SoC 验证工程师

岗位职责:

1、根据设计需求、架构和规格,制定验证方案和计划;

2、根据验证方案和计划,搭建 IP 或 SoC 验证环境,开发和调试测试用例、check 机制等;

3、分析和定位测试用例错误原因,协助设计人员定位和解决问题;

4、验证回归,收集和分析覆盖率;

5、输出验证报告;

6、提升验证效率,如采用自动化脚本、高效验证方法等。

任职要求:

1、微电子、电子工程等相关专业硕士及以上学历,三年以上工作经验;

2、有丰富的 IP 或 SoC 验证经验,熟悉验证流程;

3、熟练掌握 Verilog/SystemVerilog/Python 等;

4、熟练掌握 UVM 验证方法学,能独立完成 IP 或 SoC 验证环境搭建及调试;

5、熟悉 AMBA 总线,具有 isp, codec, npu, display 等相关验证经验优先;

6、良好的表达沟通能力及团队合作精神,较强独立工作能力和动手能力;

7、良好的英文阅读、文档编写能力。

04

SoC验证到底做什么

流片成败,看验证。很多想入行IC、准备转SoC验证的同学,都会问:验证工程师到底在做什么?是不是只跑仿真、看波形?其实,真正的SoC芯片验证,是一套从顶层规划到芯片落地的完整工程体系,也是芯片上线前的最后一道质量关。

• 根据芯片规格书,制定验证策略与整体方案• 明确验证范围、重点模块、风险点• 设定覆盖率目标、验收标准与时间节点二、搭建验证环境环境搭得稳,后面的测试、回归、定位问题都会事半功倍。这是验证工程师最核心的技能之一:

• 用SystemVerilog、UVM搭建可重用的验证平台• 开发测试用例、激励序列、参考模型• 集成VIP、总线协议、接口模型• 编写自动化仿真脚本

三、执行仿真测试环境搭建完成后,就进入真正的测试环节,尽可能把芯片里的问题“逼出来”。

• RTL级功能仿真,验证逻辑正确性• 门级仿真、低功耗仿真• 批量回归测试,保证改代码不引入新Bug• 覆盖正常场景、边界场景、异常场景

四、调试与问题定位仿真不通过,就要定位问题、分析根因。调试能力,是区分普通验证和资深验证的关键:

• 看波形、查日志、追踪信号流向• 判断是设计问题还是验证用例问题• 和设计工程师沟通,推动问题修复• 记录Bug、闭环管理五、覆盖率分析很多初学者只关心“过了仿真”,但行业里真正看重的是:有没有测完整?有没有漏?覆盖率达标, 确保所有设计功能都被覆盖到才敢说验证基本完成。• 收集代码覆盖率、功能覆盖率• 分析覆盖率缺口,补充测试点此外,还有硬件验证与硅后支持,要从仿真到真实芯片

• 参与FPGA原型验证• 支持硬件仿真、加速验证• 流片后协助硅后测试与 bringup

• 输出验证总结,形成流程沉淀

05

验证课后作业

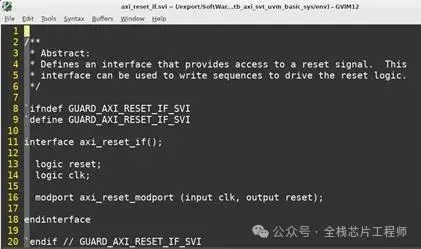

课后作业:景芯SOC验证AXI VIP实战:

1. 包含AXI VIP库文件

编译选项:在仿真脚本中引用Synopsys AXI VIP库路径,例如:

vcs -sverilog +incdir+VIP_HOME/svt_axi/svt_axi_pkg.svbr

景芯SoC是在Makefile中引用Synopsys AXI VIP库路径,例如:

注意,axi_reset_if的接口定义如下:

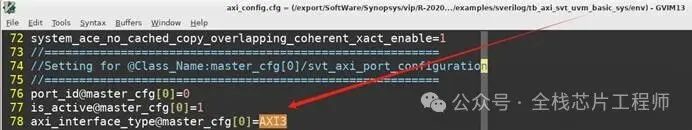

2. 配置AXI VIP Agent

2.1 创建AXI System Configuration

首先看下axi_config.cfg配置文件,所有配置项都在这文件里,注意,默认是AXI3, 根据需求定义协议版本(如SVT_AXI_VERSION=AXI4)。

配置对象:在UVM环境中创建系统级配置对象,指定协议参数:

svt_axi_system_configuration axi_sys_cfg; axi_sys_cfg = svt_axi_system_configuration::type_id::create("axi_sys_cfg");axi_sys_cfg.num_masters =1; // Master数量axi_sys_cfg.num_slaves = 1; // Slave数量axi_sys_cfg.addr_width = 32; // 地址位宽axi_sys_cfg.data_width = 64; // 数据位宽br

景芯SoC实际配置如下:

注意,作为master对应的is_active = 1,只作为监测(monitor)使用时,对应slave_cfg的is_active = 0。

//配置Master Agent为Active(驱动事务)

axi_sys_cfg.master_cfg[0].is_active = UVM_ACTIVE;

//配置Slave Agent为Active(生成响应)

axi_sys_cfg.slave_cfg[0].is_active = UVM_ACTIVE;

注意,在axuser_enable、axqos_enable不做配置时,VIP默认采用0进行发送。同样ready信号在不做配置的情况下,VIP默认置位为1。

foreach(this.master_cfg[i]) begin

this.master_cfg[i].aruser_enable = 1;

this.master_cfg[i].awuser_enable = 1;

this.master_cfg[i].wuser_enable = 1;

this.master_cfg[i].arqos_enable = 0; //景芯同学注意,AXI3情况下此处必须为0

this.master_cfg[i].awqos_enable = 0; //景芯同学注意,AXI3情况下此处必须为0

end

foreach(this.slave_cfg[i]) begin

this.slave_cfg[i].default_awready = 0;

this.slave_cfg[i].default_wready = 0;

end

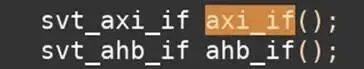

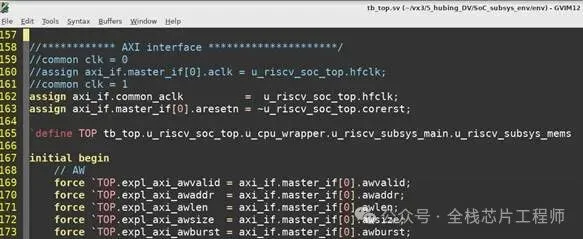

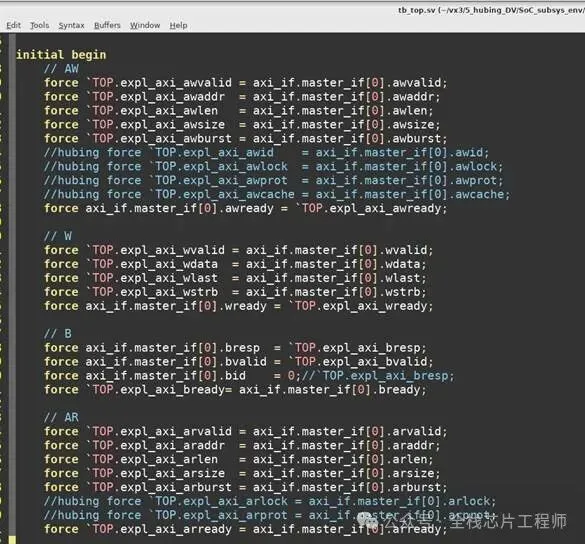

3 端口连接

//在tb_top.sv定义AXI接口实例(Master/Slave共用)

svt_axi_if axi_if(clk, rst_n);

1)各端口相同时钟

2)各端口不同时钟

除上述common_aclk的赋值外,需要对单个master/slave_if时钟进行赋值

//绑定信号到DUT端口,以VIP作为Slave为例子:

assign axi_if.awaddr = dut.awaddr;

assign axi_if.awvalid = dut.awvalid;

assign dut.awready = axi_if.awready;

// … 其他信号类似连接(W, B, AR, R通道)

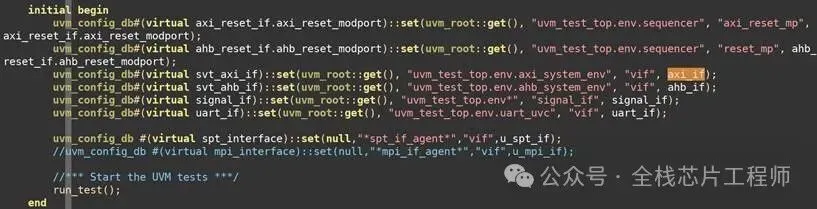

3. 环境例化

在tb_top.sv中将物理接口绑定到VIP Agent的虚拟接口:

initial begin uvm_config_db#(virtual svt_axi_if)::set(null, "uvm_test_top.env.axi_master0", "vif", axi_if);endbr

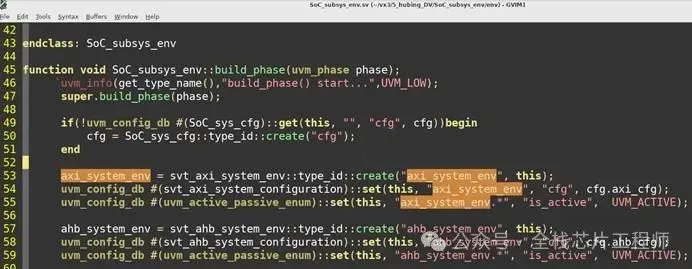

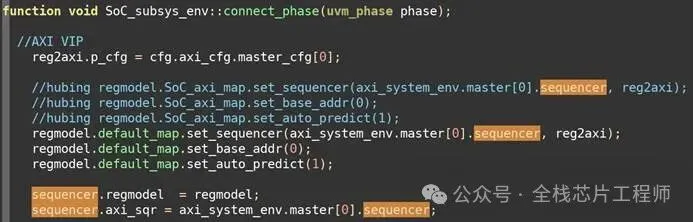

在SoC_subsys_env.sv中将物理接口绑定到VIP Agent的虚拟接口:

svt_axi_system_env axi_system_env;

uvm_config_db#(svt_axi_system_configuration)::set(this," axi_system_env ","cfg",cfg.axi_cfg);

axi_system_env = svt_axi_system_env::type_id::create("axi_system_env ",this);

4.事务级连接(TLM接口)

自动连接Sequencer与Driver,VIP内部自动将Master Sequencer与Driver绑定。若需自定义,可手动重写connect_phase:

virtual function voidconnect_phase(uvm_phase phase); master0.driver.seq_item_port.connect(master0.sequencer.seq_item_export);endfunctionbr

创建Master Sequence事务生成,编写UVM Sequence驱动Master Agent发送AXI事务:

classaxi_master_seqextendsuvm_sequence #(svt_axi_master_transaction); `uvm_object_utils(axi_master_seq)task body(); svt_axi_master_transaction tr; tr = svt_axi_master_transaction::type_id::create("tr"); start_item(tr);tr.randomize() with {cmd_type==svt_axi_transaction::WRITE;addr== 32'h8000_0000; data.size() == 4; }; finish_item(tr);endtaskendclassbr

Slave响应配置

Slave Sequence:配置Slave Agent生成预期响应(如固定延迟或错误注入):

classaxi_slave_seqextendsuvm_sequence #(svt_axi_slave_transaction); task body();forever begin svt_axi_slave_transaction tr; start_item(tr); tr.randomize() with {rresp == svt_axi_transaction::OKAY; rvalid_delay inside {[1:3]};}; finish_item(tr);end endtaskendclassbr

注意事项:

1、信号命名一致性

VIP接口信号名称需与DUT端口严格匹配(如awaddr与AWADDR可能不兼容)。

2、协议版本匹配

确认VIP配置的AXI版本(AXI3/AXI4/AXI5)与DUT一致,避免信号不兼容(如AXI4的awregion在AXI3中不存在)。

3、时序冲突检查

启用VIP内置协议检查器(默认开启),实时监测信号违反(如valid与ready握手冲突)。

4、跨时钟域处理

若存在异步时钟域,需在VIP配置中指定跨时钟域参数(如svt_axi_port_configuration::is_aclk_asynchronous = 1)。

调试技巧

波形标记:在仿真时添加VIP内部信号到波形(如axi_if.aclk, axi_if.awvalid)。

协议日志:启用VIP的协议消息打印(设置svt_axi_transaction::debug_enabled = 1)。

错误断点:在VIP回调(callback)中设置断点,定位协议违规位置。

通过以上步骤,可完成景芯SoC Synopsys AXI VIP与芯片设计AXI接口的完整集成。

06

景芯SoC训练营好评如潮

十分感谢景芯学员们对景芯的信任和支持,景芯团队一定更努力精心打磨景芯SoC实战课,让大家无论资深还是资浅都能从景芯训练营获得成长!

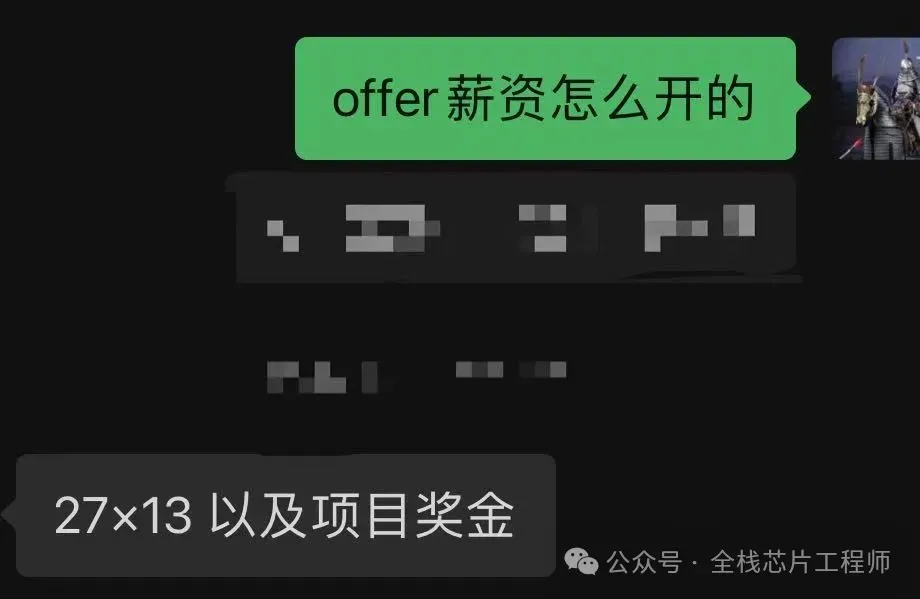

最近学员纷纷咨询小编offer选择的问题,看到大家通过景芯培训提升后拿到心仪的offer了,非常开心,祝贺大家都拿到心仪offer了!

另外,小编的一个景芯VIP学员,成都某985,硕士7年经验,之前通过景芯培训提升后拿到心仪的offer了,这3个offer我看了都眼红!上次发起了投票,今天公布下结果。先来看下三个offer情况:

1、 某GPU公司,月薪5.8w,年终4个月合计23.2万,年薪92.8万,岗位是SoC前端设计,公积金12%;

2、多媒体SOC厂商JC,月薪6.5w,年终奖2个月合计13万,年薪91万,岗位是SoC芯片设计工程师,公积金12%;

3、 国企X微电子,月薪5.5W,年终奖4个月合计22万,年薪88万,担任数字ic设计工程师,主要从事SOC芯片设计,公积金10%

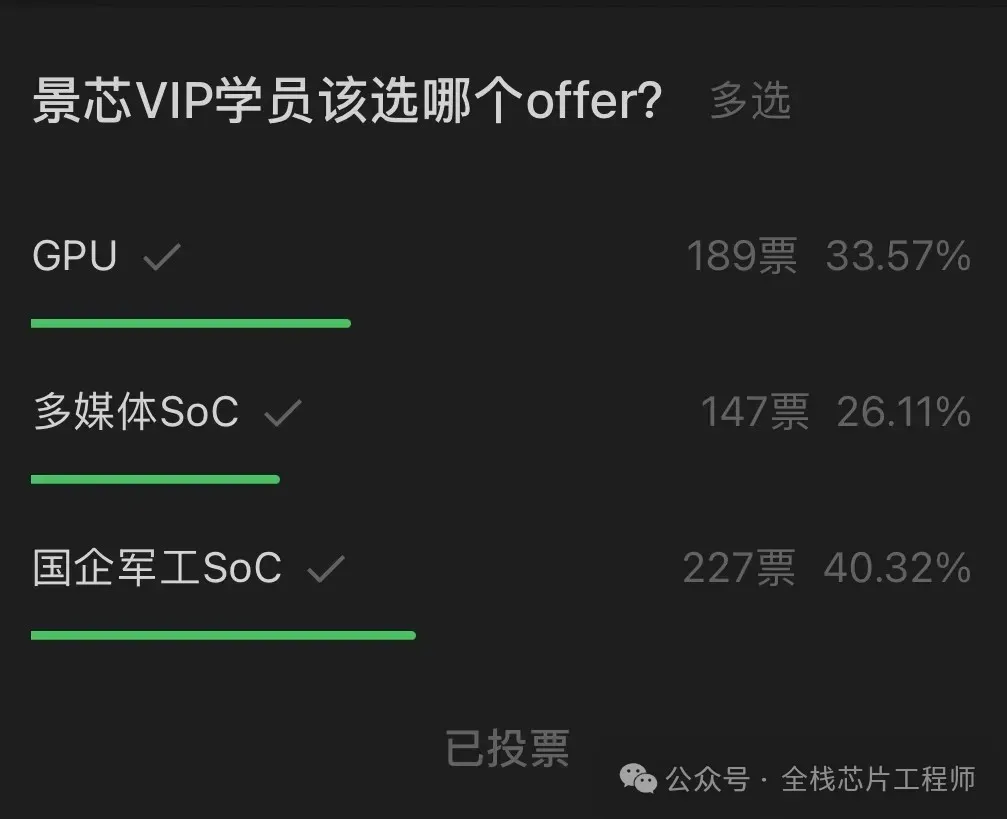

这里补充发布上次大家的投票结果公布:

从结果可以看出,市场行情不好,大家都看好国企军工的稳定性了,GPU仍然是技术首选,虽然GPU公司都在厮杀,但是仍有前景,但是IPC SOC反而得票最低,内卷同时没有太大增量市场。

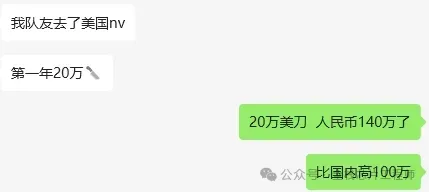

另外,景芯资深老学员告诉我,留学X国的硕士去外企某芯片巨头薪资是20万+美金!折合RMB超过140万,才25岁左右的小伙子!薪资超140万!努力学习技术吧 骚年。

如果您和小编一样渴求进步,想掌握芯片设计全流程,欢迎加入小编知识星球,疯狂成长,一起进步!早日成为芯片大佬!

课程报名微信:

07

验证求职指导

景芯训练营依托十余年芯片行业一线实战经验+全流程芯片验证项目教学积淀,为芯片验证从业者/求职者打造「技术培训+求职辅导」一体化解决方案,以全程1V1专属辅导为核心,从项目实战、简历打磨、面试攻坚到谈薪博弈,全环节精准赋能,稳稳拿下大厂高薪Offer!

一、1V1简历精修,挖掘亮点针对芯片验证求职简历“投递无门、秒挂、亮点埋没”痛点,景芯训练营资深导师以面试官视角开展1V1深度辅导,拒绝模板化修改,精准匹配芯片验证岗位招聘需求:1. 深挖技术亮点:1V1沟通梳理您的项目经历,聚焦UVM验证、SoC子系统验证、覆盖率分析、corner case构造等核心技能,提炼项目难点、落地成果与技术突破,剔除无效内容,让简历贴合大厂技术需求。2. 字句打磨:针对芯片验证简历的专业表述、项目流程、成果量化进行逐字润色,强化与目标岗位的匹配度,让你的经历从数百份简历中脱颖而出。3. 定制化投递:结合您的技术背景与求职目标,1V1分析头部芯片企业验证岗位招聘偏好、业务前景,避开求职“天坑”,精准推荐适配企业与投递时机,提升简历通过率。

二、1V1面试攻坚:实战模拟由资深技术面试官坐镇,依托景芯训练营19家头部芯片企业验证笔试面试真题库+真实项目实战经验,开展1V1全流程面试指导,解决“技术不错但面试翻车”难题:1. 模拟面试:针对芯片验证基础(UVM方法学、AMBA总线、VIP使用等)、项目实操、笔试真题进行深度1V1对练,还原大厂面试场景,模拟技术面、HR面全流程,让你提前适应面试节奏;2. 独家面试技巧赋能:1V1传授芯片验证面试避坑指南,包括项目描述技巧、技术问题应答逻辑、难点问题拆解方法,结合真题讲解高频考点作答模板,让你面试处变不惊,轻松应对各类提问。

三、1V1谈薪指导景芯训练营以行业老兵视角为你提供1V1谈薪策略与职业规划,从薪资博弈到Offer抉择,全程保驾护航。1. 背靠背谈薪策略定制:1V1分析目标企业薪资体系、芯片验证岗位职级薪酬标准,结合您的工作经验、技术能力定制专属谈薪方案,教你分阶段谈判话术——面试初期如何规避薪资报价陷阱、终面后如何抛出理想薪资、收到Offer后如何争取更高薪资与职级,最大化薪资涨幅;2. 私人情报站赋能:动用行业人脉为你1V1挖掘意向企业的真实薪资结构、福利政策、加班情况、晋升通道,让你谈薪时有据可依,精准博弈;3. 长期职业规划指导:结合你的技术背景、性格特点与芯片行业发展趋势(如低功耗验证、车规芯片验证、先进制程验证等),1V1分析Offer优劣,为你规划长远职业发展路径,避免职业选择走弯路,让每一次跳槽都成为职业飞跃的跳板。

夜雨聆风

夜雨聆风