文档内容

第4期 微处理机 No.4

2009年8月 MICROPROCESSORS Aug.,2009

RTL到GDSII设计流程概述

牛英山1,张燕军2

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.中国兵器第二0二研究所,成阳712099)

摘要:从环境设置、约束检查、时钟规划、逻辑综合、布局优化及插入DFT、时钟树综合、CTS

后优化、布线及优化、物理验证、参数提取、静态时序分析、功能验证、形式验证和自动测试向量生成

等方面,对RTL到GDSII的设计流程进行了简要的叙述。

关键词:逻辑综合;时钟树综合;静态时序分析;形式验证

中图分类号:TN4 文献标识码:A 文章编号:1002—2279(2009)04-0005—02

The Summary of RTL to GDSIl Design Flow

NIU Ying—shanl。ZHANG Yah—inn

(1.The47th Research InstituteofChinaElectronics Technology Group Corporation,Shenyang 110032,China;

2.No.202 InstituteofChinaOrdnance IndustryGroup,Xianyang712099,China)

Abstract:RTL to GDSII design flow is briefly described from environment setting.constraint

checking,clock plan,synthesis,floorplan and power plan,placement and optimization with DFT,clock

tree synthesis,post—CTS optimization,routing and optimization,physical verification,RC extraction,static

timing analysis,functional verification,formal check,automatic testpattern generation,etc.

Keywords:Synthesis;Clock tree synthesis;Static timing analysis;Formal verification

(1)环境设置 I(7)时件坩缘合

1前言 rDC,Pc毋FT,PT ●I C做1Alst…ro)…一……④

RCXT,VCS, l∞黑景攀

随着集成电路制造工艺的不断发展,为解决制

山

造工艺中出现的各种情况而应运而生的设计工具也 伫’(P黼ttmeT船tme)f

la呀布t蛾'A。厦ura优't化l

0

越来越多。不同EDA工具供应商都有不同的设计

∞(‰)e时Tt'r.ne规)捌 ¨嚣黜学

工具。如何将这些工具根据目标工艺的情况有机的

山

(|)埋辑综合 (1∞物理验证

组合在一起共同发挥作用,则成了IC设计工程师的 c(“D∞叫‘e和r) o”(H。ercu然les)

一大难题。这就是RTL到GDSII的设计流程所要 上 山

(5)布局攫捌

解决的问题。 和电一规捌 0

(Astro/

,d~gLroRaln (12)膏杏时序分析

‘I·'?~…一● (pr*raTline)

2 RTI。到GDSII设计流程 J_ ●回布局厦优

化及插入 +一.1

DFT ct田(Fo形n。式alf验,.v)证

以Synopsys的设计工具为例,介绍一下RTL到 (Phystcsfl (1硼t验证

Cotr甲der)

GDSII的设计流程,其他公司的工具可以根据其功 ::、 (VCs)

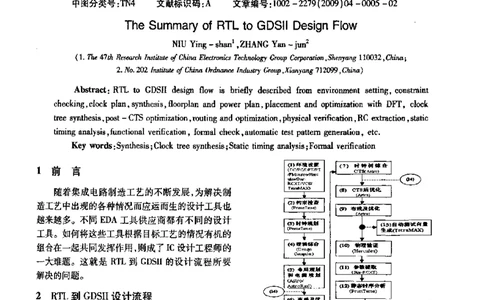

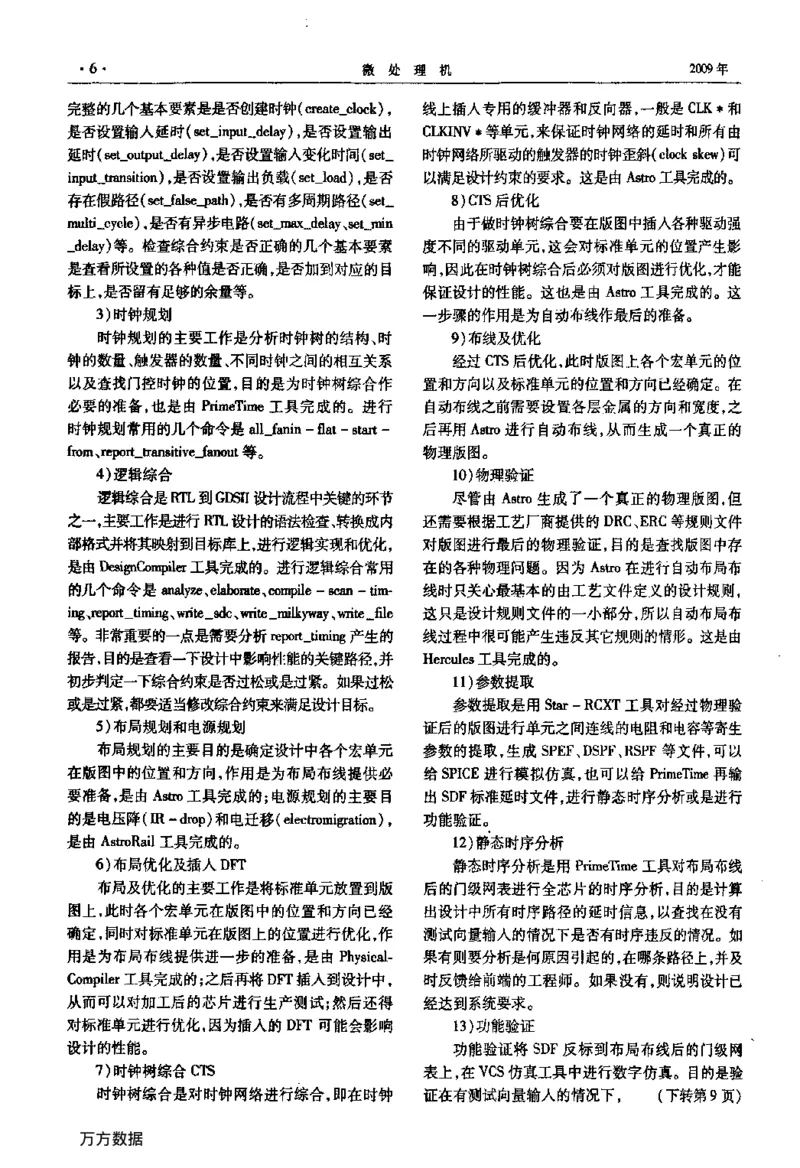

能相应替换设计流程中的工具,如图1所示。

该流程主要由以下15个阶段组成: 图1 RTL到GDSH设计流程

1)环境设置 2)约束检查

环境设置的主要工作是设置一些环境变量,以 约束检查的主要工作是检查综合约束的完整性

便可以找到流程中所用到的设计工具、所用到的设 和正确性,是由PrimeTime工具完成的。进行约束

计脚本以及设计需要的各种库文件和规则文件,并 检查常用的几个命令是report—analysis—coverage、

同时规定工程师的工作目录以及使用权限等。 check_timing、report_port—v等。检查综合约束是否

作者简介:牛英山(1976一)。男,辽宁省铁岭县人,工程师,硕士,主研方向:嵌入式微处理器设计、集成电路前端设计。

收稿日期:2008—05—05

˝(cid:242)•‰˚(cid:253)(cid:190)(cid:221)˝(cid:242)•‰˚(cid:253)(cid:190)(cid:221)-6· 微处理机 2009矩

完整的几个基本要素是是否创建时钟(create_clock), 线上插人专用的缓冲器和反向器,一般是CLK木和

是否设置输人延时(set—input—delay),是否设置输出 Cu(INV木等单元,来保证时钟网络的延时和所有由

延时(set_output_delay),是否设置输入变化时间(set— 时钟网络所驱动的触发器的时钟歪斜(dock skew)可

input_t瑚sition),是否设置输出负载(set_load)。是否 以满足设计约束的要求。这是由Astro工具完成的。

存在假路径(seLfalse_path),是否有多周期路径(∞t— 8)CTS后优化

multi_cycle),是否有异步电路(set_max_delay、set_rain 由于做时钟树综合要在版图中插入各种驱动强

_delay)等。检查综合约束是否正确的几个基本要素 度不同的驱动单元,这会对标准单元的位置产生影

是查看所设置的各种值是否正确,是否加到对应的目 响,因此在时钟树综合后必须对版图进行优化,才能

标上.是否留有足够的余量等。 保证设计的性能。这也是由As缸D工具完成的。这

3)时钟规划 一步骤的作用是为自动布线作最后的准备。

时钟规划的主要工作是分析时钟树的结构、时 9)布线及优化

钟的数量、触发器的数量、不同时钟之间的相互关系 经过CTS后优化,此时版图上各个宏单元的位

以及查找门控时钟的位置,目的是为时钟树综合作 置和方向以及标准单元的位置和方向已经确定。在

必要的准备,也是由PrimeTime工具完成的。进行 自动布线之前需要设置各层金属的方向和宽度,之

时钟规划常用的几个命令是all—fanin—flat—start— 后再用Astro进行自动布线,从而生成一个真正的

from、report_transitive_fanout等o 物理版图。

4)逻辑综合 10)物理验证

逻辑综合是RTL到GDSII设计流程中关键的环节 尽管由Astro生成了一个真正的物理版图,但

之一.主要工作是进行RTL设计的语法检查、转换成内 还需要根据工艺厂商提供的DRC、ERC等规则文件

部格式并将其映射到目标库上,进行逻辑实现和优化, 对版图进行最后的物理验证,目的是查找版图中存

是由DesignCompilar工具完成的。进行逻辑综合常用 在的各种物理问题。因为Astro在进行自动布局布

的几个命令是maaly匏、elaborate、compile一∞肌一tim- 线时只关心最基本的由工艺文件定义的设计规则,

这只是设计规则文件的一小部分,所以自动布局布

ing、report—tiIIling、write一8dc、write—milkyway、write—file

等。非常重要的一点是需要分析report_timing产生的 线过程中很可能产生违反其它规则的情形。这是由

报告,目的是查看—下设计中影响性能的关键路径,并 Hercules工具完成的。

初步判定一下综合约束是否过松或是过紧。如果过松 11)参数提取

或是过紧,都要适当修改综合约束来满足设计目标。 参数提取是用Star—RCXT工具对经过物理验

5)布局规划和电源规划 证后的版图进行单元之间连线的电阻和电容等寄生

布局规划的主要目的是确定设计中各个宏单元 参数的提取,生成SPEF、DSPF、RSPF等文件。可以

在版图中的位置和方向,作用是为布局布线提供必 给SPICE进行模拟仿真,也可以给PrimeTime再输

要准备,是由Astro工具完成的;电源规划的主要目 出SDF标准延时文件,进行静态时序分析或是进行

的是电压降(IR—drop)和电迁移(eleetromigration), 功能验证。

是由AstroRail工具完成的。 12)静态时序分析

6)布局优化及插入Dgr 静态时序分析是用PrimeTime工具对布局布线

布局及优化的主要工作是将标准单元放置到版 后的门级网表进行全芯片的时序分析,目的是计算

图上,此时各个宏单元在版图中的位置和方向已经 出设计中所有时序路径的延时信息,以查找在没有

确定,同时对标准单元在版图上的位置进行优化,作 测试向量输入的情况下是否有时序违反的情况。如

用是为布局布线提供进一步的准备,是由Physical— 果有则要分析是何原因引起的,在哪条路径上,并及

Compiler工具完成的;之后再将DFT插入到设计中, 时反馈给前端的工程师。如果没有,则说明设计已

从而可以对加工后的芯片进行生产测试;然后还得 经达到系统要求。

对标准单元进行优化,因为插入的DFT可能会影响 13)功能验证

设计的性能。 功能验证将SDF反标到布局布线后的门级网

7)时钟树综合CTS 表上,在VCS仿真工具中进行数字仿真。目的是验

时钟树综合是对时钟网络进行综合,即在时钟 证在有测试向量输入的情况下, (下转第9页)

˝(cid:242)•‰˚(cid:253)(cid:190)(cid:221)˝(cid:242)•‰˚(cid:253)(cid:190)(cid:221)叶君青等:一种宽调节范围的CMOS二级压控振荡器设计 ·9·

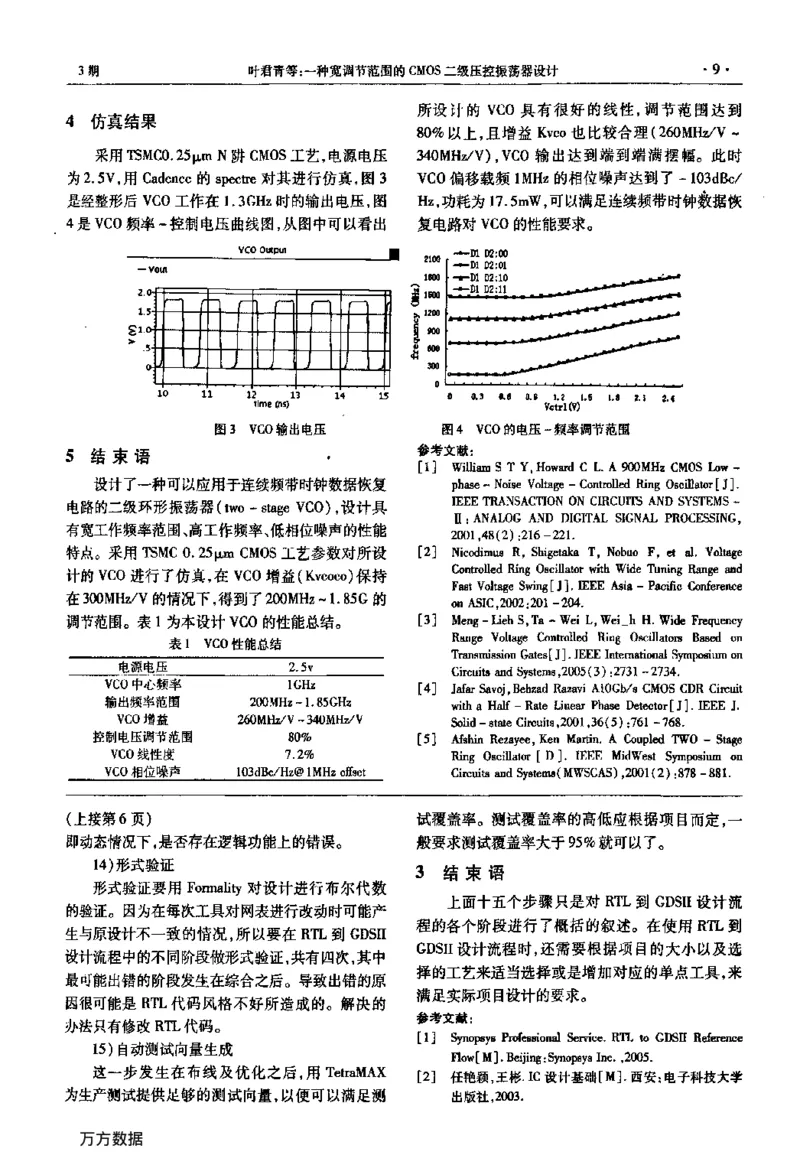

所设计的VCO具有很好的线性,调节范围达到

4仿真结果

80%以上,且增益Kveo也比较合理(260MHz/V一

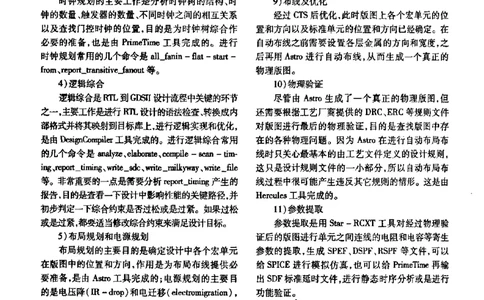

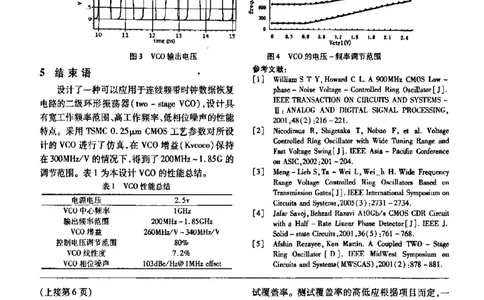

采用TSMC0.25i山m N阱CMOS工艺,电源电压 340MHz/V),VCO输出达到端到端满摆幅。此时

为2.5V,用Cadence的spectre对其进行仿真,图3 VCO偏移载频1MHz的相位噪声达到了一103dBc/

是经整形后VCO工作在1.3GHz时的输出电压,图 Hz,功耗为17.5mw,可以满足连续频带时钟数据恢

4是VCO频率一控制电压曲线图,从图中可以看出 复电路对VCO的性能要求。

——一!竺!竺竺

‘。。。’’。。。。。。。。。。。。_--__--_-_________-·---—-___._______l____________.————一_ 2l∞'Im

—VOUt

2 啪湖

1. 抛

£1¨

,

^革g各g吕D者

蛳啪蛳

o

o oJ¨¨出∽1J 1J幺1 2·‘

vctrl∽

图3 VCO输出电压 图4 VCO的电压一频率调节范围

5结束语 参考文献:

Il i Willi锄S TY,Howard C L.A 900MHz CMOS Low—

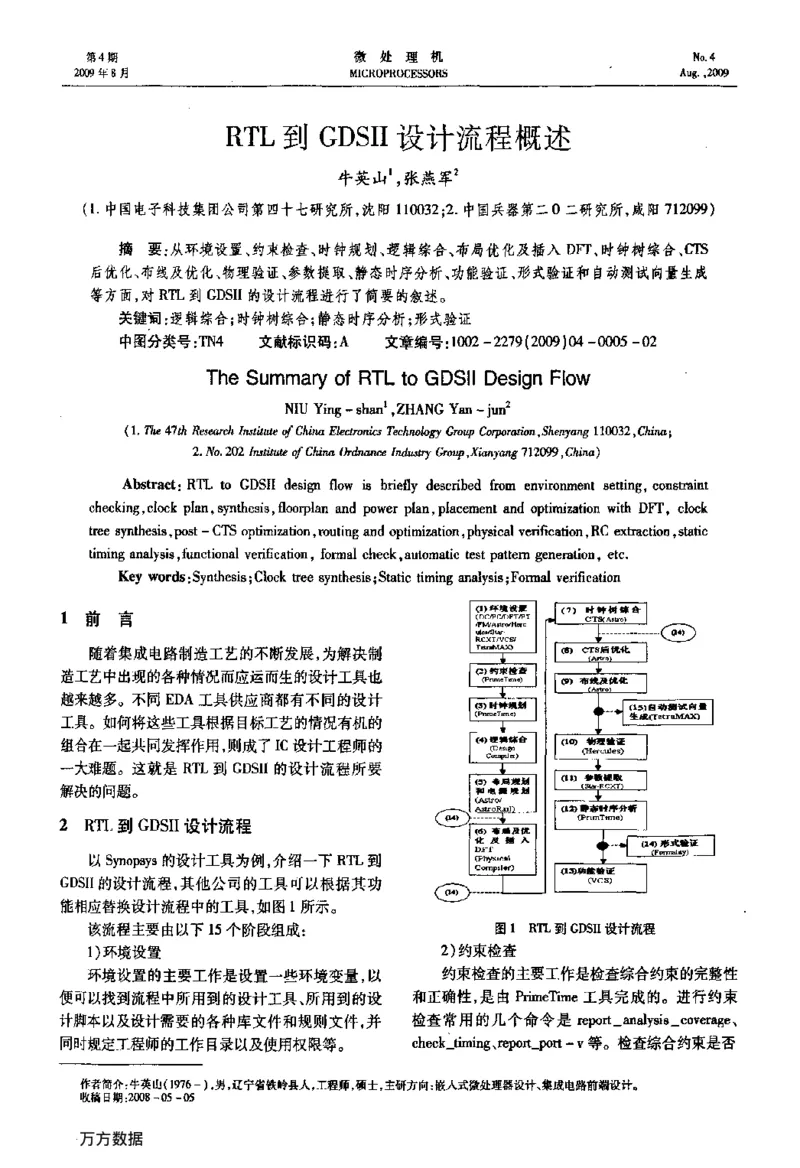

设计了一种可以应用于连续频带时钟数据恢复 phase—Noise Voltage—Contmled Ring Osc S il Y la m to M r S [J 一 ].

电路的二级环形振荡器(two—stage VCO),设计具 IEEETRANSAC’110N 0N CIRCUl7rlS AND

1I:ANALOIG AND DIGITAL SIGNAL PRoCESSING。

有宽工作频率范围、高工作频率、低相位噪声的性能

2001.48(2):216—221.

特点。采用TSMC 0.25wm CMOS工艺参数对所设 [2] Nicodimus R,Shigetaka T,Nobuo F,et a1.Voltage

计的VCO进行了仿真,在VCO增益(Kveoco)保持 Conuoled Ring Oscillator with Wide TuningRange and

Fast Voltage Swing[J].mEE Asia—Pacific Conference

在300MHz/V的情况下,得到了200MHz一1.85G的

on ASIC.2002:201—204.

调节范围。表1为本设计VCO的性能总结。 [3] Meng—Lieh S,’I'a—wei L,Ⅵrei—h H.Wide Frequency

表1 VCO性能总结 Range Voltage Controlled Ring Oscillators Based on

Transmission GatesI JI.IEEEIntemational Symposiumon

电源电压 2.5v CircuitsandSystems,2005(3):273l一2734.

VCO中心频率 1GHz [4] Jafar Savoj,Behzad Razavi A10Gb/s CMOSCDR Circuit

输出频率范围 200MHz~1.85GHz “th aHall—Rate Linear Phase DetectorfJ1.IEEE J.

VCO增益 260MH五/V一3410MHz/V Solid—state Circuits,200l,36(5):761—768.

控制电压调节范围 80% [5] Mshin Rezayee,Ken Martin.A Coupled TWO—Stage

VCO线性度 7.2% mng Oscillator[D 1.IEEE MidWest Symposium on

VCO相位噪声 103dBc/Hz@lMHzoffset Circuits andSystems(MWSCAS),200l(2):878—881.

(上接第6页) 试覆盖率。测试覆盖率的高低应根据项目而定,一

即动态情况下,是否存在逻辑功能上的错误。 般要求测试覆盖率大于95%就可以了。

14)形式验证

3结束语

形式验证要用Formality对设计进行布尔代数

上面十五个步骤只是对RTL到GDSII设计流

的验证。因为在每次工具对网表进行改动时可能产

程的各个阶段进行了概括的叙述。在使用RTL到

生与原设计不一致的情况,所以要在RTL到GDSH

GDSII设计流程时,还需要根据项目的大小以及选

设计流程中的不同阶段做形式验证,共有四次,其中

择的工艺来适当选择或是增加对应的单点工具,来

最可能出错的阶段发生在综合之后。导致出错的原

满足实际项目设计的要求。

因很可能是RTL代码风格不好所造成的。解决的

参考文献:

办法只有修改RTL代码。

[1]Synopsys Professional Service.RTL tO GDSII Reference

15)自动测试向量生成

Flow[M].Beijing:SynopsysInc.,2005.

这一步发生在布线及优化之后,用TetraMAX

[2]任艳颖,王彬.Ic设计基础[M].西安:电子科技大学

为生产测试提供足够的测试向量,以便可以满足测 出版社。2003.

˝(cid:242)•‰˚(cid:253)(cid:190)(cid:221)˝(cid:242)•‰˚(cid:253)(cid:190)(cid:221)