文档内容

数 电 试 题

选择题:

1.下列四个数中,与十进制数(163) 不相等的是( D )

10

A、(A3) B、(10100011)

16 2

C、(000101100011) D、(203)

8421BCD 8

2.N个变量可以构成多少个最小项( C )

A、N B、2N

C、2N D、2N-1

3.下列功能不是二极管的常用功能的是( C )

A、检波 B、开关

C、放大 D、整流

4..将十进制数 转换成八进制数是 ( B )

A、20 B、22

C、21 D、23

5.译码器的输入地址线为4根,那么输出线为多少根( C )

A、8 B、12

C、16 D、20

6.能把正弦信号转换成矩形脉冲信号的电路是(D )

A、多谐振荡器 B、D/A转换器

C、JK触发器 D、施密特触发器

7.三变量函数 的最小项表示中不含下列哪项 ( A )

A、m2 B、 m5

C、m3 D、 m7

8.用PROM来实现组合逻辑电路,他的可编程阵列是( B )

A、与阵列 B、或阵列

C、与阵列和或阵列都可以 D、以上说法都不对

9.A/D转换器中,转换速度最高的为( A )转换

A、并联比较型 B、逐次逼近型

C、双积分型 D、计数型

10.关于PAL器件与或阵列说法正确的是 ( A )

A、 只有与阵列可编程 B、 都是可编程的

C、 只有或阵列可编程 D、 都是不可编程的

11. 当三态门输出高阻状态时,输出电阻为 ( A )

A、无穷大 B、约100欧姆

C、无穷小 D、约10欧姆

112为使采样输出信号不失真地代表输入模拟信号,采样频率 和输入模拟信号

的最高频率 的关系是(C )

A、 ≥ B、 ≤

C、 ≥2 D、 ≤2

13. 下列说法不正确的是( C)

A.集电极开路的门称为OC门

B.三态门输出端有可能出现三种状态(高阻态、高电平、低电平)

C.OC门输出端直接连接可以实现正逻辑的线或运算

D.利用三态门电路可实现双向传输

14. 以下错误的是( B )

A.数字比较器可以比较数字大小

B.实现两个一位二进制数相加的电路叫全加器

C.实现两个一位二进制数和来自低位的进位相加的电路叫全加器

D.编码器可分为普通全加器和优先编码器

15. 下列描述不正确的是(A )

A.触发器具有两种状态,当Q=1时触发器处于1态

B.时序电路必然存在状态循环

C.异步时序电路的响应速度要比同步时序电路的响应速度慢

D.边沿触发器具有前沿触发和后沿触发两种方式,能有效克服同步触发器的空翻现象

16.离散的,不连续的信号,称为( B )。

A.模拟信号 B.数字信号

17.组合逻辑电路通常由( A )组合而成。

A.门电路 B.触发器 C.计数器

18.8 线—3 线优先编码器的输入为 I —I ,当优先级别最高的 I 有效时,其输出

0 7 7

的值是( C )。

A.111 B.010 C.000 D.101

19.十六路数据选择器的地址输入(选择控制)端有( C )个。

A.16 B.2 C.4 D.8

20.一位8421BCD码译码器的数据输入线与译码输出线的组合是( C )。

A.4:6 B.1:10 C.4:10 D.2:4

21.函数 的结果是 ( C )

A. B.

C. D.

222.ROM属于( A )。

A.组合逻辑电路 B.时序逻辑电路

23.有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲

CP作用下,四位数据的移位过程是( A )。

A.1011--0110--1100--1000—0000 B.1011--0101--0010--0001—0000

24. 一个二进制序列检测电路,当输入序列中连续输入5位数码均为1时,电路输出1,

则同步时序电路最简状态数为 ( B )

A. 4 B. 5

C. 6 D. 7

25. 可以直接现与的器件是 ( A )

A. OC门 B. I2L门

C. ECL门 D. TTL门

26. 16个触发器构成计数器,该计数器可能的最大计数模值是( D )

A. 16 B. 32

C.162 D. 216

27. 用1K×1位的RAM扩展成4K×2位应增加地址线( B )根。

A.1 B.2

C.3 D.4

28. 能把正弦信号转换成矩形脉冲信号的电路是( D )

A.多谐振荡器 B.D/A转换器

C.JK触发器 D.施密特触发器

29. 接通电源就能输出矩形脉冲波形的是( A )

A.多谐振荡器 B.D/A转换器

C.JK触发器 D.施密特触发器

30.在函数F=AB+CD的真值表中,F=1的状态有多少个?( D )。

A、2 B、4 C、6 D、7 E、16

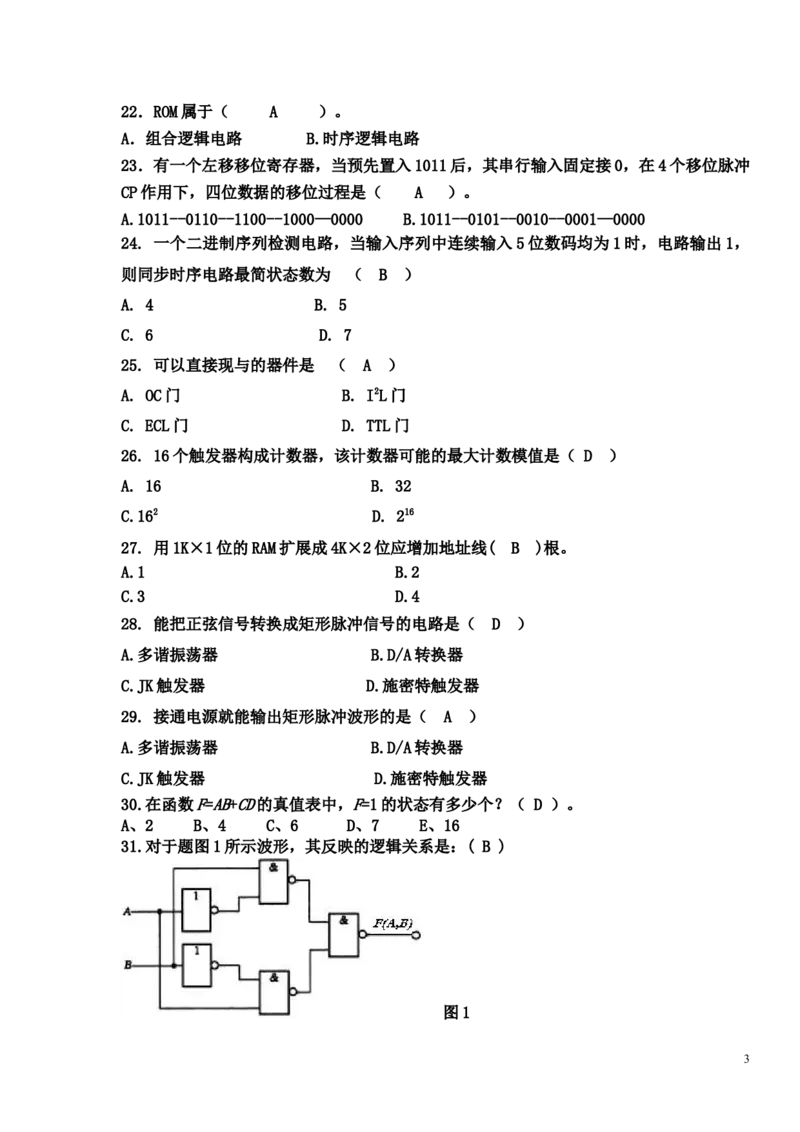

31.对于题图1所示波形,其反映的逻辑关系是:( B )

图1

3A、与非关系;B、异或关系;C、同或关系;D、或关系;E、无法判断。

32、矩形脉冲信号的参数有 D 。

A.周期 B.占空比 C.脉宽 D.以上都是

33、电路的输出态不仅与当前输入信号有关,还与前一时刻的电路状态有关,这种电路为

( B )。

A.组合电路 B.时序电路

34、米利和莫尔型时序电路的本质区别是( B )

A、没有输入变量。

B、当时的输出只和当时电路的状态有关,和当时的输入无关。

C、没有输出变量。

D、当时的输出只和当时的输入有关,和当时电路状态无关。

35、十进制数25用8421BCD码表示为 B 。

A.10 101 B.0010 0101 C.100101 D.1010

36、下列各函数等式中无冒险现象的函数式有 D 。

A. B. C. D.

E.

37、在下列逻辑电路中,不是组合逻辑电路的有 D 。

A.译码器 B.编码器 C.全加器 D.寄存器

38、把一个五进制计数器与一个四进制计数器串联可得到 D 进制计数器。

A.4 B.5 C.9 D.20

39、N 个触发器可以构成最大计数长度(进制数)为 D 的计数器。

A.N B.2N C.N2 D.2N

40、同步时序电路和异步时序电路比较,其差异在于后者 B 。

A.没有触发器 B.没有统一的时钟脉冲控制

C.没有稳定状态 D.输出只与内部状态有关

41、寻址容量为 16K×8的RAM需要 C 根地址线。

A.4 B.8 C.14 D.16 E.16K

42、只读存储器 ROM 中的内容,当电源断掉后又接通,存储器中的内容 D 。

A.全部改变 B.全部为 0 C.不可预料 D.保持不变

43、将一个时间上连续变化的模拟量转换为时间上断续(离散)的模拟量的过

程称为 A 。

A.采样 B.量化 C.保持 D.编码

44、若某 ADC 取量化单位△= ,并规定对于输入电压 ,在 0≤ < 时,

认为输入的模拟电压为 0V,输出的二进制数为 000,则 ≤ < 时,

4输出的二进制数为 B 。

A.001 B.101 C.110 D.111

45、指出下列电路中能把串行数据转换为并行数据的是( C )

A、JK 触发器 B、3 线-8 线译码器

C、移位寄存器 D、十进制计数器

46、逻辑函数F= = A 。

A.B B.A C. D.

47、在何种输入情况下,“与非”运算的结果是逻辑 0。 D

A.全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是1

48、若在编码器中有 50 个编码对象,则要求输出二进制代码位数为 B 位。

A.5 B.6 C.10 D.50

49、在下列逻辑电路中,不是组合逻辑电路的有 D 。

A.译码器 B.编码器 C.全加器 D.寄存器

50、下列逻辑电路中为时序逻辑电路的是 C 。

A.变量译码器 B.加法器 C.数码寄存器 D.数据选择器

51、随机存取存储器具有 A 功能。

A.读/写 B.无读/写 C.只读 D.只写

52、寻址容量为 16K×8的RAM需要 C 根地址线。

A.4 B.8 C.14 D.16 E.16K

53、用二进制码表示指定离散电平的过程称为 D 。

A.采样 B.量化 C.保持 D.编码

54、将幅值上、时间上离散的阶梯电平统一归并到最邻近的指定电平的过程称

为 B 。

A.采样 B.量化 C.保持 D.编码

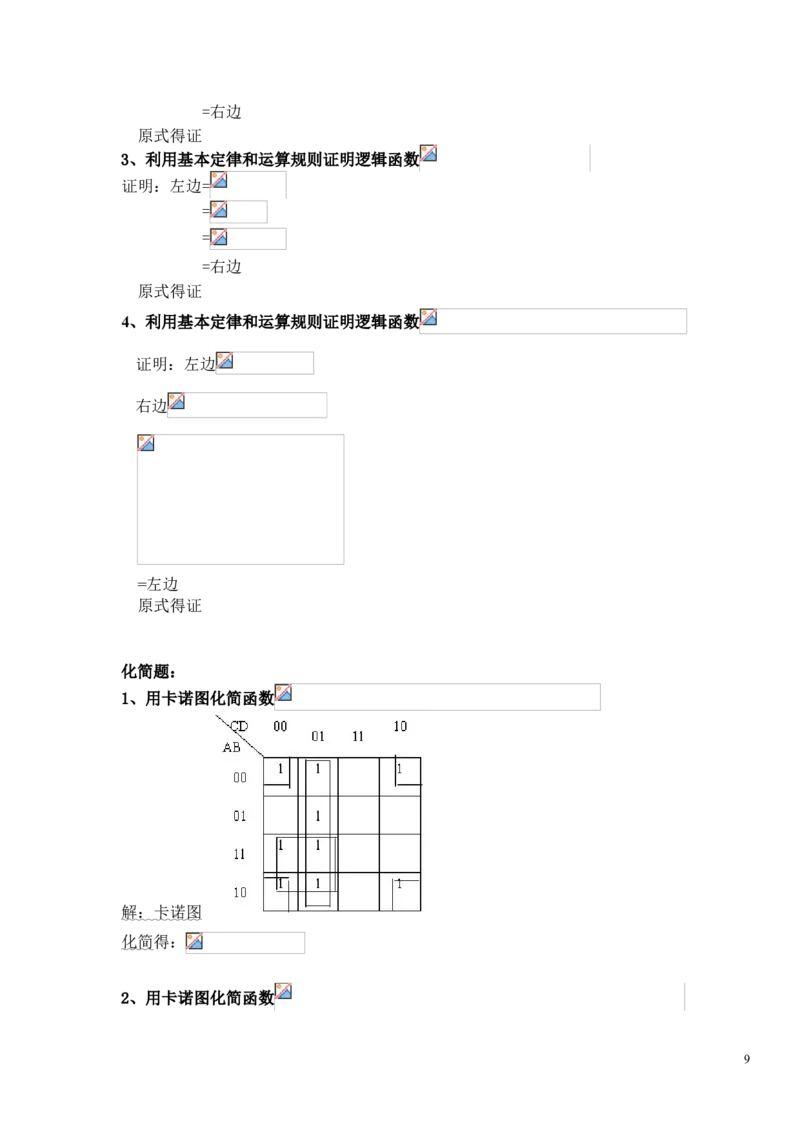

填空题:

1. 数制转换: (8F) = (143 ) = (10001111 ) = (217 ) 。

16 10 2 8

2. 有一数码10010011,作为自然二进制数时,它相当于十进制数(147),作为8421BCD

码时,它相当于十进制数(93)。

3. 已知某函数 ,该函数的反函数 =( )

4. 如果对键盘上108个符号进行二进制编码,则至少要(7)位二进制数码。

5. 在TTL门电路的一个输入端与地之间接一个10K电阻,则相当于在该输入端输入(高)

电平;在CMOS门电路的输入端与电源之间接一个 1K电阻,相当于在该输入端输入

(高)电平。

56.晶体三极管在工作时,发射结和集电结均处正向偏置,该晶体管工作在(饱和导通)状

态。

7. 74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A A A =110时,

2 1 0

输出 应为(10111111)。

8. 一个10位地址码、8位输出的ROM,其存储容量为(8K 或213)。

9.将一个包含有 32768个基本存储单元的存储电路设计 16位为一个字节的 ROM。该

ROM有(11)根地址线,有(16)根数据读出线。

10 .能够实现“线与”的TTL门电路叫(OC门)。

11.按逻辑功能的不同特点,数字电路可分为(组合逻辑电路) 和(时序逻辑电路)两大

类。

12.在逻辑电路中,三极管通常工作在( 饱和)和( 截止)状态

13.(406) =(0100 0000 0110)

10 8421BCD

14.一位数值比较器的逻辑功能是对输入的( A 和 B 两个)数据进行比较,它有(

Y )、( Y )、( Y )三个输出端。

A>B AV 不变 不变

CC CC

1 >V >V 低 导通

CC CC

V CC u I

8 4 2

V

7 V CC 3

CC

D 1

2 V

u

I 555 3

3 CC

0

t

6 OUT u O

TH

V SS CO

u

1 5 o

0.01μF

0 t

解(1)该电路组成施密特触发器。

(2)波形图

u

I

2

V

CC

3

1

V

3 CC t

0

u

o

0 t

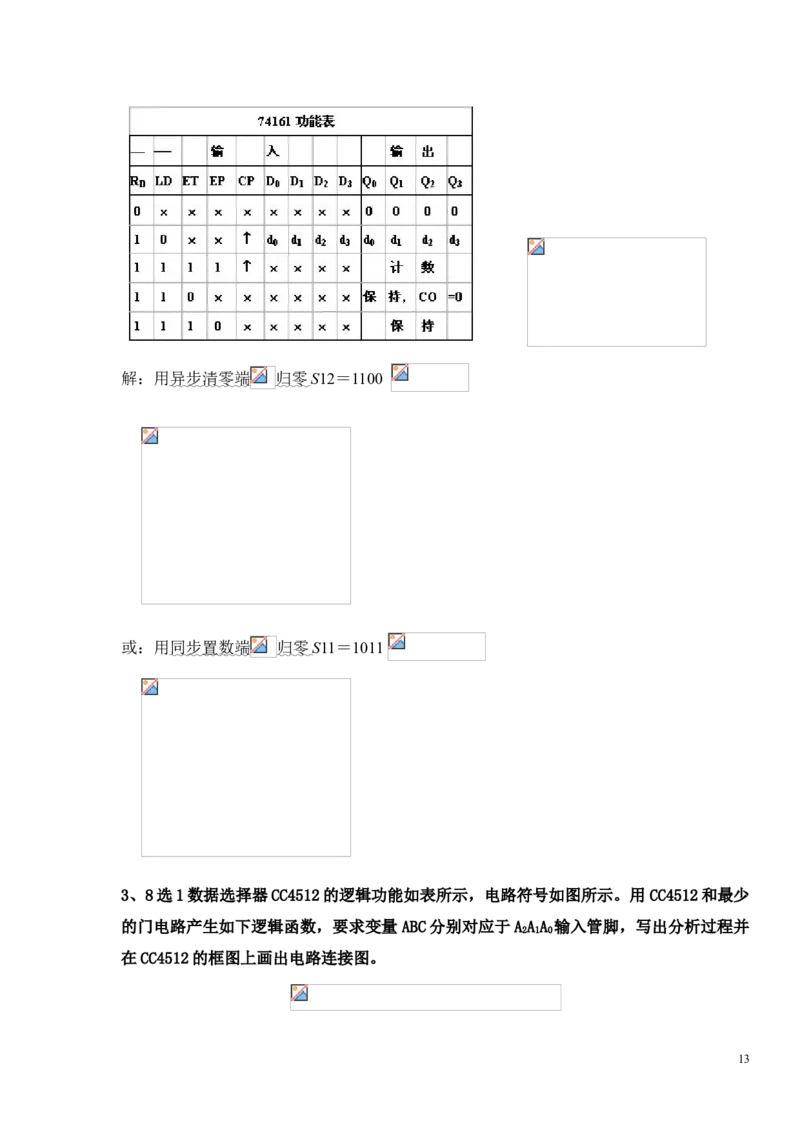

2、用74LS161来构成一个十二进制计数器。74LS161的功能表如图所示。

12解:用异步清零端 归零 S12=1100

或:用同步置数端 归零 S11=1011

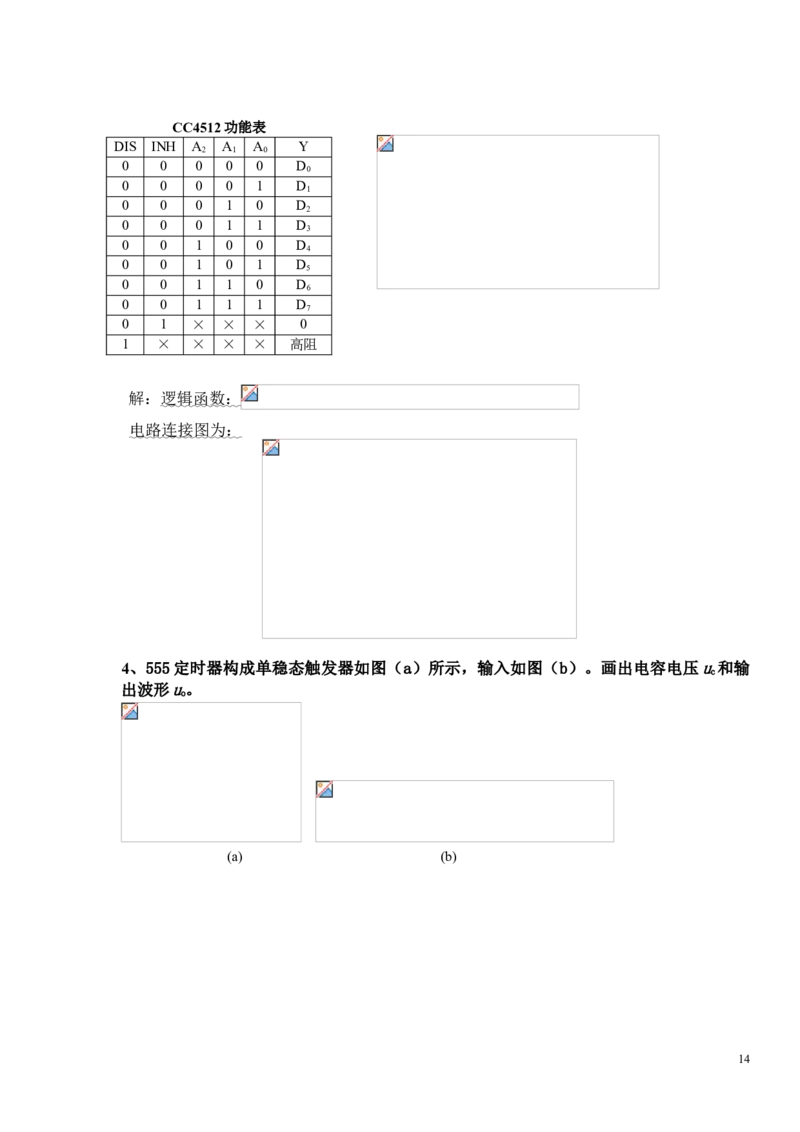

3、8选1数据选择器CC4512的逻辑功能如表所示,电路符号如图所示。用 CC4512和最少

的门电路产生如下逻辑函数,要求变量 ABC分别对应于A A A 输入管脚,写出分析过程并

2 1 0

在CC4512的框图上画出电路连接图。

13CC4512功能表

DIS INH A A A Y

2 1 0

0 0 0 0 0 D

0

0 0 0 0 1 D

1

0 0 0 1 0 D

2

0 0 0 1 1 D

3

0 0 1 0 0 D

4

0 0 1 0 1 D

5

0 0 1 1 0 D

6

0 0 1 1 1 D

7

0 1 × × × 0

1 × × × × 高阻

解:逻辑函数:

电路连接图为:

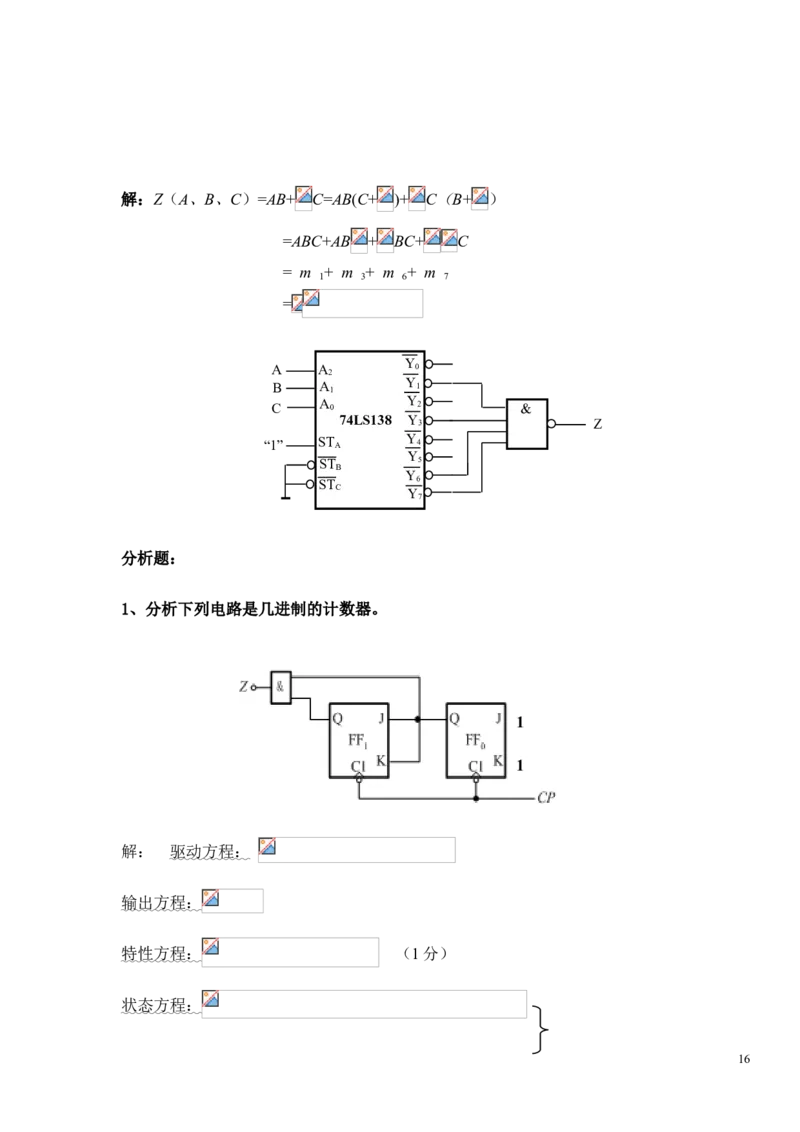

4、555定时器构成单稳态触发器如图(a)所示,输入如图(b)。画出电容电压u和输

c

出波形u。

o

(a) (b)

14解:

5、用512×4的RAM扩展组成一个2K×8位的存储器.需要几片RAM,试画出它们的连接

图,用图示RAM实现。

答:需要8片RAM,同时做字扩展和位扩展。连接图如下:

6、试用3线—8线译码器74LS138和门电路实现下列函数。

Z(A、B、C)=AB+ C

Y

A 0

2

Y

A 1

1

A 0 Y 2

74LS138 Y

3

ST A Y 4

Y

ST 5

B

Y

ST 6

C Y 15

7解:Z(A、B、C)=AB+ C=AB(C+ )+ C(B+ )

=ABC+AB + BC+ C

= m + m + m + m

1 3 6 7

=

Y

A A 0

2

Y

B A 1

1

C A 0 Y 2 &

74LS138 Y 3 Z

“1” ST A Y 4

Y

ST 5

B

Y

ST 6

C Y

7

分析题:

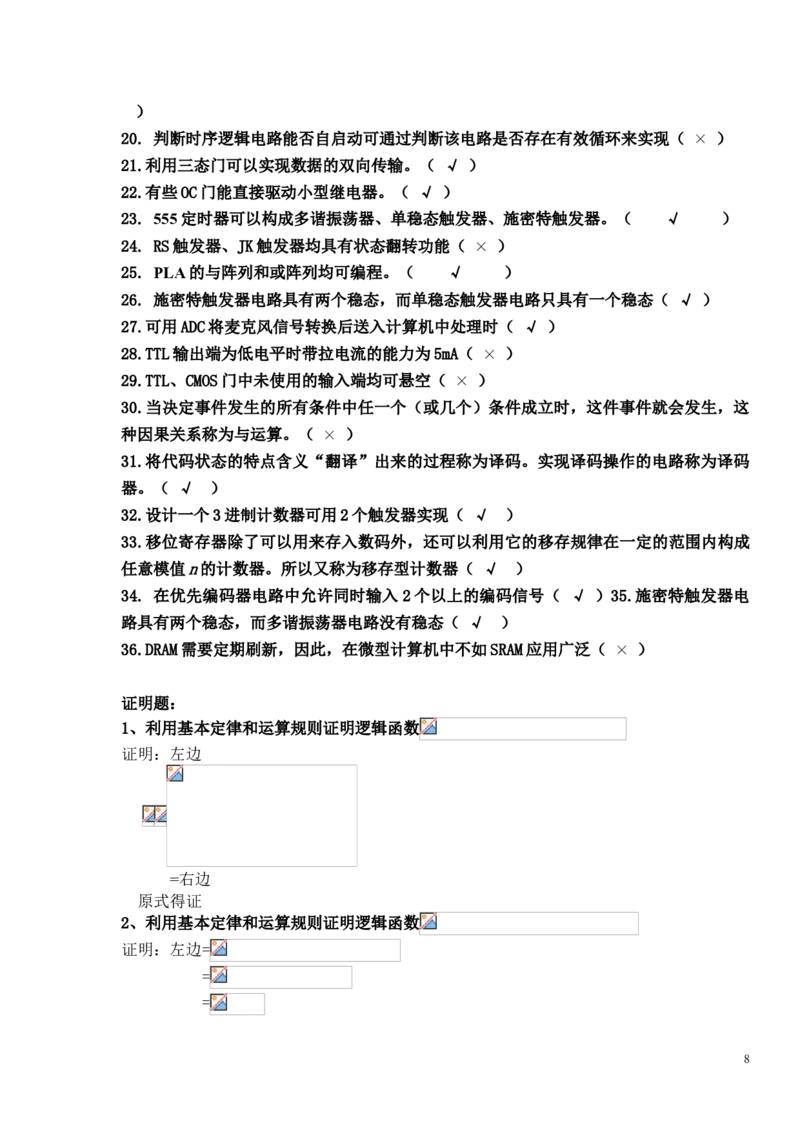

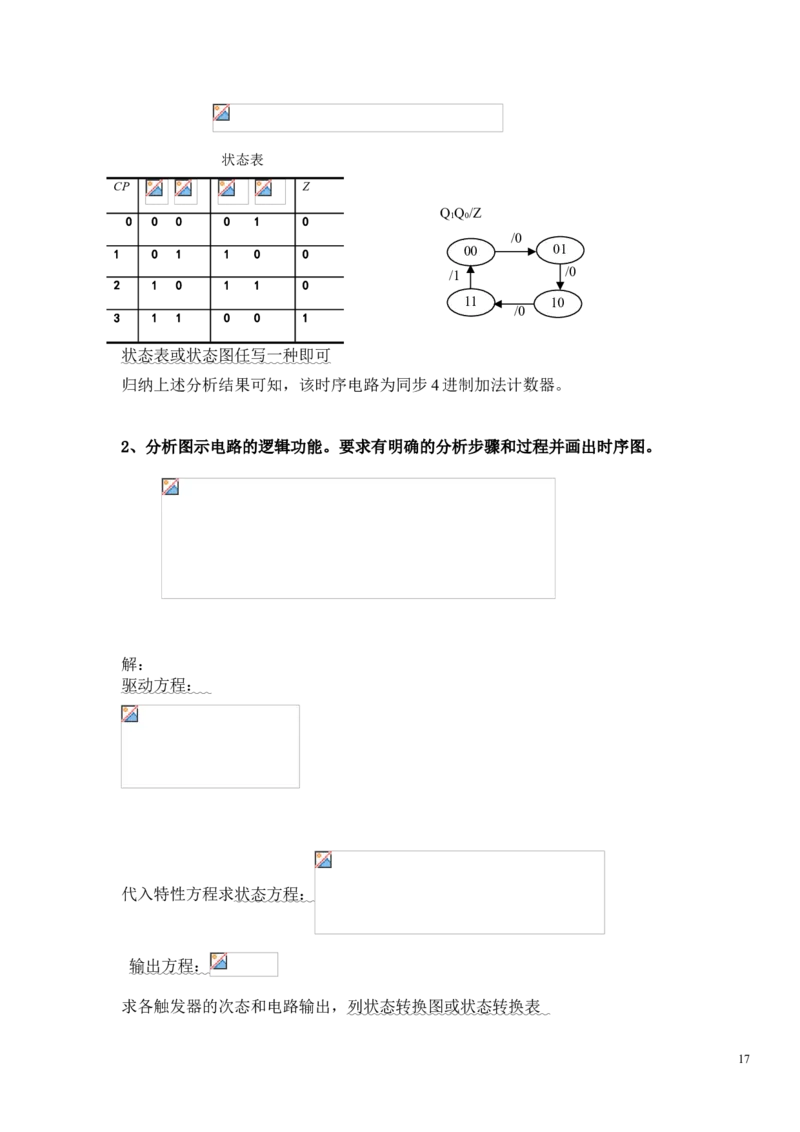

1、分析下列电路是几进制的计数器。

1

1

解: 驱动方程:

输出方程:

特性方程: (1分)

状态方程:

16状态表

CP Z

Q Q /Z

0 0 0 0 1 0 1 0

/0

1 0 1 1 0 0 00 01

/1 /0

2 1 0 1 1 0

11 10

/0

3 1 1 0 0 1

状态表或状态图任写一种即可

归纳上述分析结果可知,该时序电路为同步4进制加法计数器。

2、分析图示电路的逻辑功能。要求有明确的分析步骤和过程并画出时序图。

解:

驱动方程:

代入特性方程求状态方程:

输出方程:

求各触发器的次态和电路输出,列状态转换图或状态转换表

17时序图:

电路功能:

有效循环的6个状态分别是0~5这6个十进制数字的格雷码,并且在时钟脉冲 CP的作用

下,这6个状态是按递增规律变化的,即:

000→001→011→111→110→100→000→…

所以这是一个用格雷码表示的六进制同步加法计数器。当对第6个脉冲计数时,计数器

又重新从000开始计数,并产生输出Y=1。

3、分析图示电路的逻辑功能。

18解:此电路为同步时序电路

驱动方程: ;

输出方程:

T触发器的特性方程:

将各触发器的驱动方程代入,即得电路的状态方程:

通过计算得状态表或状态转换图:

时序图:

电路功能:

由状态图可以看出,当输入X =0时,在时钟脉冲CP的作用下,电路的4个状态按递增

规律循环变化,即:

00→01→10→11→00→…

当X=1时,在时钟脉冲CP的作用下,电路的4个状态按递减规律循环变化,即:

00→11→10→01→00→…

可见,该电路既具有递增计数功能,又具有递减计数功能,是一个 2位二进制同步可逆

19计数器。

4、8位A/D输入满量程为 10V,当输入下列电压时,数字量的输出分别为多少?(1)

3.5V;(2)7.08V;(3)5.97V

解:(1)第一步,当 V时,因为V>V,所以取d =0,存储。

N X 7

第二步,当 V时,因为VV,所以取d =0,存储。

N X 5

…

如此重复比较下去,经过 8个时钟脉冲周期,转换结束,最后得到 A/D转换器的转换

结果d ~d =01011001,则该数字所对应的模拟输出电压为

7 0

同理(2)10110101=7.0703125V

(3)10011000=5.9375V

设计题:

1、用与非门设计一个举重裁判表决电路。设举重比赛有3个裁判,一个主裁判和两个副

裁判。杠铃完全举上的裁决由每一个裁判按一下自己面前的按钮来确定。只有当两个或

两个以上裁判判明成功,并且其中有一个为主裁判时,表明成功的灯才亮。

解:设主裁判为变量A,副裁判分别为B和C;表示成功与否的灯为Y,根据逻辑要求列

出真值表

逻辑表达式

Y=AB+AC

逻辑电路图:

202、设计一个按自然态序变化的7进制同步加法计数器,计数规则为逢七进一,产生一个

进位输出。

解:建立原始状态图:

因需用3位二进制代码,选用3个CP下降沿触发的JK触发器,分别用FF0、FF1、FF2

表示。由于要求采用同步方案,故时钟方程为:

卡诺图化简输出方程:

卡诺图化简 状态方程:

的卡诺图也可以画在一个图中。

21得状态方程: 比较特性方程:

得驱动方程:

、

、

、

电路图并检查电路能否自启动:

将111代入状态方程得次态为000,此电路能自启动。

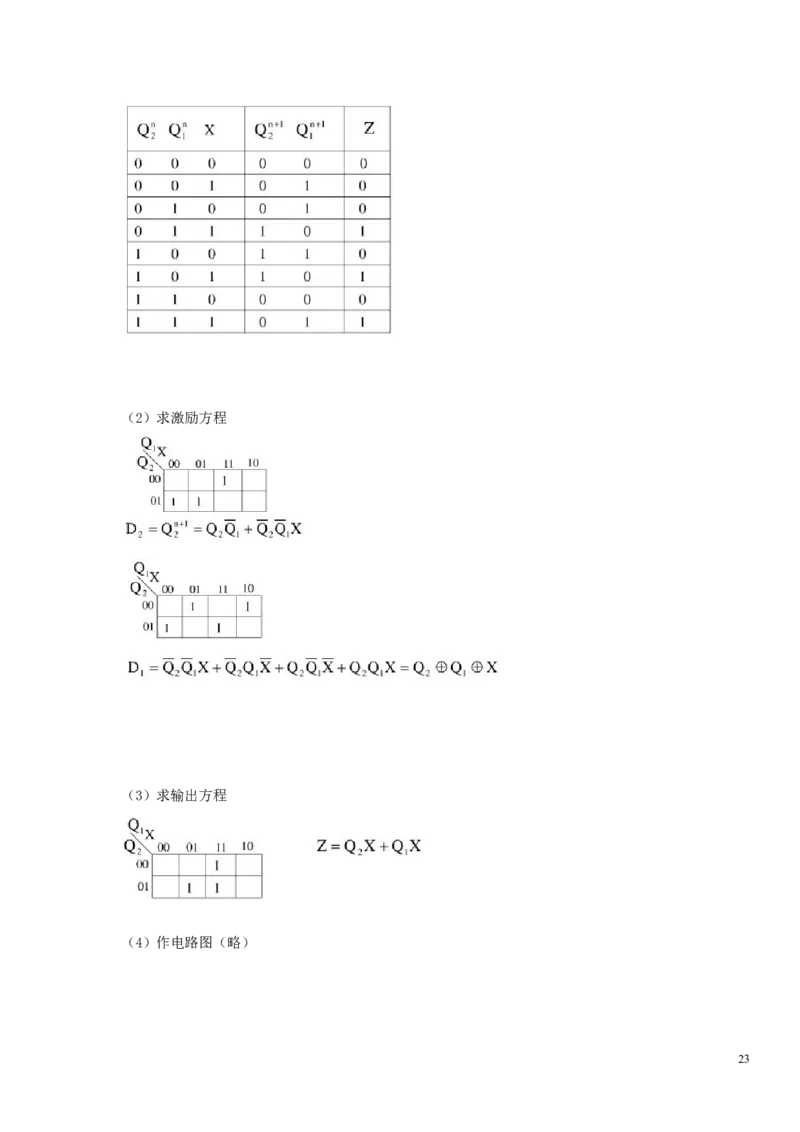

3、已知某同步时序电路状态图如图所示,完成以下任务(1)做出状态转换真值表;(2)若用D触

发器实现,请求出相应的激励方程;(3)求输出方程;(4)画出电路图;

解:(1)状态转换真值表

22(2)求激励方程

(3)求输出方程

(4)作电路图(略)

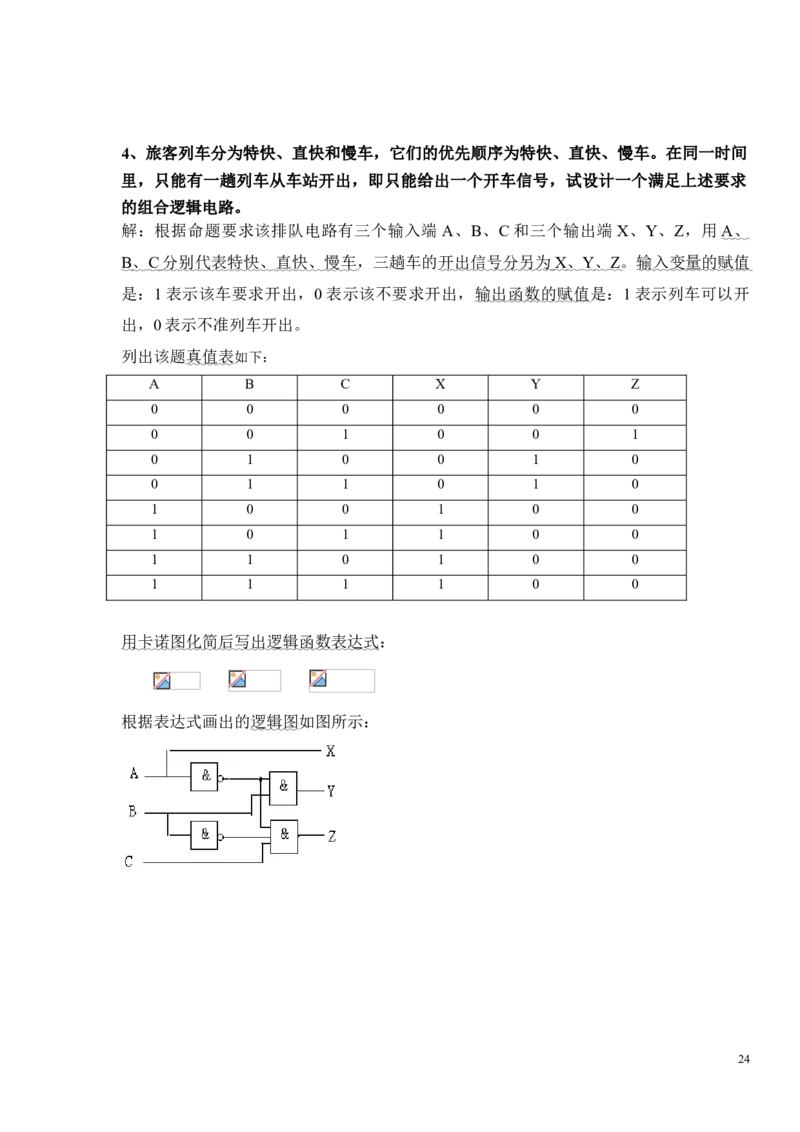

234、旅客列车分为特快、直快和慢车,它们的优先顺序为特快、直快、慢车。在同一时间

里,只能有一趟列车从车站开出,即只能给出一个开车信号,试设计一个满足上述要求

的组合逻辑电路。

解:根据命题要求该排队电路有三个输入端 A、B、C和三个输出端 X、Y、Z,用 A 、

B 、 C 分别代表特快、直快、慢车 ,三趟车的 开出信号分另为 X 、 Y 、 Z 。输入变量的赋值

是:1表示该车要求开出,0表示该不要求开出,输出函数的赋值是:1表示列车可以开

出,0表示不准列车开出。

列出该题真值表如下:

A B C X Y Z

0 0 0 0 0 0

0 0 1 0 0 1

0 1 0 0 1 0

0 1 1 0 1 0

1 0 0 1 0 0

1 0 1 1 0 0

1 1 0 1 0 0

1 1 1 1 0 0

用卡诺图化简后写出逻辑函数表达式:

根据表达式画出的逻辑图如图所示:

24