兄弟们,最近在搞 AI 算力卡或高阶 GPU 加速卡 Vcore 供电的肯定深有体会:新一代硅片的算力是上去了,但功耗也彻底放飞自我,核心电流动辄 1000A+。更要命的是,板级 XY 轴空间几乎被高速信号走线(PCIe 5.0/6.0)和 HBM 内存彻底榨干。

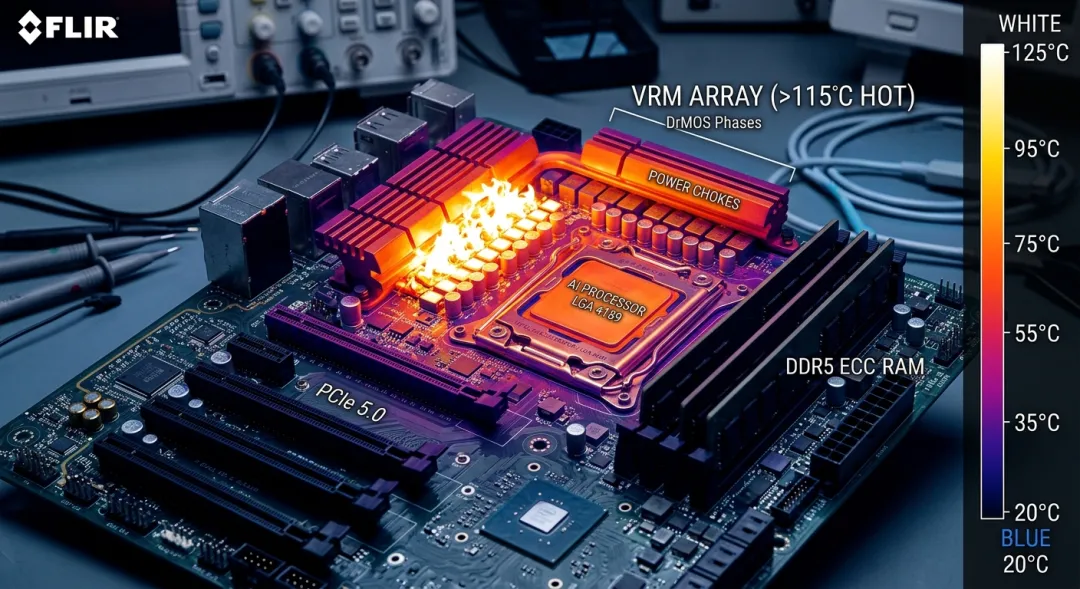

这就导致多相电源(Multi-phase POL)只能被迫在极端受限的面积内高密度排布。跑全负载动态拉载测试(Load Transient)时,极端的 di/dt 阶跃不仅考验环路响应,更考验散热。传统底面散热的 DrMOS 把热量全排给 PCB,导致热成像仪上红通通一片,动不动就触发过温降频(Thermal Throttling),甚至连累旁边的光模块或高速信号链。

不想因为热撞墙和 EMI 辐射超标反复 Re-spin(改板)?今天我们来深度拆解长工微(Innovision)针对高密度 PDN(电源分配网络)推出的 90A 智能功率级模块 (Smart Power Stage),看看极客级的封装与内部架构如何帮研发在 Design-in 阶段“一次过检”。

破局点 1:Top-side Cooling 顶层散热,直接切断 PCB 热传导路径

传统的 PQFN 封装 DrMOS,习惯将底部的 Thermal Pad 直接大面积焊在 PCB 上。在 1000A 级别的多相阵列中,这意味着巨大的热量被强行注入高热阻的玻纤板材中,把 PCB 变成了一个巨型“烤炉”。

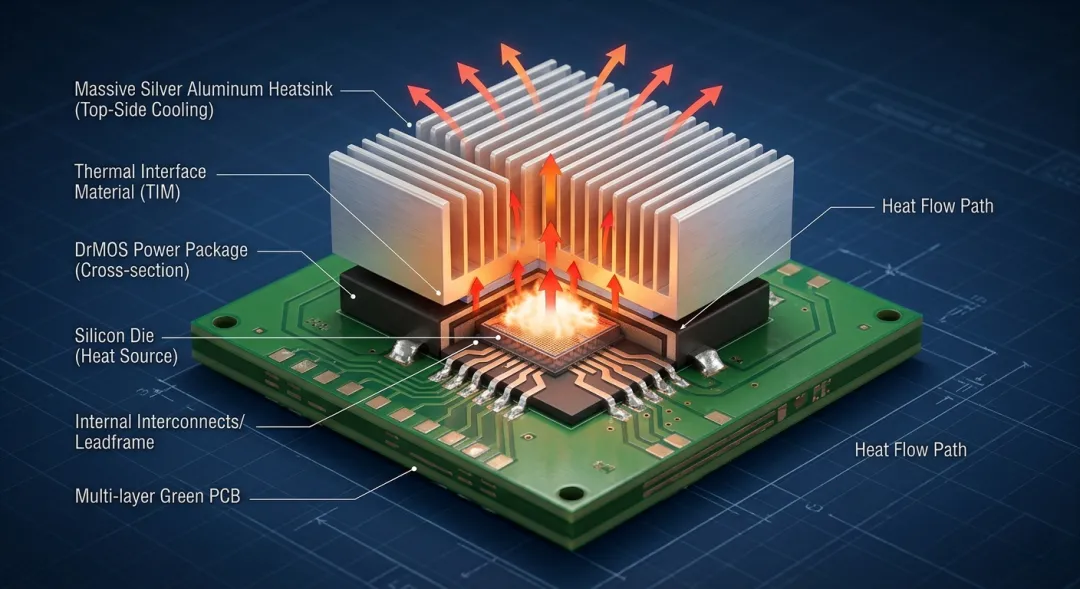

长工微这颗 90A DrMOS直接采用了 Top-side Cooling(顶层散热) 倒装封装架构。

从物理结构上看,它将发热量最大的功率 MOSFET 晶圆倒扣,顶层设计了裸露的金属散热焊盘。热流向(Thermal Path)被彻底改变:热量不再向下“淤积”在 PCB 内,而是向上通过导热界面材料(TIM)直接传导至顶部的高效散热器(Heatsink)或液冷冷板(Cold Plate)。

结合极低的结到顶部热阻($R_{\theta JC(top)}$),在同等满载工况下,此架构能将芯片结温(Tj)和 PCB 板级温度显著降低几十度。这给系统架构师释放了极其宝贵的热设计余量,直接消灭了因局部过热导致的系统级降频。

破局点 2:极致 3D 集成压榨寄生电感,干掉 SW 节点高频振铃 (Ringing)

做大功率高频降压(Buck)的兄弟都知道,寄生电感(Parasitic Inductance)是万恶之源。尤其在几十安培的开关瞬间,回路中的寄生电感 $L_{loop}$ 会在 Switch Node(SW 节点)激发出极高的电压尖峰和高频振铃(Ringing),这不仅是 EMI 辐射测试(RE/CE)挂科的直接原因,还会大幅增加开关损耗。

长工微通过极其紧凑的 3D 封装工艺,将内部的高边管(High-side FET)、低边管(Low-side FET)与驱动器(Driver)进行了超高密度集成。不仅内部核心的 $R_{DS(on)}$极低,更关键的是,它将 Gate Drive 走线和功率回路的寄生电感压榨到了物理极限。

从实测波形可以清晰看到,即便在 1MHz 以上的高频开关下,其 SW 节点波形依然极其干净。尖峰电压被死死压制,高频毛刺快速衰减。这意味着研发在进行 EMI 摸底时,完全可以省去复杂的 Snubber(缓冲电路)调参地狱,甚至在 BOM 中直接砍掉这部分冗余器件。

破局点 3:精准死区时间 (Dead-time) 控制与轻载效率跃升

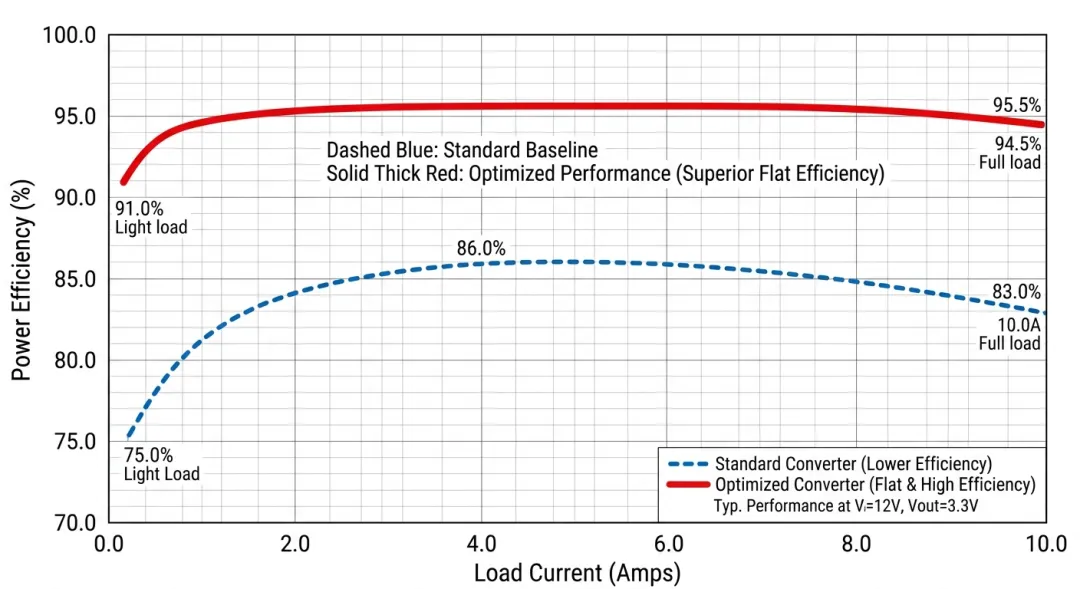

AI 服务器并非时刻都在满载跑测试,大量的待机与中低并发任务让 PDN 长期处于轻载(Light-load)区间。在轻载下,开关损耗(尤其是死区时间内的体二极管导通损耗)对总效率的拖累会呈现指数级上升。如果死区时间留得过长,体二极管(Body Diode)正向导通时间增加,发热严重;留得过短,又极易引发上下管直通(Shoot-through)炸机。

长工微的底层驱动架构内嵌了自适应的精准死区时间(Dead-time)控制逻辑。在低边管关断到高边管导通的极短窗口期内,它能精确卡在最佳死区阈值,将体二极管的续流耗散降至最低。配合极小的内部栅极电荷(Qg),该模块在 10A-20A 的轻载单相区间内,依然能维持极为陡峭且平稳的高效率曲线,大幅优化了数据中心关注的 PUE 核心指标。

破局点 4:高精度 IMON/TMON,给多相控制器装上“高精雷达”

对于动辄 10 相、20 相的并联供电阵列,均流(Current Balancing)是生死线。如果有一相电流报告不准,就会导致该相长期“超载”工作,最终引发单相热失控烧板。

长工微 90A DrMOS 内部集成了极高精度的电流监测(IMON)和温度监测(TMON)电路。相比于传统的 DCR 采样容易受电感温漂影响,其内置 IMON 能在全负载范围内提供误差极小($\pm 2\%$ 以内)的线性电流反馈。

这相当于给前端的数字多相控制器装上了“高精雷达”——控制器能够极其精准地获取每一相的真实工况,从而执行完美的动态相数管理(Phase Shedding)和极其平滑的均流控制。

工程师赋能:从 Reference Design 到 Layout 避坑指南

选对料只是第一步,好用才是硬道理。为了最大限度降低 Design-in 摩擦力,长工微提供了经过严苛验证的 N-Phase 评估板(EVB)及完整的 Layout 铺铜指南:

高频去耦策略:明确给出了 VIN与 PGND 的高频去耦电容(MLCC)“贴脸”放置方案,最小化高频回路的 ESL/ESR。

Via Array(过孔阵列)优化:针对 Top-side Cooling 架构,提供了底层控制信号走线与非承载热量的通流过孔阵列最佳实践,闭眼抄作业就能保证电气性能与热管理的双赢。

结语与开发资源获取

在 AI 算力供电这个“地狱级”副本里,长工微 90A 智能 DrMOS 凭借 Top-side Cooling 封装、极低寄生电感、精准的死区时间控制以及高精度的 IMON/TMON 遥测,帮研发工程师彻底解决了热撞墙与 EMI 调试耗时的痛点。减少一轮 Re-spin,就是帮项目早半个月推向市场(TTM),也是帮研发兄弟早点下班。

【硬核资源,即刻获取】

别再对着 DataSheet 盲猜了,直接拿实物跑波形验证!

👉 [直接扫码免费申请长工微 90A DrMOS 测试评估板 (EVB) 及 N-Phase 参考设计包]

(包含完整 Altium/Allegro 原理图、Gerber 文件、BOM 清单及 SPICE 仿真模型)

往期推荐

夜雨聆风

夜雨聆风