文档内容

栏目编辑

邹优强

从

到

一一基于

的完整低功耗设计流程

摘要

众所周知

,

目前集成电路的功耗正变得越来越高

。电路功耗密度的增长速度十分惊人

, 使

得功耗管理几乎对每一类设计都变成了一个日益严峻的问题

。从A SI C 设计的角度来看

, 面向S O C

的高效功耗管理技术从架构设计阶段就成为CI 设计的一部分

, 而低功耗实现的技术则需要应用

于从R T L 到G D sl

l 设计的每一阶段

。

本文将着重介绍基于通用功耗格式( C P F

:

C o m m o n P o w er

F o mr

at )的完整低功耗设计流程

。

在19 9

年的第32 届M CI

R O 大会上

, 英特

尔公司的F er

d P ol

lac

k 首次指出了一种相当令人

吃惊的趋势

,

那就是

,

集成电路的功耗密度正

以极快的速度增大

,

并逐渐接近地球上最热的

人造物体的功耗密度

。

对于9 0n m 及以下尺寸的电路设计来说

, 功

耗管理是十分必要的

。这是因为

,

在这一工艺

尺寸下

,

漏电流将超过开关电流的大小

,

占主

导地位

, 从而成为C M O S 电路中功耗的主要来

源

,

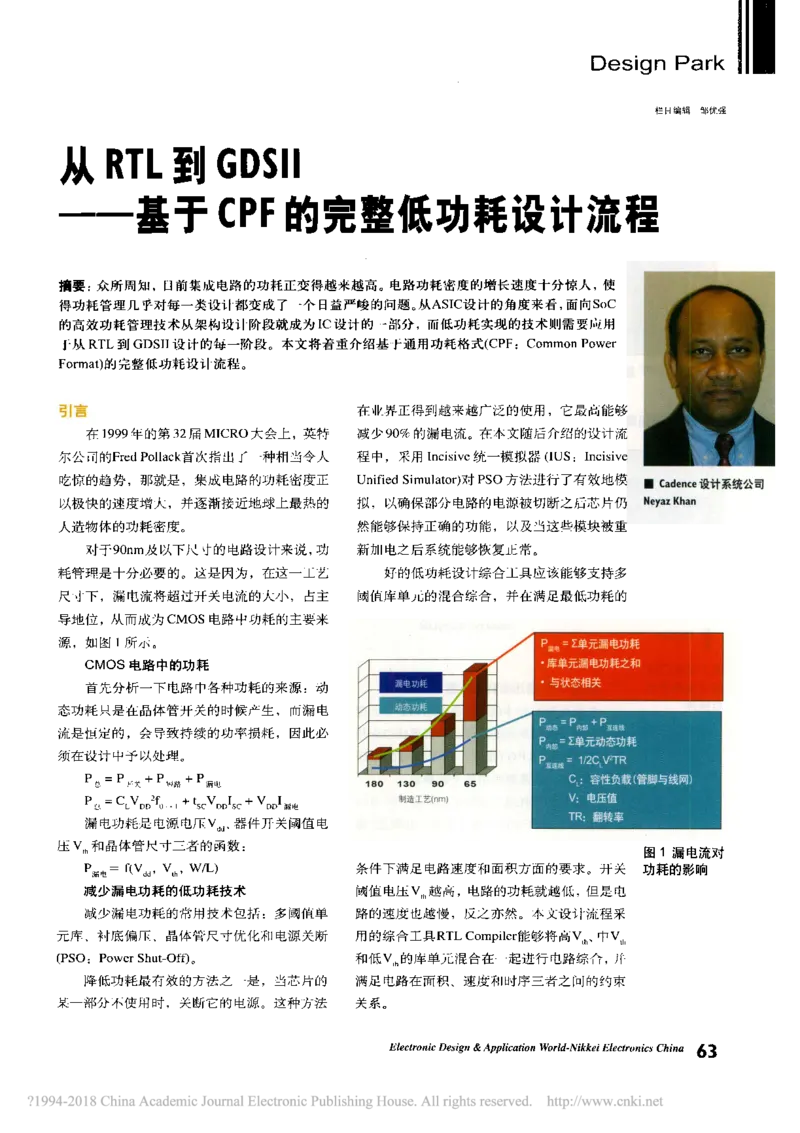

如图l 所示

。

C M O S 电路中的功耗

首先分析一下电路中各种功耗的来源

: 动

态功耗只是在晶体管开关的时候产生

,

而漏电

流是恒定的

,

会导致持续的功率损耗

,

因此必

须在设计中予以处理

。

P 。

=

P 开关+

P 毓路+

P 漏电

p

。

=

C

L V

。。2f0

_

l +

t s e V

o D I

s 。

+

V

。。I 漏电

漏电功耗是电源电压V

d d

、器件开关阑值电

压丫

、和晶体管尺寸三者的函数

:

p 漏电=

f( V

d d

,

V

。、

, W几)

减少漏电功耗的低功耗技术

减少漏电功耗的常用技术包括

:

多闭值单

元库

、

衬底偏压

、

晶体管尺寸优化和电源关断

(P S O

:

P o w e r S h u t

一O 均

。

降低功耗最有效的方法之一是

,

当芯片的

某一部分不使用时

,

关断它的电源

。

这种方法

在业界正得到越来越广泛的使用

,

它最高能够

减少90 % 的漏电流

。在本文随后介绍的设计流

程中

,

采用I n c i s i v e 统一模拟器(Iu S

:

I n e i s i v e

U n i if

e d S i m u la t o r )对P S O 方法进行了有效地模

拟

,

以确保部分电路的电源被切断之后芯片仍

然能够保持正确的功能

,

以及当这些模块被重

新加电之后系统能够恢复正常

。

好的低功耗设计综合工具应该能够支持多

闭值库单元的混合综合

,

并在满足最低功耗的

图1 漏电流对

条件下满足电路速度和面积方面的要求

。

开关

功耗的影响

阑值电压丫

h 越高

, 电路的功耗就越低

, 但是电

路的速度也越慢

,

反之亦然

。

本文设计流程采

用的综合工具R T L

C o m p i le r 能够将高V

th

、

中V

t。

和低V

:。的库单元混合在一起进行电路综合

, 并

满足电路在面积

、

速度和时序三者之间的约束

关系

。

E le

cotr

n ic

D e sign

& 沌即ilc

a 瓦o n wo 游

押认掩e i leE

cotr

n ic s hC in

a

6 3

设计新苑

图

采用

描述隔离与状

使用

描述功耗设计意图

态保持

在采用

技术时

, 还需要隔离必要的逻

辑

,

并保持关键单元的状态

,

即需要状态保持

的电源门控( S R P G ) 技术

。对于多电源电压

( M S V)

电路

,

还需要采用电平转换器

。

全芯片的功耗设计意图可以采用C P F 进行

有效地描述

。C P F 文件作为一个统一的规范

, 能

够在设计

、

验证与实现的整个设计流程中描述

各种功耗意图

。它还包含了用于电路综合与实

现的库的信息

,

以及其他特殊的工艺信息

。

设计意图

:

电源域

一逻辑上

: 层次化模块对应相应的电源域

一物理上

:

电源/ 地网络与互连

一分析模式

: 指定相应的时序库到不同的电

源域

·

电源逻辑

一电平转换逻辑

一隔离逻辑

一状态保持逻辑

一开关逻辑& 控制信号

·

电源模式

一模式与转换

工艺信息

:

· 电平转换单元

·

隔离单元

· 状态保持单元

· 开关单元

· 常用单元

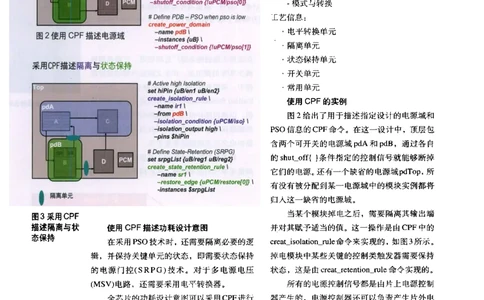

使用C 户F 的实例

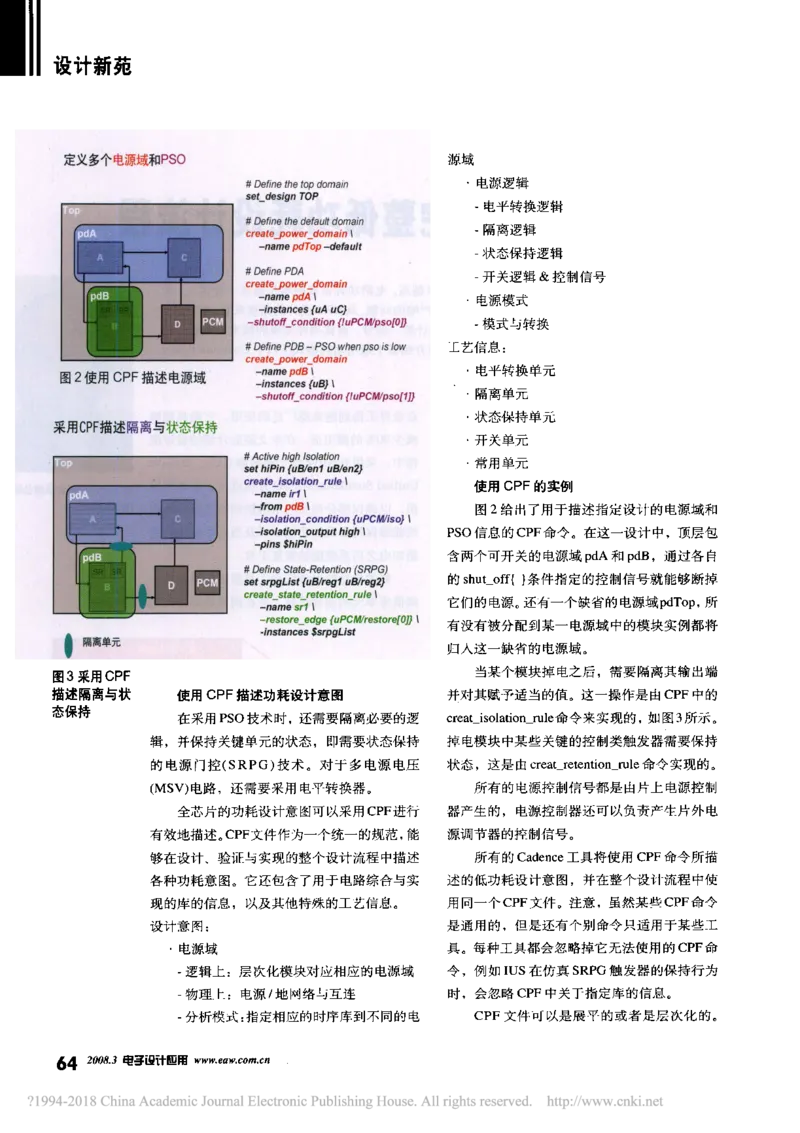

图2 给出了用于描述指定设计的电源域和

P S O 信息的C P F 命令

。在这一设计中

, 顶层包

含两个可开关的电源域dP A 和p d B

,

通过各自

的hs ut

_ o f { }条件指定的控制信号就能够断掉

它们的电源

。还有一个缺省的电源域p d T叩

, 所

有没有被分配到某一电源域中的模块实例都将

归人这一缺省的电源域

。

当某个模块掉电之后

,

需要隔离其输出端

并对其赋予适当的值

。这一操作是由C P F 中的

c er

a -t

i s o la ti o n皿

l e 命令来实现的

, 如图3 所示

。

掉电模块中某些关键的控制类触发器需要保持

状态

,

这是由er ae 仁er

t en it on

- r u l e 命令实现的

。

所有的电源控制信号都是由片上电源控制

器产生的

,

电源控制器还可以负责产生片外电

源调节器的控制信号

。

所有的C ad en e 工具将使用C P F 命令所描

述的低功耗设计意图

,

并在整个设计流程中使

用同一个C P F 文件

。

注意

,

虽然某些C P F 命令

是通用的

,

但是还有个别命令只适用于某些工

具

。

每种工具都会忽略掉它无法使用的C P F 命

令

,

例如IU S 在仿真S R P G 触发器的保持行为

时

,

会忽略C P F 中关于指定库的信息

。

C P F 文件可以是展平的或者是层次化的

。

6 4

2.08

脚W特气e 口邢气亡口爪

一C n

一

一般而言

,

在开始芯片顶层设计时

,

使用层次

化描述的C P F 文件与设计的实际结构相匹配

。

本文接下来将介绍在整个低功耗设计流程

中

, 各种工具如何使用C P F 文件描述的功耗意

图

。

采用! US

验证功耗意图

低功耗设计流程的第一步是定义并描述芯

片的功耗意图

, 创建如上文所介绍的C P F 文件

。

下一步是验证在正常功能行为之上叠加了低功

耗行为的系统的功能正确性

, 这需要使用I U S

来仿真c P F 文件所描述的电源掉电

、

隔离和状

态保持等行为

。

C P F 文件指定了触发隔离

、

电

源掉电和状态保持操作的控制信号

。

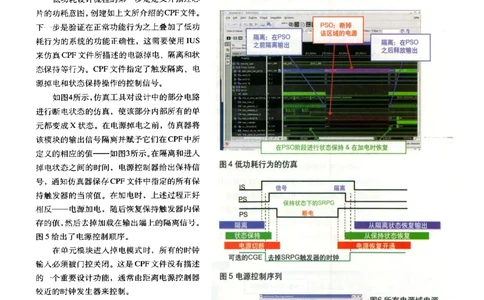

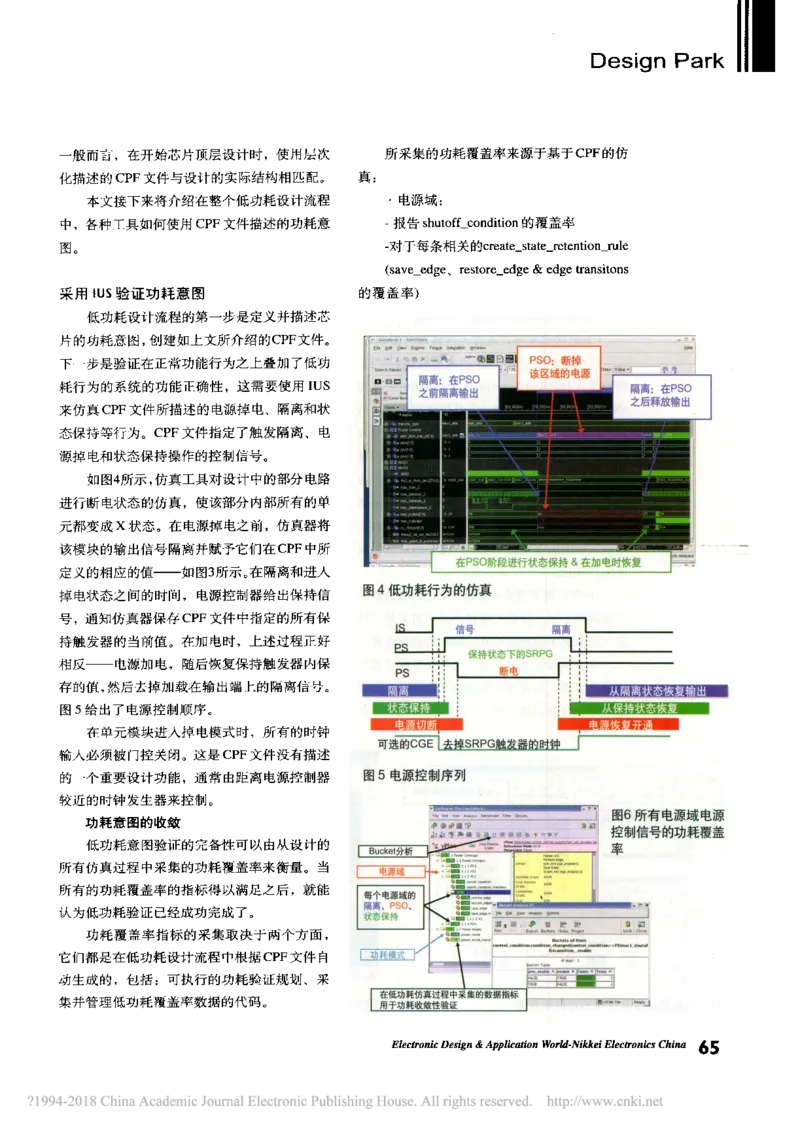

如图4所示

, 仿真工具对设计中的部分电路

进行断电状态的仿真

,

使该部分内部所有的单

元都变成X 状态

。在电源掉电之前

, 仿真器将

该模块的输出信号隔离并赋予它们在C P F 中所

定义的相应的值—

如图3 所示

。在隔离和进人

掉电状态之间的时间

,

电源控制器给出保持信

号

, 通知仿真器保存C P F 文件中指定的所有保

持触发器的当前值

。

在加电时

, 上述过程正好

相反—

电源加电

,

随后恢复保持触发器内保

存的值

, 然后去掉加载在输出端上的隔离信号

。

图5 给出了电源控制顺序

。

在单元模块进人掉电模式时

,

所有的时钟

输人必须被门控关闭

。这是C P F 文件没有描述

的一个重要设计功能

,

通常由距离电源控制器

较近的时钟发生器来控制

。

功耗意图的收敛

低功耗意图验证的完备性可以由从设计的

所有仿真过程中采集的功耗覆盖率来衡量

。当

所有的功耗覆盖率的指标得以满足之后

,

就能

认为低功耗验证已经成功完成了

。

功耗覆盖率指标的采集取决于两个方面

,

它们都是在低功耗设计流程中根据C P F 文件自

动生成的

,

包括

: 可执行的功耗验证规划

、

采

集并管理低功耗覆盖率数据的代码

。

所采集的功耗覆盖率来源于基于C P F 的仿

真

:

·

电源域

:

一报告

s h u t o fl 泣c o n d i t io n 的覆盖率

一对于每条相关的

c er

at 之

s ta te - r e t e n ti o n ,

一e

(

s a v

e _ e d g e

、

er

s to r e - e d g e &

e d g e atr

n s i t o n s

的覆盖率)

Ele

cotr

n ic

D e s ign

& 月即“ ` “ “ 口

n ” o/ r` -l M k k e i leE咖

n如hC ian

6 5

设计新苑

...

.

.

ù.....ù...ù

一

.

一对于每条相关的

r ae

c t e

一

i

s

o l

a

t

i o

“

_

l o

g

i

e _ r

u l

e

(

i

s

o l

a

t

i

n

o

_

n

c o

d

i

t

i o

n

&

e

d g

e

t

a r

n

s

i

t

n

o

s 的覆

盖率

)

· 功耗模式

一C

FP 中定义的每种功耗模式的覆盖率

一每次有效功耗模式转换的覆盖率

一可选项

:

P

o

w e r-m

o

d

e _

c

h e e k

i

ng

( 当出现无效模式或者无效转换时报错

)

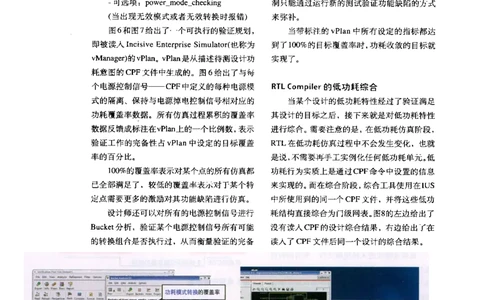

图

6

和图7 给出了一个可执行的验证规划

,

即被读人I n c i s i v e

E n t e r p r i s e

S i m u l a to

r (也称为

v M an

a g er ) 的

v p l a n

。

v p lan 是从描述待测设计功

耗意图的C P F 文件中生成的

。

图6 给出了与每

个电源控制信号—

C PF

中定义的每种电源模

式的隔离

、

保持与电源掉电控制信号相对应的

功耗覆盖率数据

。

所有仿真过程累积的覆盖率

数据反馈成标注在

v lP an 上的一个比例数

, 表示

验证工作的完备性占

v lP an

中设定的目标覆盖

率的百分比

。

10 % 的覆盖率表示对某个点的所有仿真都

已全部满足了

,

较低的覆盖率表示对于某个特

定点需要更多的激励对其功能缺陷进行仿真

。

设计师还可以对所有的电源控制信号进行

B cu ke

t 分析

,

验证某个电源控制信号所有可能

的转换组合是否执行过

,

从而衡量验证的完备

性

。

出现任何遗漏的转换就表示激励生成是不

完整的

。

图7 给出了C P F 中定义的所有指定功耗操

作模式的功耗指标

,

以及所有可能的有效模式

转换

。

设计师可以对搜集的仿真数据进行

B cu

k et 分析

,

以寻找所有遗漏的模式转换

。

遗

漏的转换表明覆盖率空间还存在漏洞

, 这些漏

洞只能通过运行新的测试验证功能缺陷的方式

来弥丰卜

。

当带标注的

v lP an

中所有设定的指标都达

到了10 0 % 的目标覆盖率时

, 功耗收敛的目标就

实现了

。

RT L c o m p i! e r 的低功耗综合

当某个设计的低功耗特性经过了验证满足

其设计的目标之后

,

接下来就是对低功耗特性

进行综合

。需要注意的是

, 在低功耗仿真阶段

,

RLT 在低功耗仿真过程中不会发生变化

,

也就

是说

, 不需要再手工实例化任何低功耗单元

。低

功耗行为实质上是通过C P F 命令中设置的信息

来实现的

。而在综合阶段

, 综合工具使用在I U S

中所使用到的同一个C P F 文件

,

并将这些低功

耗结构直接综合为门级网表

。图8 的左边给出了

没有读人C P F 的设计综合结果

,

右边给出了在

读人了C P F 文件后同一个设计的综合结果

。

图7 功耗模式及其转换的功耗覆盖率

图S R 下L C o m ilP er

的低功耗综合

6 6

2.08

J 电子设计应用

w w .w ae

.w e o m

. c n

识别出

文件中指定的低功耗特性

,

并将下列低功耗单元添加到设计当中

:

用于电

源域所有输出端的隔离单元

、

用于指定输人端

的隔离单元

、

用于跨电压域信号的电平转换器

、

将指定的所有触发器替换为可以保持状态的触

发器

。

除了电源门控之外

, R C 将在网表中插人所

有的低功耗单元

,

电源门控将在布局布线之后

再插人到网表中

。

顺便说明一下

, 在R T L 仿真中

, 不一定需

要把电源控制器与设计连在一起进行仿真

。

这

一过程是由IU S 通过提供电源控制器输出端的

电源控制信号的虚拟连接关系而得以实现的

。

而在综合阶段

,

这些虚拟的连接被替换成与相

应单元的R T L 级连接

。

R C 根据C P F 文件的描

述

,

自动连接所有的低功耗单元

, 就像IU S 仿

真那样

。

R C 能够以多种模式同时对一个设计进行综

合

。

它的时序分析引擎能够自动指出设计中的

最差路径

。

除此之外

,

R C 还支持自顶向下的

M S V 综合

, 这种综合能够在芯片的不同电压域

上采用不同的单元库

,

执行自顶向下的分析和

优化操作

。

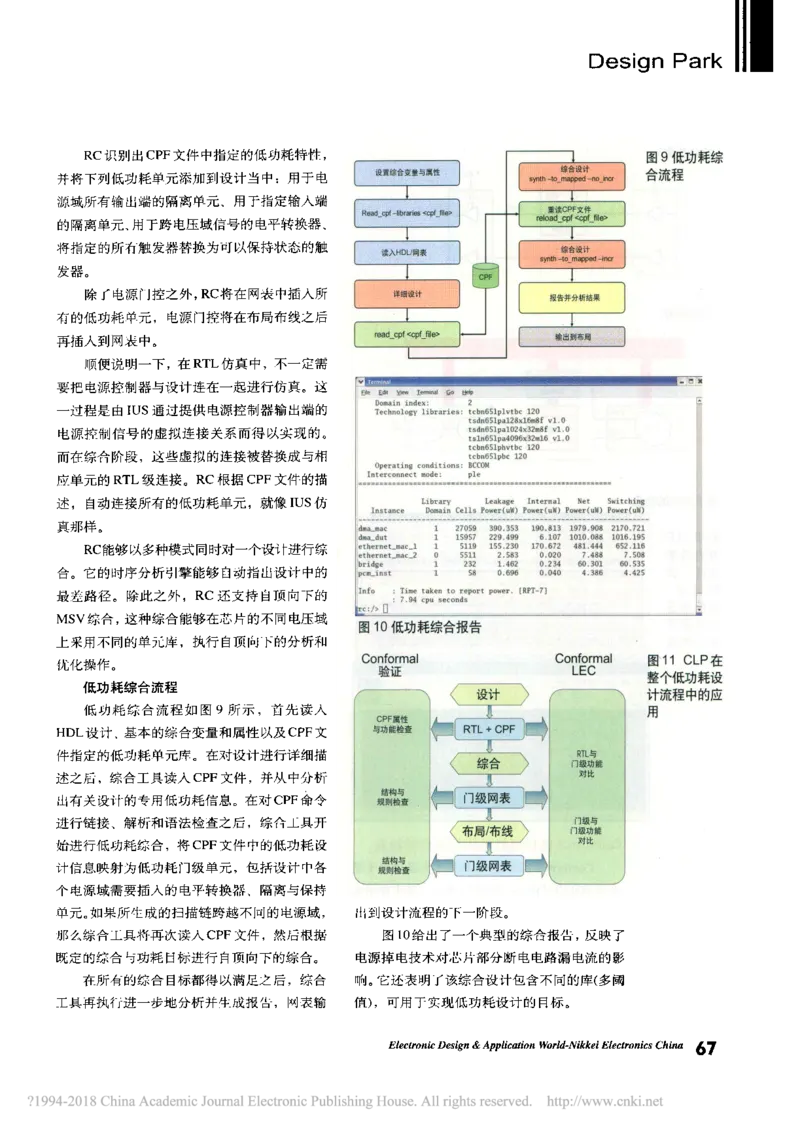

低功耗综合流程

低功耗综合流程如图9 所示

,

首先读入

H D L 设计

、

基本的综合变量和属性以及C P F 文

件指定的低功耗单元库

。

在对设计进行详细描

述之后

,

综合工具读人C P F 文件

,

并从中分析

出有关设计的专用低功耗信息

。在对C P F 命令

进行链接

、

解析和语法检查之后

,

综合工具开

始进行低功耗综合

, 将C P F 文件中的低功耗设

计信息映射为低功耗门级单元

,

包括设计中各

个电源域需要插入的电平转换器

、

隔离与保持

单元

。如果所生成的扫描链跨越不同的电源域

,

那么综合工具将再次读人C P F 文件

, 然后根据

既定的综合与功耗目标进行自顶向下的综合

。

在所有的综合目标都得以满足之后

,

综合

工具再执行进一步地分析并生成报告

,

网表输

出到设计流程的下一阶段

。

图10 给出了一个典型的综合报告

, 反映了

电源掉电技术对芯片部分断电电路漏电流的影

响

。它还表明了该综合设计包含不同的库(多闭

值)

,

可用于实现低功耗设计的目标

。

leE

c如inc

eD

s ign

& 注即“ ` 口“ 口” W

o

r ` -l 刀ik k e i leE

c otr inc

, hc ian

6 7

设计新苑

co

n

fo

r

m

l

a

低功耗的结构与等价性检查

n o

fo r

m

l

a

低功耗

技术大量应用于整

个低功耗设计流程

, 如图1 所示

。其中使用的

模型主要分为两类

:

C o n fo mr

a l 验证

. C PF 属性与功能检查—

保持功能

、隔离

功能

· 结构检查—

电源连接

、

缺失的隔离单

元

、

缺失的电平转换器

· 规则检查—

电源控制

、隔离控制

、

保持

控制

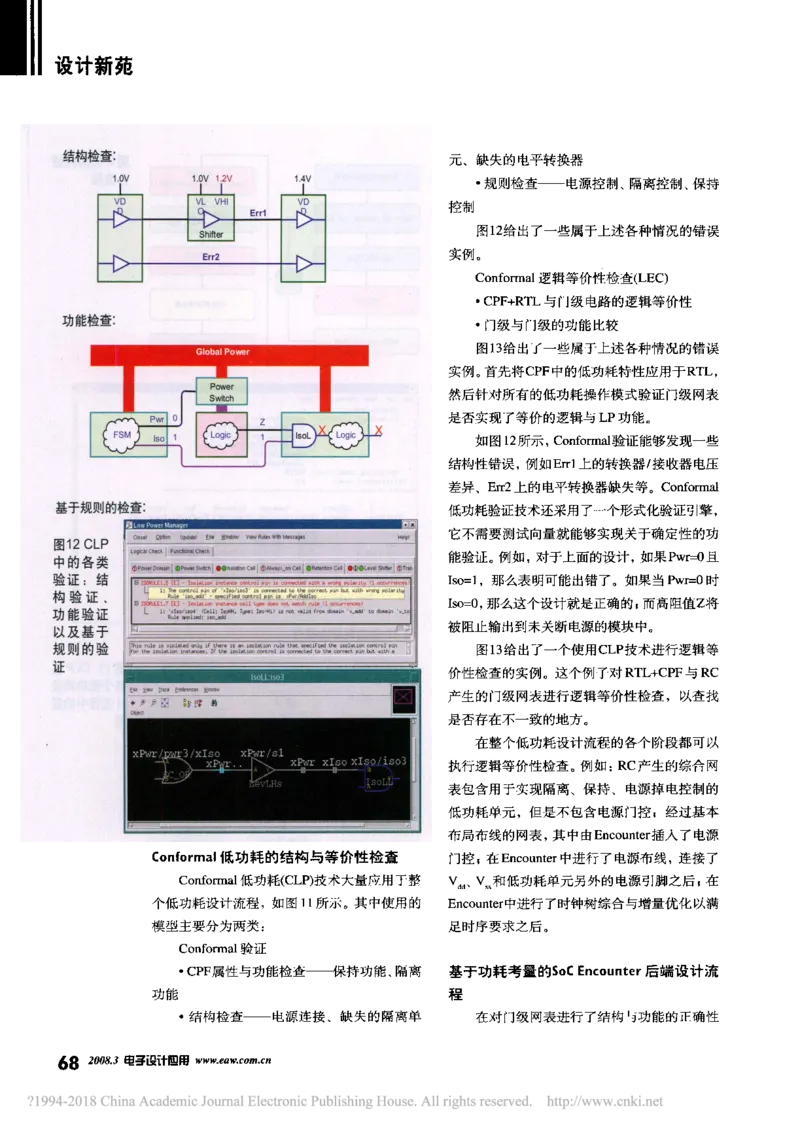

图12 给出了一些属于上述各种情况的错误

实例

。

C o n fo

r m a l 逻辑等价性检查(L E C )

, C P F + R T L 与门级电路的逻辑等价性

· 门级与门级的功能比较

图13 给出了一些属于上述各种情况的错误

实例

。首先将C P F 中的低功耗特性应用于R几

,

然后针对所有的低功耗操作模式验证门级网表

是否实现了等价的逻辑与L P 功能

。

如图12 所示

, C on fo

n 刀a l验证能够发现一些

结构性错误

, 例如E r l 上的转换器/ 接收器电压

差异

、

E r Z 上的电平转换器缺失等

。

C on fo

n n al

低功耗验证技术还采用了一个形式化验证引擎

,

它不需要测试向量就能够实现关于确定性的功

能验证

。例如

, 对于上面的设计

, 如果P w 乍0 且

15 0 = 1

,

那么表明可能出错了

。

如果当P w r = 0 时

15

0 = 0

, 那么这个设计就是正确的

; 而高阻值Z 将

被阻止输出到未关断电源的模块中

。

图13 给出了一个使用C L P 技术进行逻辑等

价性检查的实例

。

这个例子对R T L 十c PF 与R c

产生的门级网表进行逻辑等价性检查

,

以查找

是否存在不一致的地方

。

在整个低功耗设计流程的各个阶段都可以

执行逻辑等价性检查

。例如

:

R C 产生的综合网

表包含用于实现隔离

、

保持

、

电源掉电控制的

低功耗单元

,

但是不包含电源门控

; 经过基本

布局布线的网表

, 其中由E cn ou nt er 插人了电源

门控

; 在E cn ou nt er 中进行了电源布线

, 连接了

V

d d

、

vs

s 和低功耗单元另外的电源引脚之后

; 在

E cn ou nt er 中进行了时钟树综合与增量优化以满

足时序要求之后

。

基于功耗考量的S o C Ecn

o u nt

er

后端设计流

程

在对门级网表进行了结构与功能的正确性

6 8

2.08

, 电弓设计应用

` w .w ae .w

c o m

· c n

.

D

e

s ig n

P a r k

图, 3 基于C LP 的逻辑等价性检查

分析

,

并执行了功能等价性检查之后

, 就可以

开始进行后端设计流程了

,

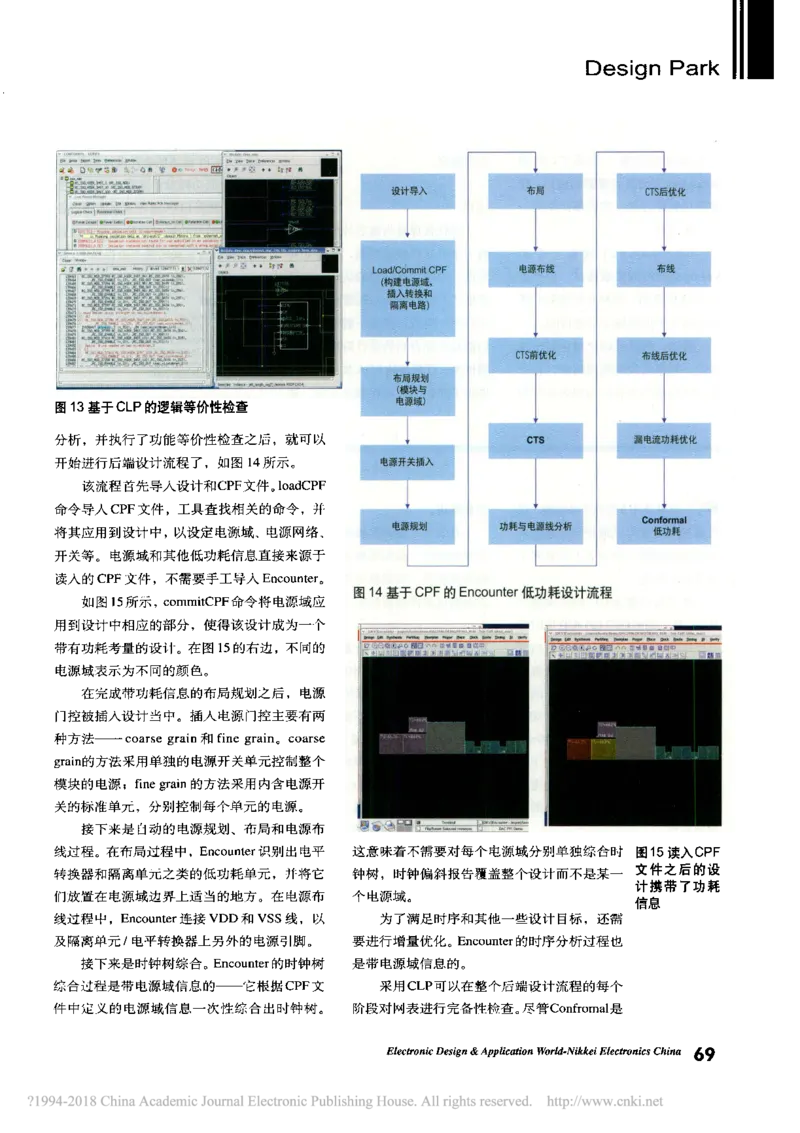

如图14 所示

。

该流程首先导人设计和c P F 文件

。lao d c P F

命令导人C P F 文件

,

工具查找相关的命令

,

并

将其应用到设计中

, 以设定电源域

、

电源网络

、

开关等

。

电源域和其他低功耗信息直接来源于

读人的C P F 文件

,

不需要手工导人E cn ou

n et

r

。

如图15 所示

,

c o m m i t C P F 命令将电源域应

用到设计中相应的部分

,

使得该设计成为一个

带有功耗考量的设计

。在图巧的右边

, 不同的

电源域表示为不同的颜色

。

在完成带功耗信息的布局规划之后

,

电源

门控被插人设计当中

。

插人电源门控主要有两

种方法—

e o a r s e

g r a i n 和f i n e

g r a i n

。

e o a r s e

g ar in 的方法采用单独的电源开关单元控制整个

模块的电源

;

if ne

gr ia

n 的方法采用内含电源开

关的标准单元

, 分别控制每个单元的电源

。

接下来是自动的电源规划

、

布局和电源布

线过程

。在布局过程中

,

E nc ou nt er 识别出电平

转换器和隔离单元之类的低功耗单元

,

并将它

们放置在电源域边界上适当的地方

。

在电源布

线过程中

,

E n e o u n et

r 连接V D D 和V S S 线

,

以

及隔离单元/ 电平转换器上另外的电源引脚

。

接下来是时钟树综合

。

E cn ou nt

er 的时钟树

综合过程是带电源域信息的—

它根据C P F 文

件中定义的电源域信息一次性综合出时钟树

。

这意味着不需要对每个电源域分别单独综合时

钟树

,

时钟偏斜报告覆盖整个设计而不是某一

个电源域

。

为了满足时序和其他一些设计目标

,

还需

要进行增量优化

。

E cn ou nt

e r 的时序分析过程也

是带电源域信息的

。

采用C L P 可以在整个后端设计流程的每个

阶段对网表进行完备性检查

。尽管C on

fr

o m al 是

图1 5 读入C p F

文件之后的设

计携带了功耗

信息

leE

` otr icn

D es ign

& 注即ical

如

“ W

o 游

刀认几ie leE

cotr

n ics

hC ian

6 ,

设计新苑

....

..........

一

.

一个独立的引擎

,

但是C L P 和

Ecn ou

n et

r 之间具有紧密的接口

, 能

够简化验证过程

。

它们都共享同一

个C P F 文件

。

E

n

c

o

u

n

t

e

:

还有一个与

v

o l t a g e s t o r m 的紧密接口

,

用于进

行IR 压降分析

, 这种分析是对C P F

指定的每个电源域分别进行的

。

最后

, 再通过C L P 对布局布线

后的

、

时序收敛的物理网表

,

和带

有C P F 信息的综合后的网表进行等

价性检查

。

结语

功耗管理是当前芯片设计面临

的一个日益严峻的问题

,

尽管业界

对这一问题已有清楚的认识

,

并且

采用了一些先进的功耗管理技术来

应对这一挑战

,

但是一般情况下人

们都是在综合后的设计阶段采用这

类技术

。

目前新的E D A 技术和工具

提供了完整的低功耗解决方案

,

通

过采用C PF 描述低功耗设计信息

, 并

在整个低功耗设计流程中使用这些

信息

, 使得E D A 业界首次实现将各

种高级的低功耗设计技术整合在设

计

、

验证与实现的整个流程当中

。.

参考文献

1

.

J a c k

H o r g a n

.

L o w

P o w e r S O C

D e s i g n

·

E D A C a fe

( 17

一2 1 M

a y 2 00 4 )

2

.

5 12 C o m m o

n P o w

e r F o mr

a t S Pe c iif

e at i o n

一V e r s i o n

1

.

0

, Zn d j a n

2 0 0 7

.

w w w

.

s iZ

,

o gr

3

.

L o w

P o w e r d e s ig n

t e c h n iq u e s

.

C a d e n e e

In t e rn

a l Per

s e n t a t i o n

2 0 0 7

4

,

R T L

C

o m P il e r

i n t e r n a l

A E

t r a i n i n g

m a t e ir a l s

.

C a d e n e e I n t e r n a l T r a i n i n g 2 0 06

一2 0 0 7

. .

. . .

. . .

. . . .

. . .

. . .

. . . 哪. .

. . .

. . . .

. . .

目. . 曰. . 口. 脚翻曰. .

圈圈口. . 圈翻. . 目圈.

.

;饵佛撰郊以料姗淑辱那黝秘肤建绷

让绪趣哪脚优或哪魏侧

皿协无需使用5 号或7 号电池

, 仅

用纽扣电池就可以维持与目前差不

多的使用时间

,

同时又大大有利于

设备的小型化

。

在没有内置M C U 的收发器产

品中

, T l 公司的C C 2 4 2O 在收发时的

消耗电流已经低于20 m A

。而在内置

了M C U 的收发器产品中

, 还没有收

发时消耗电流能够低于20 m A 的产

品

。不过

, Je n n i e 公司预计将于2 0 0 8

年推出收发时消耗电流低于2 0 m A

的JN S 14

x 系列

。O 粗公司也定下同

样的目标

,

将开发收发时消耗电流

低于ZOm A

、并具有内置M C U 的收

发器芯片

。

容易推进

。

各芯片厂商都可提供包括了协

议堆栈软件

、

收发器模块及测试板

的测试套件

。

在选择时需要充分考

虑到测试套件的使用容易度

。

可支持数据传翰的收发器

上述基于I E E E

8 0 2

. 1 5

. 4 的

2

. 4 G H z 收发器的数据传输速率较

低

, 仅有2 5 0kb ps

, 并不适合于传输

音乐

、图像等数据

。但是

, 业内也有

专为传输音乐

、

图像等应用设计的

低功耗收发器

。

J e

n in

c 公司的

J N S 13 9 只要增加专用端口就可以传

送音乐数据(见图4)

,

采用A D P c M

方式进行数据传输时

,

传输速率只

需3 2 k b p s 就已足够

。

也有公司可提供数据传输速率

较高的产品

。

韩国R a d i o P u l s e 公司

的收发器M G

一2 4 5 0 /M G

一2 4 5 5 的数

据传输速率有s o o k b p s 和I M b p s 两

档

,

用户可根据需要进行设置

。

此

图4 目标是传送音乐

提供软件与测试套件

在研究是否采用iZ g B e

时

, 构

建网络的协议堆栈软件及测试套件

的提供情况也是极为重要的选择因

素

。如果具有可使用的测试套件

, 那

么

, 从iZ g B e

的初始评估

、

引人讨

论到应用软件的开发等过程就比较

外

, 中国台湾地区达盛电子(U B E )C

的U Z 2 4 0 0 的传输速率也可以设定

为625 kb sP

, 飞思卡尔半导体公司的

M C 1 32 2 x 系列器件的传输速率更高

达ZM b sP

。

虽然提高数据传输速率

后

,

产品就无法支持IE E E 8 02

. 1 5

. 4

或iZ g B e

,

也就难以与其他公司的

芯片相互连接

,

但还是可以说是同

时实现了高速传输与低功耗

。

爬

[N IK K E I E L E C T R O N IC S

0

2 0 0 8

.

N i k k e i B u s in e s s P u b l ic a t i o n s

, I n e

. A ll

r i 只h t s

r e s e r v e d

. ] ( 南庭译)

7 0

20 .8 3 电子设计应用

w w .w

e a .w

c o m

· c n