文档内容

第一章 数字电路基础

1.1 数字电路的基本概念

1.2 数制

1.3 二—十进制码

1.4 数字电路中的二极管与三极管

1.5 基本逻辑运算

1.6 逻辑函数及其表示方法1.1 数字电路的基本概念

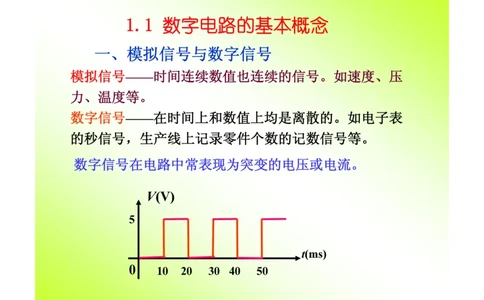

一、模拟信号与数字信号

模拟信号——时间连续数值也连续的信号。如速度、压

力、温度等。

数字信号——在时间上和数值上均是离散的。如电子表

的秒信号,生产线上记录零件个数的记数信号等。

数字信号在电路中常表现为突变的电压或电流。

V(V)

5

t(ms)

0

10 20 30 40 50二、正逻辑与负逻辑

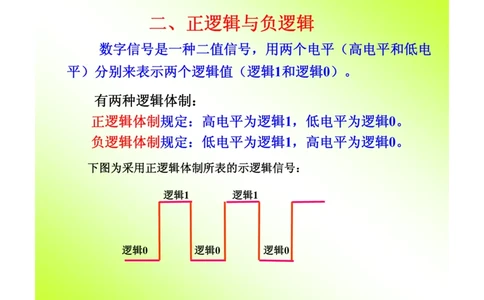

数字信号是一种二值信号,用两个电平(高电平和低电

平)分别来表示两个逻辑值(逻辑1和逻辑0)。

有两种逻辑体制:

正逻辑体制规定:高电平为逻辑1,低电平为逻辑0。

负逻辑体制规定:低电平为逻辑1,高电平为逻辑0。

下图为采用正逻辑体制所表的示逻辑信号:

逻辑1 逻辑1

逻辑0 逻辑0 逻辑0三、数字信号的主要参数

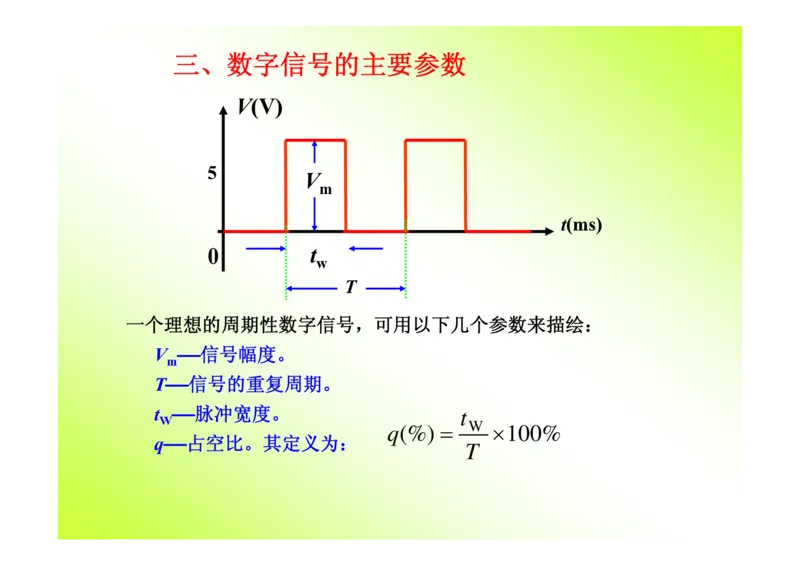

V(V)

5

V

m

t(ms)

0 t

w

T

一个理想的周期性数字信号,可用以下几个参数来描绘:

V —— 信号幅度。

m

T—— 信号的重复周期。

t —— 脉冲宽度。 t

W

W

q(%) = ×100%

q—— 占空比。其定义为:

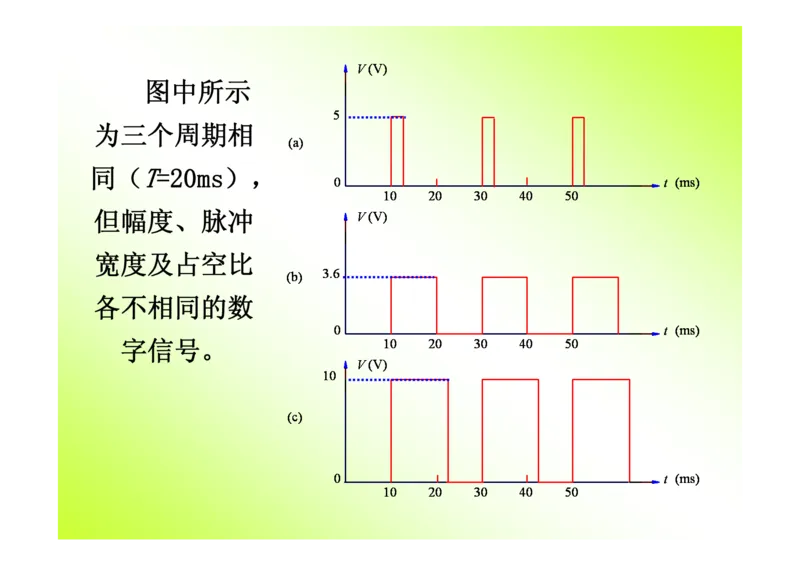

T图中所示

为三个周期相

同(T=20ms),

但幅度、脉冲

宽度及占空比

各不相同的数

字信号。1.2 数 制

一、几种常用的计数体制

1.十进制(Decimal)

2.二进制(Binary)

3.十六进制(Hexadecimal)与八进制(Octal)

二、不同数制之间的相互转换

1.二进制转换成十进制

例1.2.1 将二进制数10011.101转换成十进制数。

解:将每一位二进制数乘以位权,然后相加,可得

(10011.101) =1×24+0×23+0×22+1×21+1×20+1×2-1+

B

0×2-2+1×2-3

=(19.625)

D2.十进制转换成二进制

例1.2.2 将十进制数23转换成二进制数。

解: 用“除2取余”法转换:

2 23 ………余1 b

0

2 11 ………余1 b

1 读

取

2 5 ………余1 b

2

次

2 2 ………余0 b

3

序

2 1 ………余1 b

4

0

则(23) =(10111)

D B1.3 二—十进制码( BCD码)

BCD码 用二进制代码来表示十进制的0~9

——

十个数。

要用二进制代码来表示十进制的0~9十个数,至少要用

4位二进制数。

4位二进制数有16种组合,可从这16种组合中选择10种

组合分别来表示十进制的0~9十个数。

选哪10种组合,有多种方案,这就形成了不同的BCD码。常用BCD码

十进制数 8421码 2421码 5421码 余3码

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1

1 0 0 0 1 0 0 0 1 0 0 0 1 0 1 0 0

2 0 0 1 0 0 0 1 0 0 0 1 0 0 1 0 1

3 0 0 1 1 0 0 1 1 0 0 1 1 0 1 1 0

4 0 1 0 0 0 1 0 0 0 1 0 0 0 1 1 1

5 0 1 0 1 1 0 1 1 1 0 0 0 1 0 0 0

6 0 1 1 0 1 1 0 0 1 0 0 1 1 0 0 1

7 0 1 1 1 1 1 0 1 1 0 1 0 1 0 1 0

8 1 0 0 0 1 1 1 0 1 0 1 1 1 0 1 1

9 1 0 0 1 1 1 1 1 11 0 0 11 0 0

位权 8 4 2 1 2 4 2 1 5 4 2 1 无权1.4 数字电路中的二极管与三极管

一、二极管的开关特性

1.二极管的静态特性

(1)加正向电压V时,二极管导通,管压降V可忽略。二极

F D

管相当于一个闭合的开关。(2)加反向电压V时,二极管截止,反向电流I可忽略。二

R S

极管相当于一个断开的开关。

可见,二极管在电路中表现为一个受外加电压v 控制的开关。

i

当外加电压v 为一脉冲信号时,二极管将随着脉冲电压的

i

变化在“开”态与“关”态之间转换。这个转换过程就

是二极管开关的动态特性。2.二极管开关的动态特性

给二极管电路加入

一个方波信号,电流的

波形怎样呢?

t 为存储时间,t 称为渡越时间。

s t

t =t 十t 称为反向恢复时间

re s t反向恢复时间:t =t十t

re s t

产生反向恢复过程的原因:

反向恢复时间t 就是存储电荷消散所需要的时间。

re

同理,二极管从截止转为正向导通也需要时间,这段时

间称为开通时间。开通时间比反向恢复时间要小得多,一般

可以忽略不计。二、三极管的开关特性

1.三极管的三种工作状态

(1)截止状态:

当V小于三极管发射结死区电压时,I=I ≈0,

I B CBO

I=I ≈0,V ≈V ,三极管工作在截止区,对应图中的A点。

C CEO CE CC

三极管工作在截止状态的条件为:发射结反偏或小于死区电压(2)放大状态:

当V为正值且大于死区电压时,三极管导通。有

I

V −V V

I = I BE ≈ I

B

R R

b b

此时,若调节R↓,则I↑,I↑,V ↓,工作点沿着负载线由A点

b B C CE

→B点→C点→D点向上移动。在此期间,三极管工作在放大区,

其特点为I=βI。

C B

发射结正偏,集电结反偏

三极管工作在放大状态的条件为:(3)饱和状态:

V不变,继续减小R,当V =0.7V时,集电结变为

I b CE

零偏,称为临界饱和状态,对应E点。此时的集电极电流用I 表示,基极

CS

电流用I 表示,有:

I V

BS V - 0.7V V

I = CC ≈ CC I = CS = CC

BS

CS β βR

R R

C

C C

再减小R,I会继续增加,但I不会再增加,三极管进入饱和状态。

b B C

V ≈0.3V

饱和时的V 电压称为饱和压降V ,其典型值为: 。

CE CES CES

I> I

三极管工作在饱和状态的电流条件为:

B BS

电压条件为:集电结和发射结均正偏三种工作状态比较

工作状态 截 止 放 大 饱 和

条 件 I ≈ 0 0<I <I I >I

B B BS B BS

偏值情况 发射结电压< 发射结正偏 发射结正偏

死区电压

集电结反偏 集电结正偏

工

集电极电

I ≈ 0 I ≈ βI I = I = V / R

流 C C B C CS CC C

V ≈ V V = V − I R V = V = 0.3V

作 管压降

CE CC CE CC C C CE CES

近似的等

特

效电路

点

C、E间等

很大 很小

可变

效电阻

相当开关断开 相当开关闭合例1.4.1 电路及参数如图所示,设输入电压V =3V,三极管的V =0.7V。

I BE

(1)若β=60,试判断三极管是否饱和,并求出I 和V 的值。

C O

解: 根据饱和条件I >I 解题。

B BS

3-0.7

I = ≈ 0.023(mA)

B

100

V 12

I = CC = ≈ 0.020(mA)

BS

βR 60×10

C

(cid:1526)I >I (cid:1525)三极管饱和。

B BS

V 12

I = I = CC = ≈1.2(mA)

C CS

R 10

C

V = V ≈ 0.3V

O CES

(2)将R 改为6.8kΩ,重复以上计算。

C

V 12

I = CC = ≈ 0.029(mA)

I 不变,仍为0.023mA BS

βR 60×6.8

B

C

I = β× I = 60×0.023≈1.4(mA)

(cid:1526)I <I (cid:1525)三极管处在放大状态。

C B

B BS

V = V = V - I × R = 12 -1.4× 6.8 ≈ 2.48(V)

O CE CC C C(3)将R 改为6.8kΩ,再将R 改为60kΩ,重复以上计算。

C b

3-0.7

I = ≈ 0.038(mA) I ≈0.029 mA

B BS

60

(cid:1526)I >I (cid:1525)三极管饱和。

B BS

V 12

I = I = CC = ≈1.76(mA)

C CS

R 6.8

C

V = V ≈ 0.3V

O CES

由此可见,R 、R 、β等参数都

b C

能决定三极管是否饱和。

V V

饱和条件可写为: I > CC

R βR

b C

即在V 一定(要保证发射结正偏)和V 一定的条件下,R 越小,β

I CC b

越大,R 越大,三极管越容易饱和。在数字电路中总是合理地选择这

C

几个参数,使三极管在导通时为饱和导通。2.三极管的动态特性

(1)延迟时间t ——从v 正跳变

d i

的瞬间开始,到i 上升到

C

0.1I 所需的时间

CS

(2)上升时间t ——i 从0.1I

r C CS

上升到0.9I 所需的时间。

CS

(3)存储时间t ——从v 下跳变

s i

的瞬间开始,到i 下降到

C

0.9I 所需的时间。

CS

(4)下降时间t —— 从0.9I

f C CS

下降到0.1I 所需的时间。

CS

开通时间t = t +t

on d r

关断时间t = t +t

off s f1.5 基本逻辑运算

一、基本逻辑运算

1.与运算

设:开关闭合= 1

“ ”

与逻辑真值表

开关不闭合= 0

“ ”

输 入 输出

AB 灯L

灯亮,L=1

A B L

不闭合 不闭合 不亮

灯不亮,L=0

0 0 0

不闭合 闭合 不亮

0 1 0

1 0 0

与逻辑表达式: 闭合 不闭合 不亮

1 1 1

闭合 闭合 亮

L = A ⋅ B

与逻辑 只有当决定一件事情的条件全部具备之后,这

——

件事情才会发生。2.或运算

AB 灯L

不闭合 不闭合 不亮

不闭合 闭合 亮

闭合 不闭合 亮

闭合 闭合 亮

或逻辑真值表

输 入 输出

A B L

0 0 0

或逻辑表达式:

0 1 1

1 0 1

L=A+B

1 1 1

或逻辑 当决定一件事情的几个条件中,只要有一个

——

或一个以上条件具备,这件事情就发生。3.非运算

A 灯L

闭合 不亮

不闭合 亮

非逻辑真值表

A L

0 1

非逻辑表达式:

1 0

非逻辑 某事情发生与否,仅取决于一个条件,而

——

且是对该条件的否定。即条件具备时事情不发生;条

件不具备时事情才发生。二、其他常用逻辑运算

“与非”真值

1.与非

——

表

输 入 输出

由与运算 和

A B L

非运算组合而

0 0 1

成。 0 1 1

1 0 1

1 1 0

“或非”真值

表

2.或非

——

输 入 输出

由或运算和

A B L

非运算组合 0 0 1

0 1 0

而成。

1 0 0

1 1 03.异或

异或是一种二变量逻辑运算,当两个变量取值相同时,

逻辑函数值为0;当两个变量取值不同时,逻辑函数值为1。

异或的逻辑表达式为: L = A ⊕ B

“异或”真值

表

输 入 输出

A B L

0 0 0

0 1 1

1 0 1

1 1 01.6 逻辑函数及其表示方法

一、逻辑函数的建立

例1.6.1 三个人表决一件事情,结果按“少数服从多数”的原则决

定,试建立该逻辑函数。

三人表决电路真值表

解:第一步:设置自变量和因变量。

A B C L

第二步:状态赋值。

对于自变量A、B、C设: 0 0 0 0

0 0 1 0

同意为逻辑“1”,

0 1 0 0

不同意为逻辑“0”。

0 1 1 1

对于因变量L设:

1 0 0 0

事情通过为逻辑“1”,

1 0 1 1

没通过为逻辑“0”。

1 1 0 1

第三步:根据题义及上述规定 1 1 1 1

列出函数的真值表。一般地说,若输入逻辑变量A、B、C…

的取值确定以后,输出逻辑变量L的值也唯

一地确定了,就称L是A、B、C的逻辑函数,

写作:

L=f(A,B,C…)

逻辑函数与普通代数中的函数相比较,有两

个突出的特点:

(1)逻辑变量和逻辑函数只能取两个值0和1。

( 2 ) 函 数 和 变 量 之 间 的 关 系 是 由 “ 与 ” 、

“或”、“非”三种基本运算决定的。二、逻辑函数的表示方法

三人表决电路真值表

A1. B真 C值表 ——L将输入逻辑变量的各种可能取值和相应的函数值排列

在一起而组成的表格。

0 0 0 0

02 . 0 函 1数表达0 式 —— 由逻辑变量和“与”、“或”、“非”三种运算

符0所 1构 0成的表0达式。

0 1 1 1

由真值表可以转换为函数表达式。例如,由“三人表决”函数的真

1 0 0 0

值表可写出逻辑表达式:

1 0 1 1

L = ABC + ABC + ABC + ABC

1 1 0 1

1 1 1 1 真值表

反之,由函数表达式也可以转换成真值表。

A B L

例1.6.2 列出下列函数的真值表:

0 0 1

0 1 0

解:该函数有两个变量,有4种取值的

1 0 0

可能组合,将他们按顺序排列起来即

1 1 1

得真值表。3.逻辑图 由逻辑符号及它们之间的连线而构成的图形。

——

由函数表达式可以画出逻辑图。

例1.6.3 画出函数 的逻辑图:

解:可用两个非门、两个与门

和一个或门组成。

由逻辑图也可以写出表达式。

例1.6.4 写出如图所示

逻辑图的函数表达式。

解: L = AB + BC + AC本章小结

1.数字信号在时间上和数值上均是离散的。

2.数字电路中用高电平和低电平分别来表示逻辑1和逻辑0,它和二进

制数中的0和1正好对应。因此,数字系统中常用二进制数来表示数据。

3.常用BCD码有8421码、242l码、542l码、余3码等,其中842l码使用

最广泛。

4.在数字电路中,半导体二极管、三极管一般都工作在开关状态,即

工作于导通(饱和)和截止两个对立的状态,来表示逻辑1和逻辑0。

影响它们开关特性的主要因素是管子内部电荷存储和消散的时间。

5.逻辑运算中的三种基本运算是与、或、非运算。

6.描述逻辑关系的函数称为逻辑函。逻辑函数中的变量和函数值都只

能取0或1两个值。

7.常用的逻辑函数表示方法有真值表、函数表达式 、逻辑图等,它们

之间可以任意地相互转换。第二章 逻辑门电路

2.1 基本逻辑门电路

2.2 TTL逻辑门电路

2.3 MOS逻辑门电路

2.4 集成逻辑门电路的应用

2.5 正负逻辑及逻辑符号的变换2.1 基本逻辑门电路

一、二极管与门和或门电路

输 入 输出

1.与门电路 V (V) V (V) V(V)

A B L

0V 0V 0V

0V 5V 0V

5V 0V 0V

5V 5V 5V

与逻辑真值表

输 入 输出

A B L

0 0 0

0 1 0

1 0 0

1 1 12.或门电路

输 入 输出

V (V) V (V) V(V)

A B L

0V 0V 0V

0V 5V 5V

5V 0V 5V

5V 5V 5V

或逻辑真值表

输 入 输出

A B L

0 0 0

0 1 1

1 0 1

1 1 1二、三极管非门电路

非逻辑真值表

输 入 输 出

输 入 输 出

V (V) V(V)

A L

A L

0V 5V

0 1

5V 0V 1 0二极管与门和或门电路的缺点:

(1)在多个门串接使用时,会出现低电平偏离标准数值

的情况。

(2)负载能力差。解决办法:

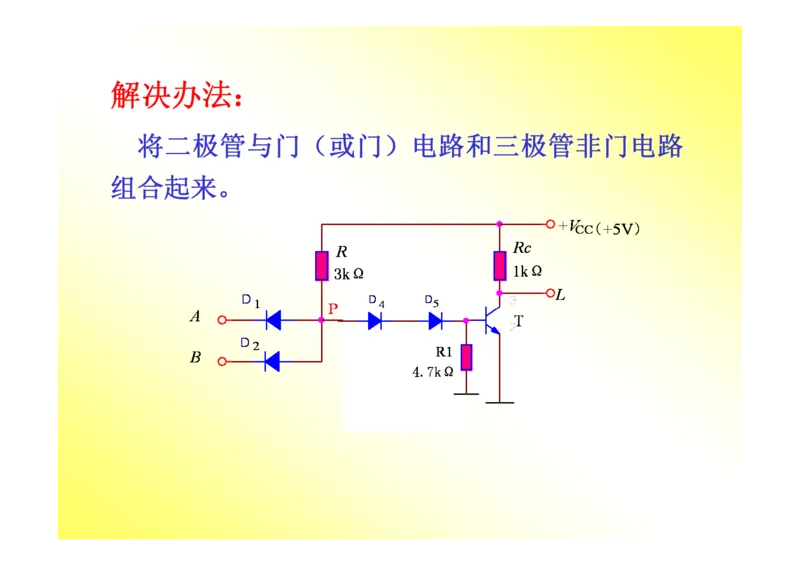

将二极管与门(或门)电路和三极管非门电路

组合起来。三、DTL与非门电路

工作原理:

(1)当A、B、C全接为高电平5V时,二极管D ~D 都截止,而D 、

1 3 4

D 和T导通,且T为饱和导通, V =0.3V,即输出低电平。

5 L

(2)A、B、C中只要有一个为低电平0.3V时,则V ≈1V,从而使D 、

P 4

D 和T都截止,V =V =5V,即输出高电平。

5 L CC

L = A ⋅ B ⋅ C

所以该电路满足与非逻辑关系,即:2.2 TTL逻辑门电路

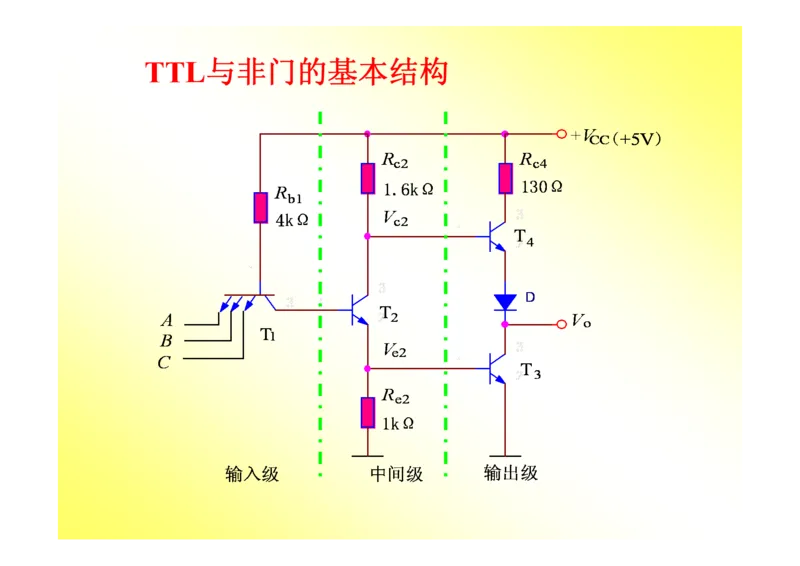

一、TTL与非门的基本结构及工作原理

1.TTL与非门的基本结构TTL与非门的基本结构2.TTL与非门的逻辑关系

(1)输入全为高电平3.6V时。

由于T 饱和导通,输出电压为:

T 、T 饱和导通, 3

2 3

V =V ≈0.3V

由于T 饱和导通,V =1V。 O CES3

2 C2

T 和二极管D都截止。

4

实现了与非门的逻

辑功能之一:

输入全为高电平时,

输出为低电平。(2)输入有低电平0.3V 时。

由于T 和D导通,所以:

4

该发射结导通,V =1V。T 、T 都截止。

B1 2 3 V ≈V -V -V

O CC BE4 D

忽略流过R 的电流,V ≈V =5V 。 =5-0.7-0.7=3.6(V)

C2 B4 CC

实现了与非门的逻辑

功能的另一方面:

输入有低电平时,

输出为高电平。

综合上述两种情况,

该电路满足与非的

逻辑功能,即:

L = A⋅ B ⋅C二、TTL与非门的开关速度

1.TTL与非门提高工作速度的原理

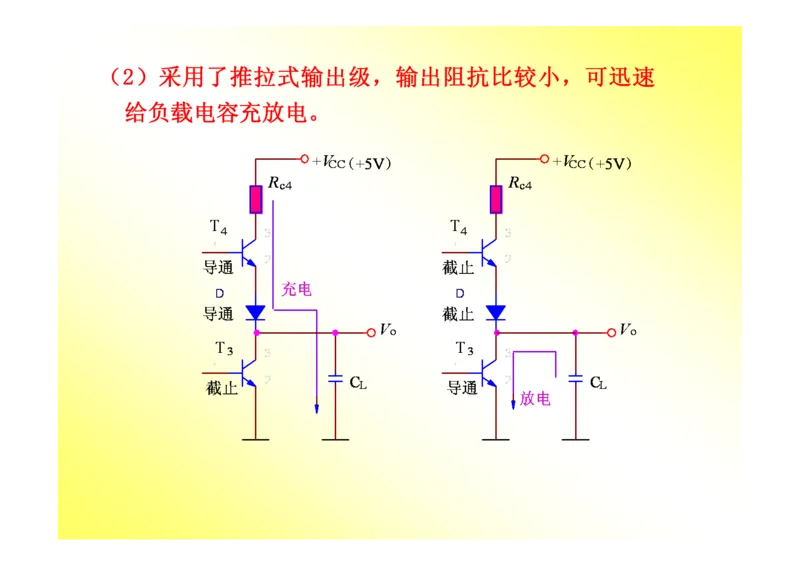

(1)采用多发射极三极管加快了存储电荷的消散过程。(2)采用了推拉式输出级,输出阻抗比较小,可迅速

给负载电容充放电。2.TTL与非门传输延迟时间t

pd

导通延迟时间t

——

从输入波形上升沿的中点到输出波形下降沿的

PHL

中点所经历的时间。

截止延迟时间t

——

从输入波形下降沿的中点到输出波形上升沿的

PLH

中点所经历的时间。

t + t

t = PLH PHL

与非门的传输延迟时间t :

pd

pd 2

一般TTL与非门传输延迟时间t 的值为几纳秒~十几个纳秒。

pd三、TTL与非门的电压传输特性及抗干扰能力

1.电压传输特性曲线:

V =f(V )

o i

A B

C

D E2.几个重要参数

(1)输出高电平电压V 在正逻辑体制中代表逻辑“1 的输

—— ”

OH

出电压。V 的理论值为3.6V,产品规定输出高电压的最小

OH

值V =2.4V。

OH(min)

(2)输出低电平电压V 在正逻辑体制中代表逻辑“0 的输

—— ”

OL

出电压。V 的理论值为0.3V,产品规定输出低电压的最大

OL

值V =0.4V。

OL(max)

(3)关门电平电压V

——

是指输出电压下降到V 时对

OFF OH(min)

应的输入电压。即输入低电压的最大值。在产品手册中常

称为输入低电平电压,用V 表示。产品规定V

IL(max) IL(max)

=0.8V。(4)开门电平电压V

——

是指输出电压下降到V 时对

ON OL(max)

应的输入电压。即输入高电压的最小值。在产品手册中常

称为输入高电平电压,用V 表示。产品规定V

IH(min) IH(min)

=2V。

(5)阈值电压V 电压传输特性的过渡区所对应的输入电压,

——

th

即决定电路截止和导通的分界线,也是决定输出高、低电

压的分界线。

近似地:V ≈V ≈V

th OFF ON

即V <V ,与非门关门,输出高电平;

i th

V >V ,与非门开门,输出低电平。

i th

V 又常被形象化地称为门槛电压。V 的值为1.3V~1.4V。

th th3.抗干扰能力

TTL门电路的输出高低电平不是一个值,而是一个范围。

同样,它的输入高低电平也有一个范围,即它的输入信号允许一定

的容差,称为噪声容限。

低电平噪声容限 V =V -V =0.8V-0.4V=0.4V

NL OFF OL(max)

高电平噪声容限 V =V -V =2.4V-2.0V=0.4V

NH OH(min) ON四、TTL与非门的带负载能力

1.输入低电平电流I 与输入高电平电流I

IL IH

(1)输入低电平电流I ——是指当门电路的输入端接低电平时,从

IL

门电路输入端流出的电流。

V −V 5 − 1

可以算出: I = CC B1 = = 1(mA)

IL

R 4

b1

产品规定I <1.6mA。

IL(2)输入高电平电流I 是指当门电路的输入端接高电

IH——

平时,流入输入端的电流。

有两种情况:

①寄生三极管效应:

I =βI ,

IH P B1

β为寄生三极管的电流放大系数。

P

②倒置的放大状态:

I =β I ,

IH i B1

β 为倒置放大的电流放大系数。

i

由于β 和β的值都远小于1,

p i

所以I 的数值比较小,产品规定:I <40uA。

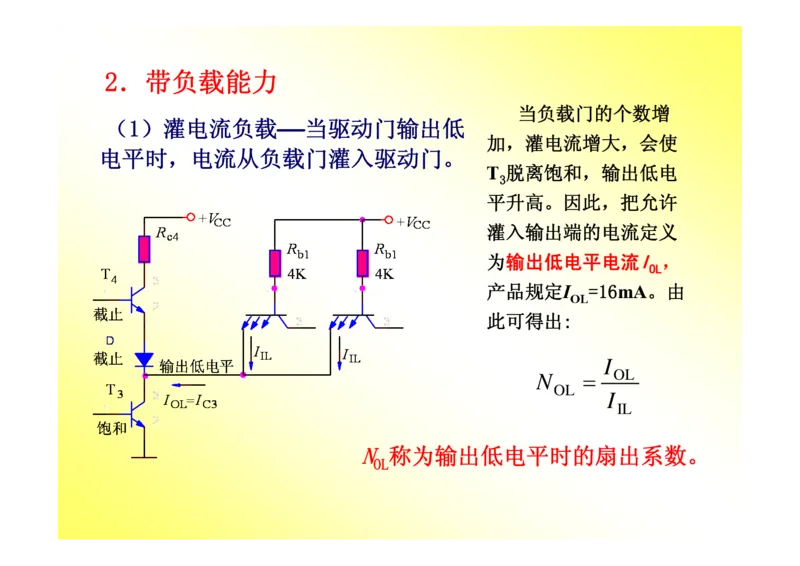

IH IH2.带负载能力

当负载门的个数增

(1)灌电流负载 当驱动门输出低

——

加,灌电流增大,会使

电平时,电流从负载门灌入驱动门。

T 脱离饱和,输出低电

3

平升高。因此,把允许

灌入输出端的电流定义

为输出低电平电流I ,

OL

产品规定I =16mA。由

OL

此可得出:

I

OL

N =

OL

I

IL

N 称为输出低电平时的扇出系数。

OL(2)拉电流负载 当驱动门输

——

出高电平时,电流从驱动门拉出,

拉电流增大时,R

C4

流至负载门的输入端。 上的压降增大,会使输

出高电平降低。因此,

把允许拉出输出端的电

流定义为输出高电平电

流I 。

OH

产品规定:I =0.4mA。

OH

由此可得出:

I

N = OH

OH

I

IH

N 称为输出高电平时的扇出系数。

OH

一般N ≠N ,常取两者中的较小值作为门电路的

OL OH

扇出系数,用N 表示。

O五、TTL与非门举例

——

7400

7400是一种典型的TTL与非门器件,内部含有4个2输入端

与非门,共有14个引脚。引脚排列图如图所示。六、 TTL门电路的其他类型

1.非门2.或非门3.与或非门4.集电极开路门( OC门)

在工程实践中,有时需要将几个门的输出端并联使用,以实现与

逻辑,称为线与。普通的TTL门电路不能进行线与。

为此,专门生产了一种可以进行线与的门电路——集电极开路门。OC门主要有以下几方面的应用:

(1)实现线与。

逻辑关系为:

L = L ⋅ L = AB ⋅ CD

1 2

(2)实现电平转换。

如图示,可使输出高电平变为10V。

(3)用做驱动器。

如图是用来驱动发光二极管的电路。OC门进行线与时,外接上拉电阻R 的选择:

P

(1)当输出高电平时,

R 不能太大。R 为最大值时要保证输出电压为V 。

P P OH(min)

由: V -V = m ' I R

CC OH(min) IH P(max)

得:

V -V

CC OH(min)

R =

P(max) '

m ⋅ I

IH(2)当输出低电平时

R 不能太小。R 为最小值时要保证输出电压为V 。

P P OL(max)

V −V

由: I = CC OL(max) + m⋅ I

OL(max) IL

R

P(min)

V −V

得:R

=

CC OL(max)

P(min)

I − m ⋅ I

OL(max) IL

所以:

R <R <R

P(min) P P(max)5.三态门

(1)三态输出门的结构及工作原理。

当EN=0时,G输出为1,D 截止,相当于一个正常的二输入端与非门,

1

称为正常工作状态。

当EN=1时,G输出为0,T 、T 都截止。这时从输出端L看进去,呈现

4 3

高阻,称为高阻态,或禁止态。

去掉非门G,则EN=1时,为工

作状态, EN=0时,为高阻态。(2)三态门的应用

三态门在计算机总线结构中有着广泛的应用。

(a)组成单向总线

——

实现信号的分时单向传送。

(b)组成双向总线,

实现信号的分时双向传送。七、TTL集成逻辑门电路系列简介

1.74系列

——

为TTL集成电路的早期产品,属中速TTL器件。

2.74L系列

——

为低功耗TTL系列,又称LTTL系列。

3.74H系列

——

为高速TTL系列。

4.74S系列

——

为肖特基TTL系列,进一步提高了速度。

74S系列的几点改进:

(1)采用了抗饱和三极管74S系列的几点改进:

(1)采用了抗饱和三极管

(2)将Re2用“有源泄放电路代替”。

(3)输出级采用了达林顿结构。

(4)输入端加了三个保护二极管。

5.74LS系列

——

为低功耗肖

特基系列。

6.74AS系列

——

为先进肖特

基系列,

7.74ALS系列

——

为先进低

功耗肖特基系列。2.3 MOS逻辑门电路

一、 NMOS门电路

1.NMOS非门

逻辑关系:(设两管的开启电压为V =V =4V,且g >>g )

T1 T2 m1 m2

(1)当输入V为高电平8V时,T 导通,T 也导通。因为g >>g ,

i 1 2 m1 m2

所以两管的导通电阻R <<R ,输出电压为:

DS1 DS2

R

V = DS1 V ≤1V 所以输出为低电平。

OL DD

R + R

DS1 DS2(2)当输入V 为低电平0V时,

i

T 截止,T 导通。

1 2

V =V -V =8V =V ,即输出为高电平。

O DD T OH

所以电路实现了非逻辑。

2.NMOS门电路

(1)与非门

与非真值表

输 入 输出

A B L

0 0 1

0 1 1

1 0 1

1 1 0(2)或非门

或非真值表

输 入 输出

A B L

0 0 1

0 1 0

1 0 0

1 1 0二、CMOS非门

CMOS逻辑门电路是由N沟道MOSFET和P沟道MOSFET互

补而成。

1.逻辑关系:

(设V >(V +|V |),且V =|V |)

DD TN TP TN TP

(1)当V=0V时,T 截止,T 导通。输出V ≈V 。

i N P O DD

(2)当V=V 时,T 导通,T 截止,输出V ≈0V。

i DD N P O2.电压传输特性:

(设: V =10V, V =|V |=2V)

DD TN TP

(1)当V<2V,T 截止,T 导通,V≈V =10V。

i N P o DD

(2)当2V<V<5V,T 工作在饱和区,T 工作

i N P

在可变电阻区。

(3)当V=5V,两管都工作在饱和区,

i

V=(V /2)=5V。

o DD

(4)当5V<V<8V,

i

T 工作在饱和区,

P

T 工作在可变电阻区。

N

(5)当V>8V,T 截止,

i P

T 导通,V=0V。

N o

CMOS门电路的阈值电压

V =V /2

th DD3.工作速度

由于CMOS非门电路工作时总有一个管子导通,所以当带

电容负载时,给电容充电和放电都比较快。CMOS非门的平

均传输延迟时间约为10ns。三、其他的CMOS门电路

1.CMOS与非门和或非门电路

(1)与非门

(2)或非门(3)带缓冲级的门电路

为了稳定输出高低电平,可在输入输出端分别加反相器作

缓冲级。

L = A + B = A ⋅ B2.CMOS异或门电路

由两级组成,前级为或非门,输出为

X = A + B

后级为与或非门,经过逻辑变换,可得:

L = A⋅ B + X = A ⋅ B + A + B = A⋅ B + A⋅ B = A ⊕ B3 .CMOS三态门

当EN=0时,T 和T 同时导通,为正常的非门,

P2 N2

输出

L = A

当EN=1时,T 和T 同时截止,输出为高阻状态。

P2 N2

所以,这是一个低电平有效的三态门。4 .CMOS传输门

工作原理:(设两管的开启电压V =|V |)

TN TP

(1)当C接高电平V , 接低电平0V时,若V 在0V~V 的范围变化,

DD i DD

至少有一管导通,相当于一闭合开关,将输入传到输出,即V =V 。

o i

(2)当C接低电平0V, 接高电平V ,V 在0V~V 的范围变化时,

DD i DD

T 和T 都截止,输出呈高阻状态,相当于开关断开。

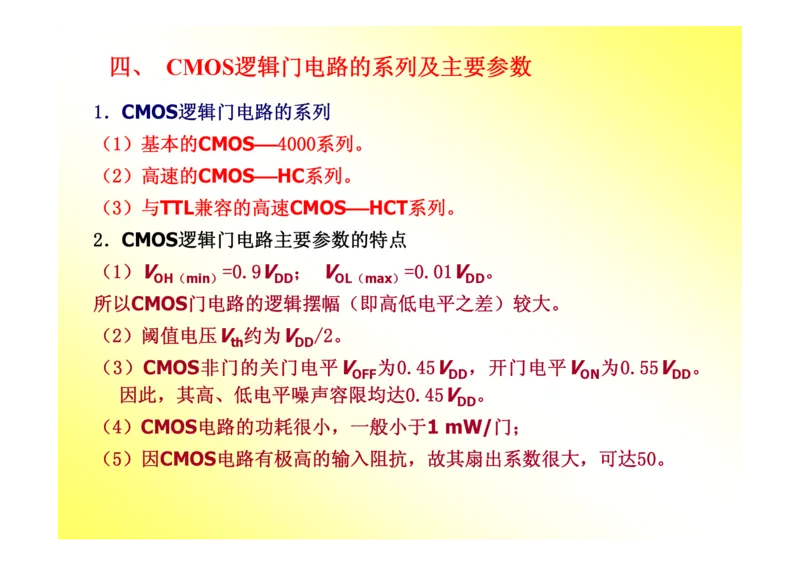

N P四、 CMOS逻辑门电路的系列及主要参数

1.CMOS逻辑门电路的系列

(1)基本的CMOS—— 4000系列。

(2)高速的CMOS——HC系列。

(3)与TTL兼容的高速CMOS——HCT系列。

2.CMOS逻辑门电路主要参数的特点

(1)V =0.9V ; V =0.01V 。

OH(min) DD OL(max) DD

所以CMOS门电路的逻辑摆幅(即高低电平之差)较大。

(2)阈值电压V 约为V /2。

th DD

(3)CMOS非门的关门电平V 为0.45V ,开门电平V 为0.55V 。

OFF DD ON DD

因此,其高、低电平噪声容限均达0.45V 。

DD

(4)CMOS电路的功耗很小,一般小于1 mW/门;

(5)因CMOS电路有极高的输入阻抗,故其扇出系数很大,可达50。2.4 集成逻辑门电路的应用

一、TTL与CMOS器件之间的接口问题

两种不同类型的集成电路相互连接,驱动门必须要为负

载门提供符合要求的高低电平和足够的输入电流,即要

满足下列条件:

驱动门的V ≥负载门的V

OH(min) IH(min)

驱动门的V ≤负载门的V

OL(max) IL(max)

驱动门的I ≥负载门的I

OH(max) IH(总)

驱动门的I ≥负载门的I

OL(max) IL(总)二、TTL和CMOS电路带负载时的接口问题

1.对于电流较小、电平能够匹配

的负载可以直接驱动。

(a)用TTL门电路驱动发光二极

管LED,这时只要在电路中串接

一个约几百Ω的限流电阻即可。

(b)用TTL门电路驱动5V低电

流继电器,其中二极管D 作

保护,用以防止过电压。2.带大电流负载

(a)可将同一芯片上的多个门并联作为驱动器。

(b)也可在门电路输出端接三极管,以提高负载能力。三、多余输入端的处理

(1)对于与非门及与门,

多余输入端应接高电平。如

直接接电源正端,在前级驱

动能力允许时,也可以与有

用的输入端并联使用。

(2)对于或非门及或门,

多余输入端应接低电平,

比如直接接地;也可以与

有用的输入端并联使用。2.5 混合逻辑中逻辑符号的变换

1.逻辑图中任一条线的两端同时加上或消去小圆圈,其逻辑关系不变。

2.任一条线一端上的小圆圈移到另一端,其逻辑关系不变。

3.一端消去或加上小圆圈,同时将相应变量取反,其逻辑关系不变。本章小结

1.最简单的门电路是二极管与门、或门和三极管非门。它们是集

成逻辑门电路的基础。

2.目前普遍使用的数字集成电路主要有两大类,一类由NPN型三极管

组成,简称TTL集成电路;另一类由MOSFET构成,简称MOS集成电路。

3.TTL集成逻辑门电路的输入级采用多发射极三级管、输出级采用达

林顿结构,这不仅提高了门电路的开关速度,也使电路有较强的驱动负

载的能力。在TTL系列中,除了有实现各种基本逻辑功能的门电路以外,

还有集电极开路门和三态门。

4.MOS集成电路常用的是两种结构。一种是NMOS门电路,另一类是

CMOS门电路。与TTL门电路相比,它的优点是功耗低,扇出数大,噪声

容限大,开关速度与TTL接近,已成为数字集成电路的发展方向。

5.为了更好地使用数字集成芯片,应熟悉TTL和CMOS各个系列产品的

外部电气特性及主要参数,还应能正确处理多余输入端,能正确解决不

同类型电路间的接口问题及抗干扰问题。第三章 组合逻辑电路的分析与设计

3.1 逻辑代数

3.2 逻辑函数的卡诺图化简法

3.3 组合逻辑电路的分析方法

3.4 组合逻辑电路的设计方法

3.5 组合逻辑电路中的竞争冒险基 本 公 式

3.1 逻辑代数

一 名 、 称 逻辑代数的基本 公 公 式 式1 公 式 2

A⋅1= A A+ 0 = A

0—1律

A⋅0 = 0 A+1=1

互补律

AA = 0 A+ A =1

A⋅ A = A

重叠律 A+ A = A

交换律 A⋅ B = B⋅ A A+ B = B + A

结合律 A(BC) = (AB)C A+(B +C) = (A+ B)+C

分配律 A(B +C) = AB+ AC A+(BC) = (A+ B)(A+C)

反演律

AB = A + B A + B = A B

A(A+ B) = A A+ AB = A

吸收律

A(A+ B) = AB A+AB= A+B

对合律

A = A公式的证明方法:

(1)用简单的公式证明略为复杂的公式。

A + AB = A + B

例3.1.1 证明吸收律

证: A + AB = A(B + B) + AB = AB + AB + AB = AB + AB + AB + AB

= A(B + B) + B(A + A) = A + B

(2)用真值表证明,即检验等式两边函数的真值表是否一致。

例3.1.2 用真值表证明反演律

AB = A + B

A B AB A + B

0 0 1 1

0 1 1 1

1 0 1 1

1 1 0 0二、逻辑代数的基本规则

1 .代入规则

名称 公式1 公式2

对于任何一个逻辑等式,以某个逻辑变量或逻辑函数同时取代等式

A⋅1= A A+ 0 = A

两端0—任1何 律 一个逻辑变量后,等式依然成立。

A⋅0 = 0 A+1=1

例如,在反演律中用BC去代替等式中的B,则新的等式仍成立:

互补律

AA = 0 A+ A =1

重叠律

ABC =AA⋅ A+=BCA = A + B + C

A+ A = A

2 .对偶规则

交换律

A⋅ B = B⋅ A A+ B = B + A

将一个逻辑函数L进行下列变换:

结合律 A(BC) = (AB)C A+(B +C) = (A+ B)+C

·→+,+ →·

分配律

0 →

1,A

1

( B

→

+

0

C) = AB+ AC A+(BC) = (A+ B)(A+C)

所

反

得

演

新

律

函数表达式叫做LA 的 B 对 = 偶 A + 式 B ,用

L'

表示。 A + B = A B

对偶规则的基本内容A是(A:+如B果) =两A个逻辑函数表达式A相+等AB,=那A么它

吸收律

们的对偶式也一定相等。

A(A + B) = AB A+ AB = A+ B

基本公式中的公式l和公式2就互为对偶 式。

对合律

A = A3 .反演规则

将一个逻辑函数L进行下列变换:

·→+,+ →· ;

0 → 1,1 → 0 ;

原变量 → 反变量, 反变量 → 原变量。

所得新函数表达式叫做L的反函数,用 L 表示。

利用反演规则,可以非常方便地求得一个函数的反函数

例3.1.3 求函数 L = AC + BD 的反函数:

解: L = (A + C)⋅(B + D)

例3.1.4 求函数 L = A⋅ B + C + D 的反函数:

解: L = A + B ⋅C ⋅ D

在应用反演规则求反函数时要注意以下两点:

(1)保持运算的优先顺序不变,必要时加括号表明,如例3.1.3。

(2)变换中,几个变量(一个以上)的公共非号保持不变。如例3.1.4。三、逻辑函数的代数化简法

1.逻辑函数式的常见形式

一个逻辑函数的表达式不是唯一的,可以有多种形式,并

且能互相转换。例如:

L = AC + AB 与 或表达式

——

或 与表达式

= ( A + B)( A + C) ——

与非 与非表达式

= AC ⋅ AB ——

或非 或非表达式

= A + B + A + C ——

与 或 非表达式

= AC + AB —— ——

其中,与—或表达式是逻辑函数的最基本表达形式。2.逻辑函数的最简“与 或表达式” 的标准

—

(1)与项最少,即表达式中“+ 号最少。

”

(2)每个与项中的变量数最少,即表达式中“ 号最少。

· ”

3.用代数法化简逻辑函数

(1)并项法:

运用公式 A + A = 1 将两项合并为一项,消去一个变量。

例: L = A(BC + BC) + A(BC + BC)

= ABC + ABC + ABC + ABC

= AB(C + C) + AB(C + C)

= AB + AB = A(B + B) = A(2)吸收法:

运用吸收律 A+AB=A,消去多余的与项。

例:

L = AB + AB(C + DE) = AB

(3)消去法:

运用吸收律 A + AB = A + B 消去多余因子。

例:

L = A + AB + BE = A + B + BE = A + B + E

(4)配项法:

先通过乘以 (A + A) 或加上 (AA,) 增加必要的乘积项,

再用以上方法化简。

例:

L = AB + AC + BCD = AB + AC + BCD( A + A)

= AB + AC + ABCD + ABCD = AB + AC在化简逻辑函数时,要灵活运用上述方法,才能将逻

辑函数化为最简。

例3.1.6 化简逻辑函数:

L = AD + AD + AB + AC + BD + ABEF + BEF

解: L = A + AB + AC + BD + ABEF + BEF

(利用 )

A + A = 1

= A + AC + BD + BEF ( 利 用 A+AB=A )

= A + C + BD + BEF (利用 A + AB = A + B)例3.1.7 化简逻辑函数:

L = AB + AC + BC + CB + BD + DB + ADE(F + G)

解:

L = ABC + BC + CB + BD + DB + ADE(F + G) (利用反演律 )

= A + BC + CB + BD + DB + ADE(F + G)

(利用 )

A + AB = A + B

= A + BC + CB + BD + DB (利用A+AB=A)

= A + BC(D + D) + CB + BD + DB(C + C) (配项法)

= A + BCD + BC D + CB + BD + DBC + DBC

= A + BC D + CB + BD + DBC (利用A+AB=A)

= A + C D(B + B) + CB + BD

= A + C D + CB + BD (利用 A + A = 1)例3.1.8 化简逻辑函数:L = AB + BC + BC + AB

解法1:L = AB + BC + BC + AB + AC (增加多余项 AC )

= AB + BC + AB + AC (消去一个多余项 BC )

= BC + AB + AC (再消去一个多余项 AB )

解法2:L = AB + BC + BC + AB + AC (增加多余项 AC )

= AB + BC + AB + AC (消去一个多余项 BC )

= AB + BC + AC (再消去一个多余项 AB )

由上例可知,有些逻辑函数的化简结果不是唯一的。

代数化简法的优点:不受变量数目的限制。

缺点:没有固定的步骤可循;需要熟练运用各种公式和定

理;需要一定的技巧和经验;不易判定化简结果是否最简。3.2 逻辑函数的卡诺图化简法

一、 最小项的定义与性质

最小项

——n个变量的逻辑函数中,包含全部变量的乘积项称为最小

项。n变量逻辑函数的全部最小项共有2n个。

三变量函数的最小项

变 量 取 值

最 小 项 编 号

A B C

A B C 0 0 0 m

0

A B C 0 0 1 m

1

A BC 0 1 0 m

2

A BC 0 1 1 m

3

AB C 1 0 0 m

4

AB C 1 0 1 m

5

ABC 1 1 0 m

6

ABC 1 1 1 m

7二、逻辑函数的最小项表达式

任何一个逻辑函数表达式都可以转换为一组最小项之和,

称为最小项表达式。

例1:将函数

L(A, B,C) = AB + AC

转换成最小项表达式。

解: L(A, B,C) = AB + AC = AB(C + C) + AC(B + B)

= ABC + ABC + ABC + ABC =m +m +m +m

7 6 3 1

例2: 将函数 F = AB + AB + AB + C 转换成最小项表达式。

解: F = AB + AB + AB + C = AB + AB ⋅ AB ⋅ C

= AB + (A + B)(A + B)C = AB + ABC + ABC

= AB(C + C) + ABC + ABC = ABC + ABC + ABC + ABC

=m +m +m +m =∑m(3,5,6,7)

7 6 3 5三、卡诺图

1.相邻最小项

如果两个最小项中只有一个变量互为反变量,其余变量

均相同,则称这两个最小项为逻辑相邻,简称相邻项。

如最小项ABC 和 ABC 就是相邻最小项。

如果两个相邻最小项出现在同一个逻辑函数中,可以合并

为一项,同时消去互为反变量的那个量。

如:

ABC + ABC = AC(B + B) = AC

2 .卡诺图

一个小方格代表一个最小项,然后将这些最小项

按照相邻性排列起来。即用小方格几何位置上的

相邻性来表示最小项逻辑上的相邻性。3.卡诺图的结构

(1)二变量卡诺图

A

AB

00 01 11 10

AB m m m m

AB AB AB 0 1 3 2

B

(2)三变量卡诺图

B BC

00 01 11 10

A

m m m m

0 1 3 2

m m m m

0 1 3 2

ABC ABC ABC ABC 0

m m m m

4 5 7 6 m m m m

4 5 7 6

A ABC 1

ABC ABC ABC

C(3)四变量卡诺图

卡诺图具有很强

C

的相邻性:

CD

00 01 11 10

(1)直观相邻性,

AB

m m m m

0 1 3 2 只要小方格在几

00

何 位 置 上 相 邻

ABC D ABCD ABCD ABC D

m m m m ( 不 管 上 下 左

4 5 7 6

右),它代表的

01

ABC D ABCD ABCD ABC D

最小项在逻辑上

B

m m m m

12 13 15 14

一定是相邻的。

11

ABCD

ABC D ABCD ABC D

(2)对边相邻性,

A m m m m

8 9 11 10 即与中心轴对称

10

的左右两边和上

ABC D ABCD ABCD ABC D

下两边的小方格

D

也具有相邻性。四、用卡诺图表示逻辑函数

1.从真值表到卡诺图

例3.2.3 已知某逻辑函数的真值表,用卡诺图表示该逻辑函数。

解: 该函数为三变量,先画出三变量卡诺图,然后根据真值表将8个

最小项L的取值0或者1填入卡诺图中对应的8个小方格中即可。

真值表

B

A B C L

BC

0 0 0 0 A 00 01 11 10

0 0 1 0

0 0 0 1 0

0 1 0 0

0 1 1 1 A 1 0 1 1 1

1 0 0 0

1 0 1 1

C

1 1 0 1

1 1 1 12.从逻辑表达式到卡诺图

(1)如果表达式为最小项表达式,则可直接填入卡诺图。

例3.2.4 用卡诺图表示逻辑函数: F = ABC + ABC + ABC + ABC

解: 写成简化形式: F = m + m + m + m

0 3 6 7

然后填入卡诺图: F

BC

00 01 11 10

A

(2)如不是最小项表达式,应

1 0 1 0

0

先将其先化成最小项表达式,

0 0 1 1

1

再填入卡诺图。也可由“与

—

或”表达式直接填入。

—

C

G

例3.2.5 用卡诺图表示逻辑函数:

0 0 0 0

0 0 0

1

G = AB + BCD B

0 0 0

1

A

解:直接填入:

1 1 1 1

D五、逻辑函数的卡诺图化简法

1.卡诺图化简逻辑函数的原理 :

(1)2个相邻的最小项可以合并,消去1个取值不同的变量。

(2)4个相邻的最小项可以合并,消去2个取值不同的变量。

C C

ABD

C D

1 1 1 1

BCD

1 1

1

B B

1 1 1 1

A A

1 1 1 1

BC

D D

ABD

BD

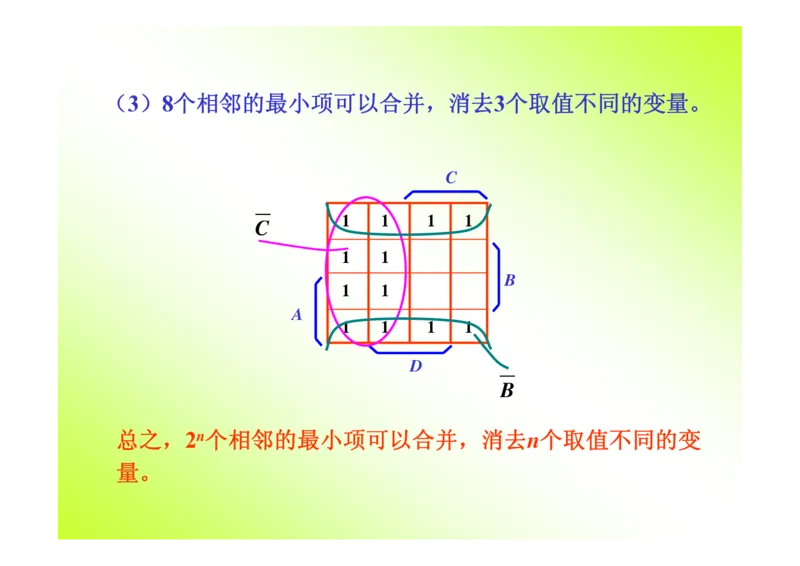

ABC(3)8个相邻的最小项可以合并,消去3个取值不同的变量。

C

1 1 1 1

C

1 1

B

1 1

A

1 1 1 1

D

B

总之,2n个相邻的最小项可以合并,消去n个取值不同的变

量。2.用卡诺图合并最小项的原则(画圈的原则)

(1)尽量画大圈,但每个圈内只能含有2n(n=0,1,2,3……)个相邻项。要特别注

意对边相邻性和四角相邻性。

(2)圈的个数尽量少。

(3)卡诺图中所有取值为1的方格均要被圈过,即不能漏下取值为1的最小项。

(4)在新画的包围圈中至少要含有1个末被圈过的1方格,否则该包围圈是多余的。

3.用卡诺图化简逻辑函数的步骤:

(1)画出逻辑函数的卡诺图。

(2)合并相邻的最小项,即根据前述原则画圈。

(3)写出化简后的表达式。每一个圈写一个最简与项,规则是,取值为l的变量用

原变量表示,取值为0的变量用反变量表示,将这些变量相与。然后将所有与项

进行逻辑加,即得最简与—或表达式。例3.2.6 化简逻辑函数:

L(A,B,C,D)=∑m(0,2,3,4,6,7,10,11,13,14,15)

解:(1)由表达式画出卡诺图。

(2)画包围圈,

合并最小项,

L

得简化的 C A D

与 — 或表达式: 1 0 1 1

1 0 1 1

L = C + A D + ABD

B

0 1 1 1

A

0 0 1 1

ABD C

D例3.2.7 用卡诺图化简逻辑函数:

F = AD + AB D + A B C D + A BC D

解:(1)由表达式画出卡诺图。

(2)画包围圈合并最小项,

得简化的与 — 或表达式: L

C

1 1

0 0

F = AD + B D

0 0 0 0

B

1 1

0 0

注意:图中的绿色圈

A

1 1 1 1

是多余的,应去掉 。

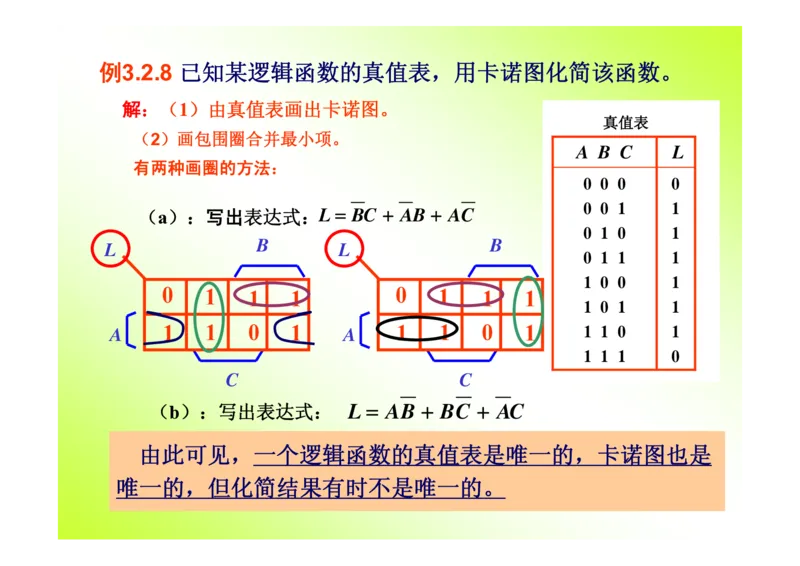

D例3.2.8 已知某逻辑函数的真值表,用卡诺图化简该函数。

解:(1)由真值表画出卡诺图。

真值表

(2)画包围圈合并最小项。

A B C L

有两种画圈的方法:

0 0 0 0

0 0 1 1

(a):写出表达式:L = BC + AB + AC

0 1 0 1

B B

L L

0 1 1 1

1 0 0 1

0 1 1 1 0 1 1 1

1 0 1 1

A 1 1 0 1 A 1 1 0 1 1 1 0 1

1 1 1 0

C C

(b):写出表达式: L = AB + BC + AC

由此可见,一个逻辑函数的真值表是唯一的,卡诺图也是

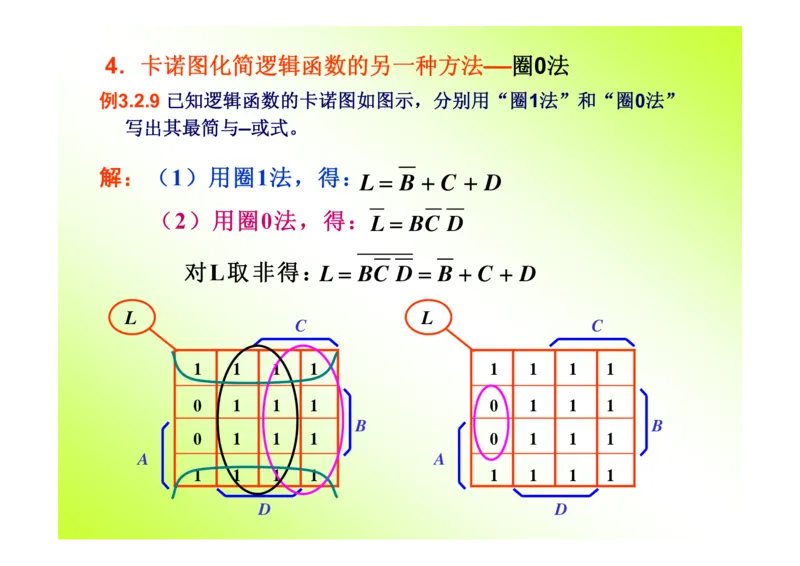

唯一的,但化简结果有时不是唯一的。4.卡诺图化简逻辑函数的另一种方法

——

圈0法

例3.2.9 已知逻辑函数的卡诺图如图示,分别用“圈1法”和“圈0法”

写出其最简与 或式。

—

解:(1)用圈1法,得:

L = B + C + D

(2)用圈0法,得:

L = BC D

对L取非得:

L = BC D = B + C + D

L L

C C

1 1 1 1 1 1 1 1

0 1 1 1 0 1 1 1

B B

0 1 1 1 0 1 1 1

A A

1 1 1 1 1 1 1 1

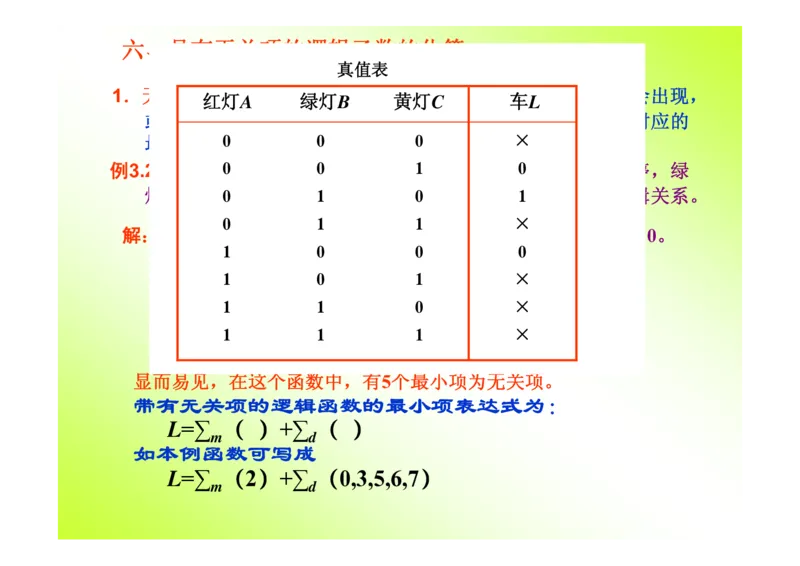

D D六、具有无关项的逻辑函数的化简

真值表

1.无关项

—红—灯

在

A

有 些 逻

绿

辑

灯

函

B

数 中 ,

黄

输

灯

入

C

变量的某

车

些

L

取值组合不会出现,

或者一旦出现,逻辑值可以是任意的。这样的取值组合所对应的

最小项称为0 无 关 项 、 任0 意 项 或 约 束0 项。 ×

例3.2.10:在十0 字 路 口 有 0红 绿 黄 三 色 1交通信号灯,0 规定红灯亮停,绿

灯亮行,黄0 灯 亮 等 一 1等 , 试 分 析 0车行与三色信1 号灯之间逻辑关系。

0 1 1 ×

解:设红、绿、黄灯分别用A、B、C表示,且灯亮为1,灯灭为0。

1 0 0 0

车用L表示,车行L=1,车停L=0。列出该函数的真值。

1 0 1 ×

1 1 0 ×

1 1 1 ×

显而易见,在这个函数中,有5个最小项为无关项。

带有无关项的逻辑函数的最小项表达式为:

L=∑ ( )+∑ ( )

m d

如本例函数可写成

L=∑ (2)+∑ (0,3,5,6,7)

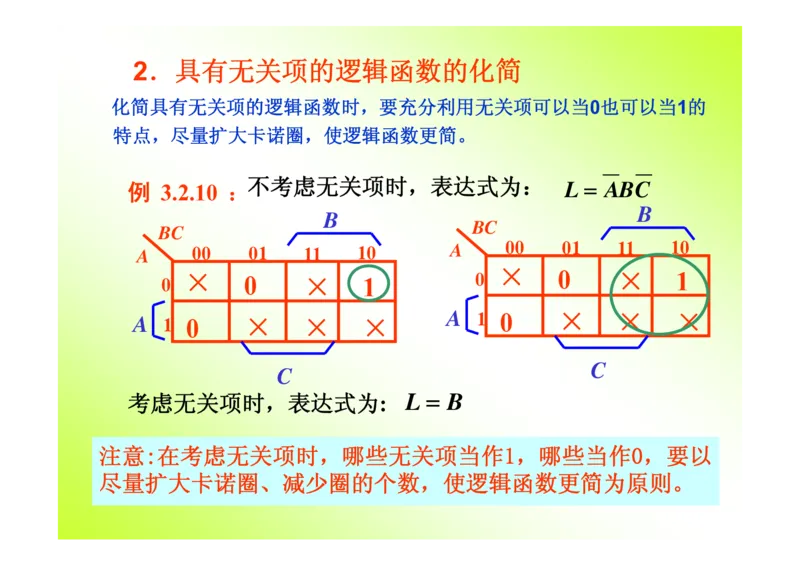

m d2.具有无关项的逻辑函数的化简

化简具有无关项的逻辑函数时,要充分利用无关项可以当0也可以当1的

特点,尽量扩大卡诺圈,使逻辑函数更简。

不考虑无关项时,表达式为:

例 3.2.10 : L = ABC

B

B

BC

BC

A 00 01 11 10 A 00 01 11 10

×

0 × 0 × 1 0 0 × 1

A 1 0 × × ×

A 1 0 × × ×

C

C

考虑无关项时,表达式为: L = B

注意:在考虑无关项时,哪些无关项当作1,哪些当作0,要以

尽量扩大卡诺圈、减少圈的个数,使逻辑函数更简为原则。例3.2.11:某逻辑函数输入是8421BCD码,其逻辑表达式为:

L(A,B,C,D)=∑m(1,4,5,6,7,9)+∑d(10,11,12,13,14,15)

用卡诺图法化简该逻辑函数。

解:(1)画出4变量卡诺图。将1、4、5、6、7、9号小方格填入1;

将10、11、12、13、14、15号小方格填入×。

(2)合并最小项。注意,1方格不能漏。×方格根据需要,可以圈

入,也可以放弃。

L = B + CD

(3)写出逻辑函数的最简与 或表达式:

—

L = AB + BCD

如果不考虑无关项,写出表达式为:

L L

C C

0 1 0 0

0 1 0 0

1 1 1 1

1 1 1 1

B B

× × × ×

× × × ×

A A

0 1 × ×

0 1 × ×

D D3.3 组合逻辑电路的分析方法

一.组合逻辑电路的特点

电路任一时刻的输出状态只决定于该时刻各输入

状态的组合,而与电路的原状态无关。

组合电路就是由门电路组合而成,电路中没有记忆单元,

没有反馈通路。

每一个输出变量是全部

或部分输入变量的函数:

L =f (A 、A 、 … 、A )

1 1 1 2 i

L =f (A 、A 、 … 、A )

2 2 1 2 i

……

L =f (A 、A 、 … 、A )

j j 1 2 i二、组合逻辑电路的分析方法

分析过程一般包含以下几个步骤:

例3.3.1:组合电路如图所示,分析该电路的逻辑功能。解:(1)由逻辑图逐级写出表达式(借助中间变量P)。

P = ABC

L = AP + BP + CP = AABC + BABC + C ABC

(2)化简与变换:

L = ABC(A + B + C) = ABC + A + B + C = ABC + ABC

真值表

(3)由表达式列出真值表。

A B C L

0 0 0 0

(4)分析逻辑功能 :

0 0 1 1

0 1 0 1

当A、B、C三个变量不一致

0 1 1 1

时,输出为“1”,所以这个

1 0 0 1

1 0 1 1

电路称为“不一致电路”。

1 1 0 1

1 1 1 03.4 组合逻辑电路的设计方法

设计过程的基本步骤:

例3.4.1:设计一个三人表决电路,结果按“少数服从多数”的原则决定。

三人表决电路真值表

解:(1)列真值表:

A B C

L

(3)用卡诺图化简。

B

0 0 0 0

BC

0 0 1 0

A 00 01 11 10

0 1 0 0

0 0 1 0

0

0 1 1 1

1 0 0 0

A 1 0 1 1 1

1 0 1 1

1 1 0 1

C

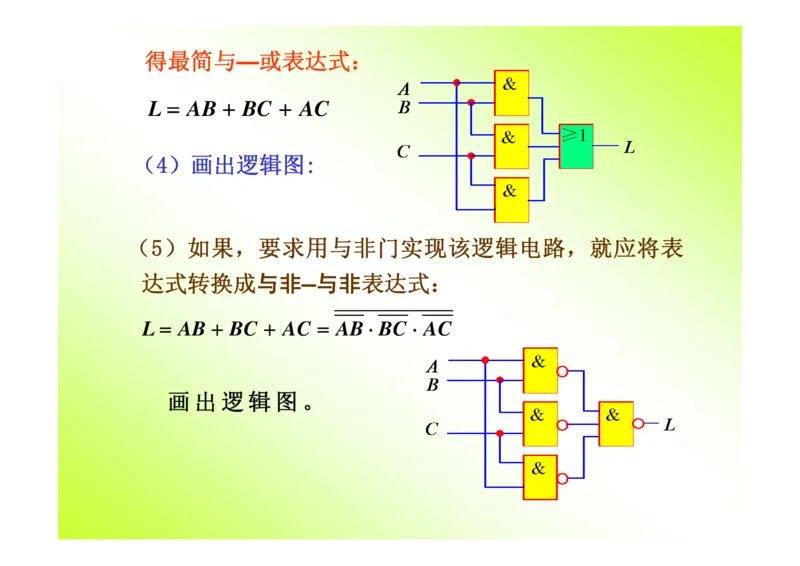

1 1 1 1得最简与—或表达式:

L = AB + BC + AC

(4)画出逻辑图:

(5)如果,要求用与非门实现该逻辑电路,就应将表

达式转换成与非 与非表达式:

—

L = AB + BC + AC = AB ⋅ BC ⋅ AC

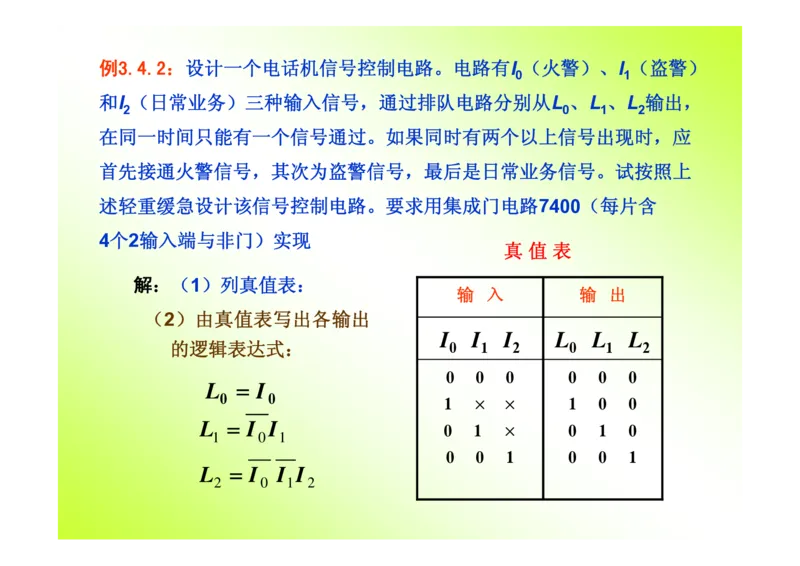

画 出 逻 辑 图 。例3.4.2:设计一个电话机信号控制电路。电路有I (火警)、I (盗警)

0 1

和I (日常业务)三种输入信号,通过排队电路分别从L 、L 、L 输出,

2 0 1 2

在同一时间只能有一个信号通过。如果同时有两个以上信号出现时,应

首先接通火警信号,其次为盗警信号,最后是日常业务信号。试按照上

述轻重缓急设计该信号控制电路。要求用集成门电路7400(每片含

4个2输入端与非门)实现

真 值 表

解:(1)列真值表:

输 入 输 出

(2)由真值表写出各输出

I I I L L L

的逻辑表达式: 0 1 2 0 1 2

0 0 0 0 0 0

L = I

0 0

1 × × 1 0 0

L = I I

0 1 × 0 1 0

1 0 1

0 0 1 0 0 1

L = I I I

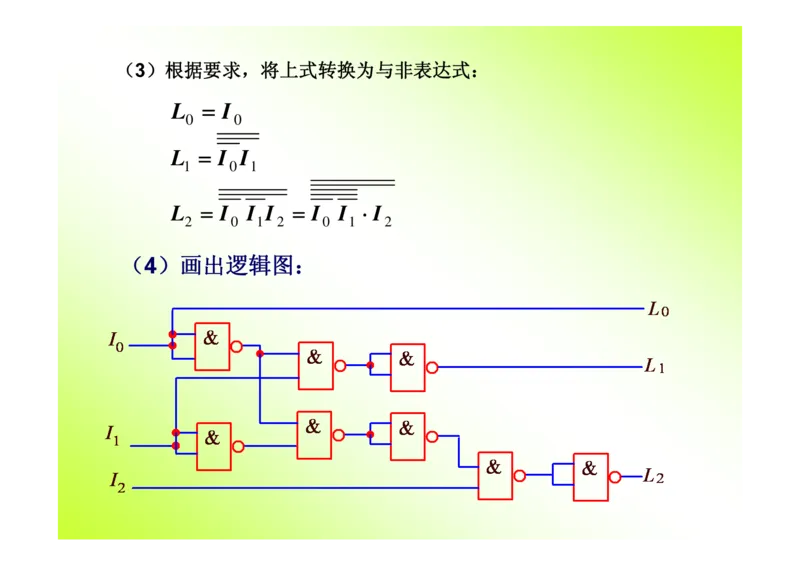

2 0 1 2(3)根据要求,将上式转换为与非表达式:

L = I

0 0

L = I I

1 0 1

L = I I I = I I ⋅ I

2 0 1 2 0 1 2

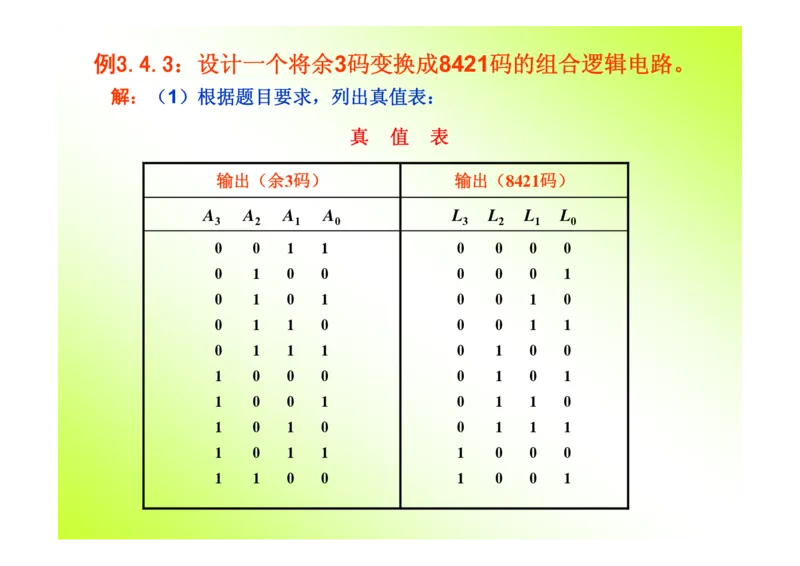

(4)画出逻辑图:例3.4.3:设计一个将余3码变换成8421码的组合逻辑电路。

解:(1)根据题目要求,列出真值表:

真 值 表

输出(余3码) 输出(8421码)

A A A A L L L L

3 2 1 0 3 2 1 0

0 0 1 1 0 0 0 0

0 1 0 0 0 0 0 1

0 1 0 1 0 0 1 0

0 1 1 0 0 0 1 1

0 1 1 1 0 1 0 0

1 0 0 0 0 1 0 1

1 0 0 1 0 1 1 0

1 0 1 0 0 1 1 1

1 0 1 1 1 0 0 0

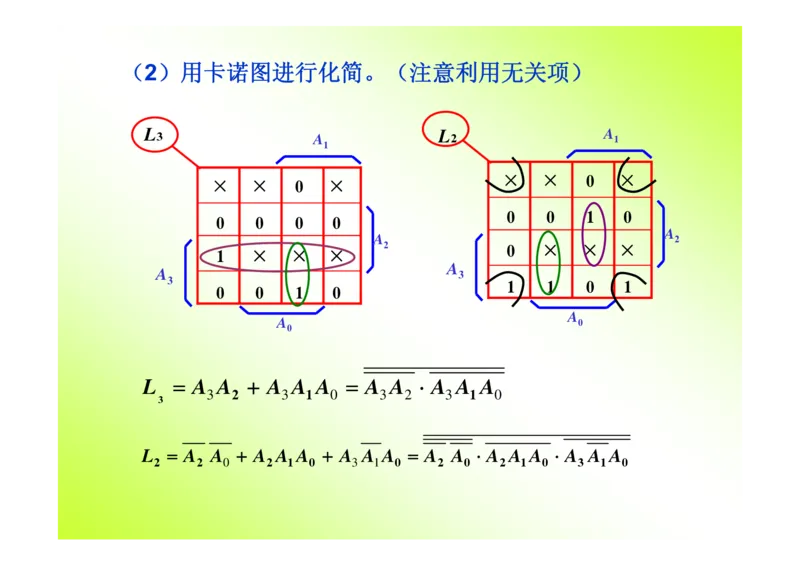

1 1 0 0 1 0 0 1(2)用卡诺图进行化简。(注意利用无关项)

L L A

3 A 2 1

1

× × 0 ×

× × 0 ×

0 0 1 0

0 0 0 0

A

A 2

2 0 × × ×

1 × × ×

A

A

3

3

1 1 0 1

0 0 1 0

A

A 0

0

L = A A + A A A = A A ⋅ A A A

3 2 3 1 0 3 2 3 1 0

3

L = A A + A A A + A A A = A A ⋅ A A A ⋅ A A A

2 2 0 2 1 0 3 1 0 2 0 2 1 0 3 1 0L L

1 A 0 A

1 1

× × 0 × × × 0 ×

0 1 0 1 1 0 0 1

A A

2 2

0 × × × 1 × × ×

A A

3 3

0 1 0 1 1 0 0 1

A A

0 0

L = A A + A A = A ⊕ A

1 1 0 0 1 1 0

L = A

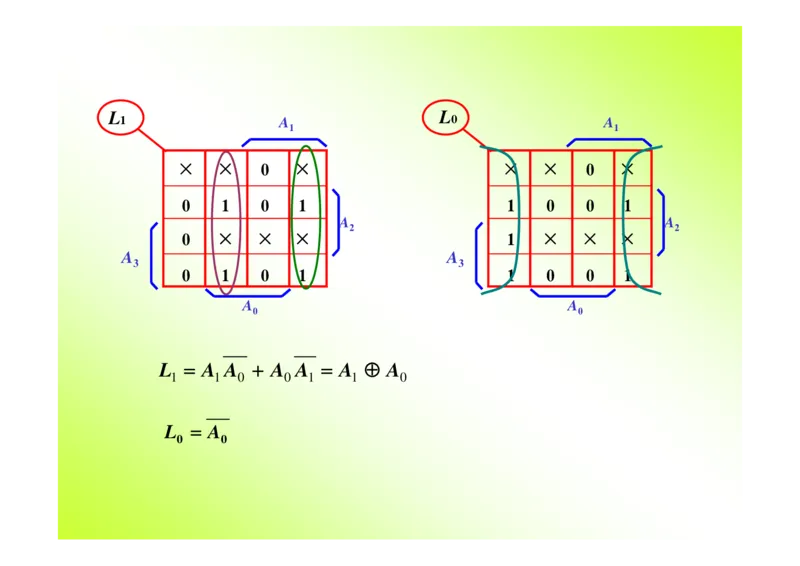

0 0逻辑表达式:

L = A L = A ⊕ A

0 0 1 1 0

L = A A ⋅ A A A ⋅ A A A

2 2 0 2 1 0 3 1 0

L = A A ⋅ A A A

3 2 3 1 0

3

(3)由逻辑表达

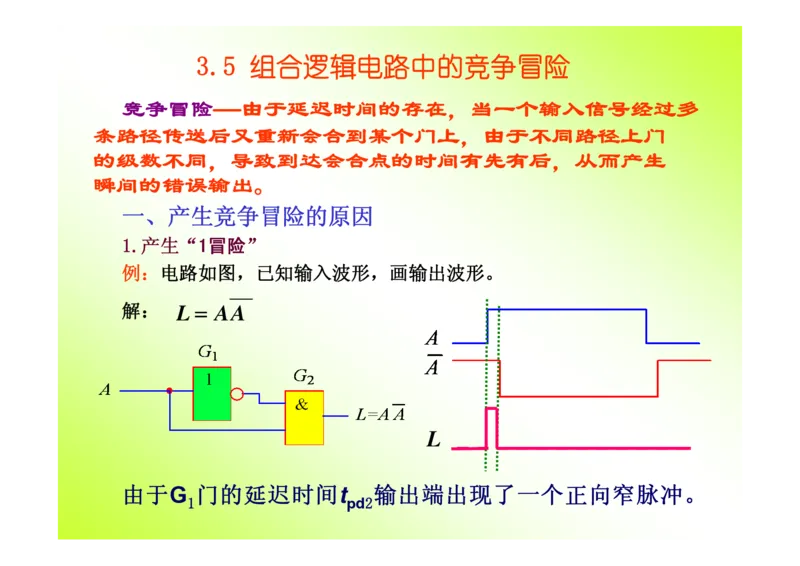

式画出逻辑图。3.5 组合逻辑电路中的竞争冒险

竞争冒险 由于延迟时间的存在,当一个输入信号经过多

——

条路径传送后又重新会合到某个门上,由于不同路径上门

的级数不同,导致到达会合点的时间有先有后,从而产生

瞬间的错误输出。

一、产生竞争冒险的原因

1.产生“1冒险”

例:电路如图,已知输入波形,画输出波形。

解: L = AA

L

由于G 门的延迟时间t 输出端出现了一个正向窄脉冲。

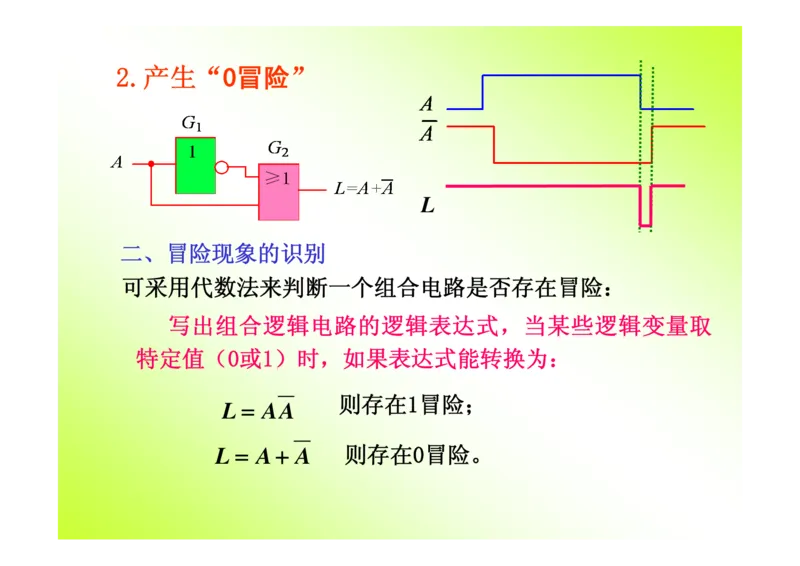

1 pd22.产生“0冒险”

L

二、冒险现象的识别

可采用代数法来判断一个组合电路是否存在冒险:

写出组合逻辑电路的逻辑表达式,当某些逻辑变量取

特定值(0或1)时,如果表达式能转换为:

则存在1冒险;

L = AA

L = A + A 则存在0冒险。例3.5.1: 判断图示电路是否存在冒险,如有,指出冒险类

型,画出输出波形。

L = AC + BC

解:写出逻辑表达式:

L = C + C

若输入变量A=B=l,则有:

因此,该电路存在0冒险。

画出A=B=l 时L的波形。

L例3.5.2: 判断函数 L = (A + B)(B + C) 是否存在冒险:

解:如果令A=C=0,则有 L = B ⋅ B

因此,该电路存在l冒险。

三、冒险现象的消除方法

1.修改逻辑设计

(1)增加冗余项

在例3.5.1的电路中,存在冒险现象。如在其表达式中增加乘积项AB,

使其变为:

L = AC + BC + AB

则在原来产生冒险的条件A=B=1时,L=1,不会产生冒险。

(2)变换逻辑式,消去互补变量

例3.5.2的逻辑式 L = (A + B)(B + C)

存在冒险现象。如将其变换为:L = AB + AC + BC

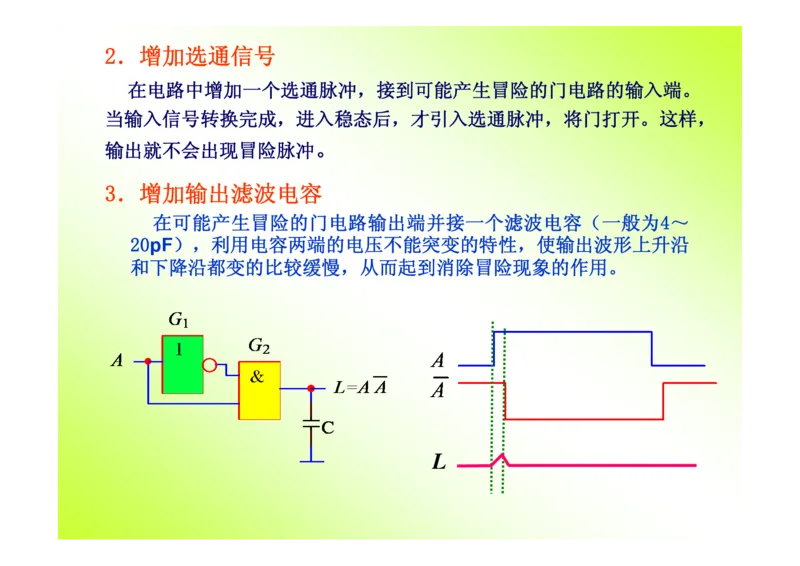

则在原来产生冒险的条件A=C=0时,L=0,不会产生冒险。2.增加选通信号

在电路中增加一个选通脉冲,接到可能产生冒险的门电路的输入端。

当输入信号转换完成,进入稳态后,才引入选通脉冲,将门打开。这样,

。

输出就不会出现冒险脉冲

3.增加输出滤波电容

在可能产生冒险的门电路输出端并接一个滤波电容(一般为4~

20pF),利用电容两端的电压不能突变的特性,使输出波形上升沿

和下降沿都变的比较缓慢,从而起到消除冒险现象的作用。

L本章小结

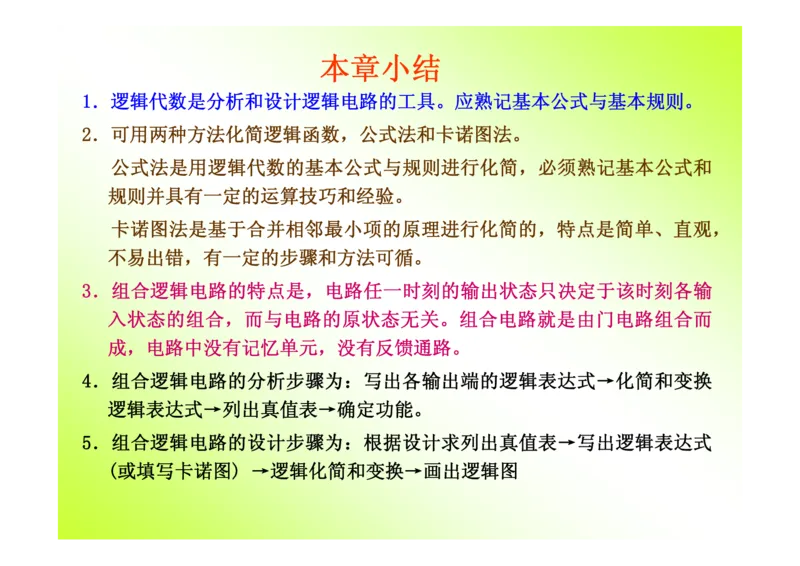

1.逻辑代数是分析和设计逻辑电路的工具。应熟记基本公式与基本规则。

2.可用两种方法化简逻辑函数,公式法和卡诺图法。

公式法是用逻辑代数的基本公式与规则进行化简,必须熟记基本公式和

规则并具有一定的运算技巧和经验。

卡诺图法是基于合并相邻最小项的原理进行化简的,特点是简单、直观,

不易出错,有一定的步骤和方法可循。

3.组合逻辑电路的特点是,电路任一时刻的输出状态只决定于该时刻各输

入状态的组合,而与电路的原状态无关。组合电路就是由门电路组合而

成,电路中没有记忆单元,没有反馈通路。

4.组合逻辑电路的分析步骤为:写出各输出端的逻辑表达式→化简和变换

逻辑表达式→列出真值表→确定功能。

5.组合逻辑电路的设计步骤为:根据设计求列出真值表→写出逻辑表达式

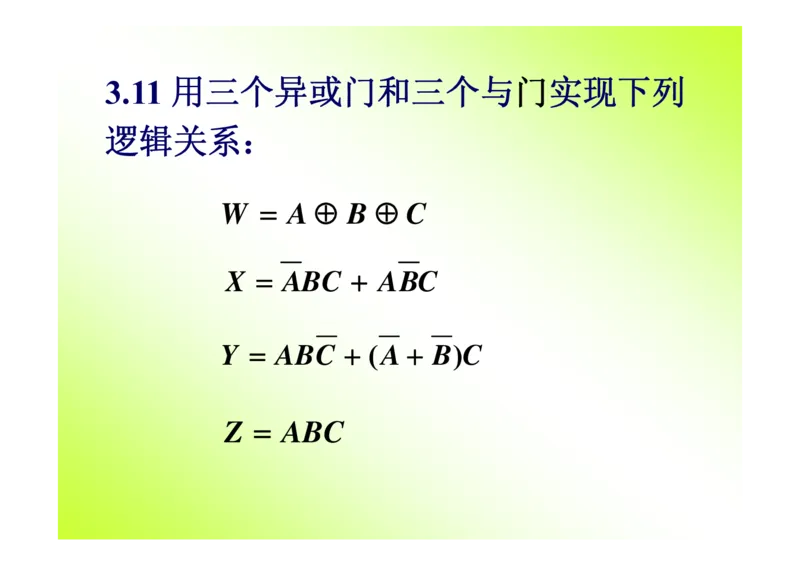

(或填写卡诺图) →逻辑化简和变换→画出逻辑图3.11 用三个异或门和三个与门实现下列

逻辑关系:

W = A ⊕ B ⊕ C

X = ABC + ABC

Y = ABC + ( A + B)C

Z = ABC3.14 试用与非门设计—个组合逻辑电路,

它接收四位二进制数B 、B 、B 、B ,

3 2 1 0

仅当2<B B B B <7时,输出Y才为1。

3 2 1 0

3.15 试用与非门设计一个组合逻辑电路,

它接收一位8421BCD码B 、B 、B 、B ,

3 2 1 0

仅当2<B B B B <7时,输出Y才为1。

3 2 1 0第四章 组合逻辑模块及其应用

4.1 编码器

4.2 译码器

4.3 数据选择器

4.4 数值比较器

4.5 加法器4.1 编码器

一.编码器的基本概念及工作原理

编码 将某一特定的逻辑信号变换为

——

二进制代码。

能够实现编码功能的

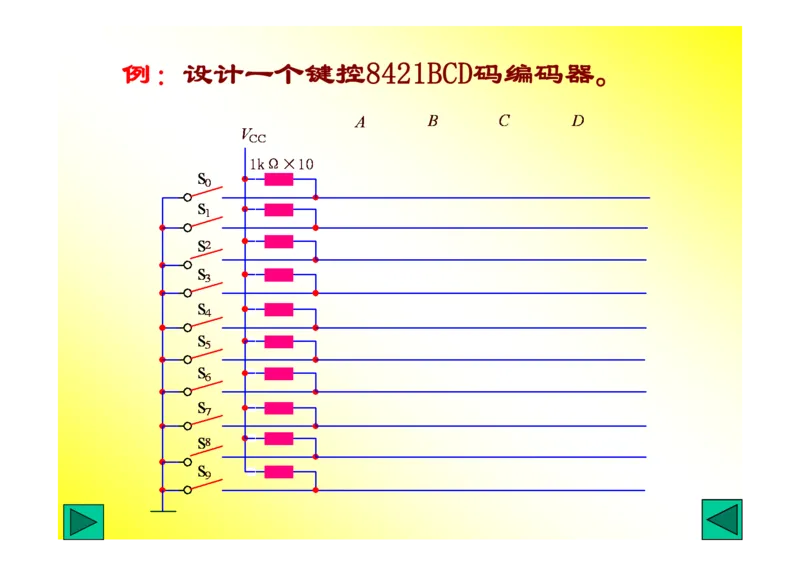

逻辑部件称为编码器。例:设计一个键控8421BCD码编码器。解:(1)列出真值表:

输 入 输 出

S S S S S S S S S S A B C D

9 8 7 6 5 4 3 2 1 0

1 1 1 1 1 1 1 1 1 0 0 0 0 0

1 1 1 1 1 1 1 1 0 1 0 0 0 1

1 1 1 1 1 1 1 0 1 1 0 0 1 0

1 1 1 1 1 1 0 1 1 1 0 0 1 1

1 1 1 1 1 0 1 1 1 1 0 1 0 0

1 1 1 1 0 1 1 1 1 1 0 1 0 1

1 1 1 0 1 1 1 1 1 1 0 1 1 0

1 1 0 1 1 1 1 1 1 1 0 1 1 1

1 0 1 1 1 1 1 1 1 1 1 0 0 0

0 1 1 1 1 1 1 1 1 1 1 0 0 1

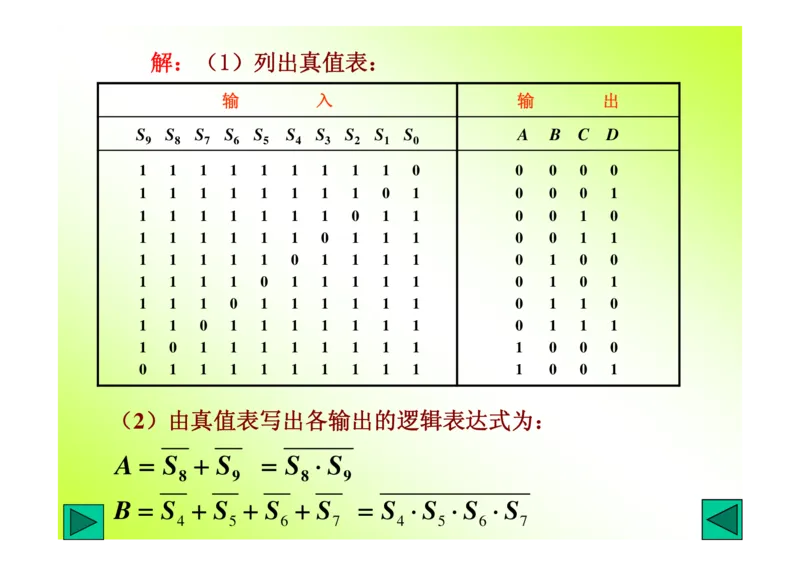

(2)由真值表写出各输出的逻辑表达式为:

A = S + S = S ⋅ S

8 9 8 9

B = S + S + S + S = S ⋅ S ⋅ S ⋅ S

4 5 6 7 4 5 6 7C = S + S + S + S = S ⋅ S ⋅ S ⋅ S

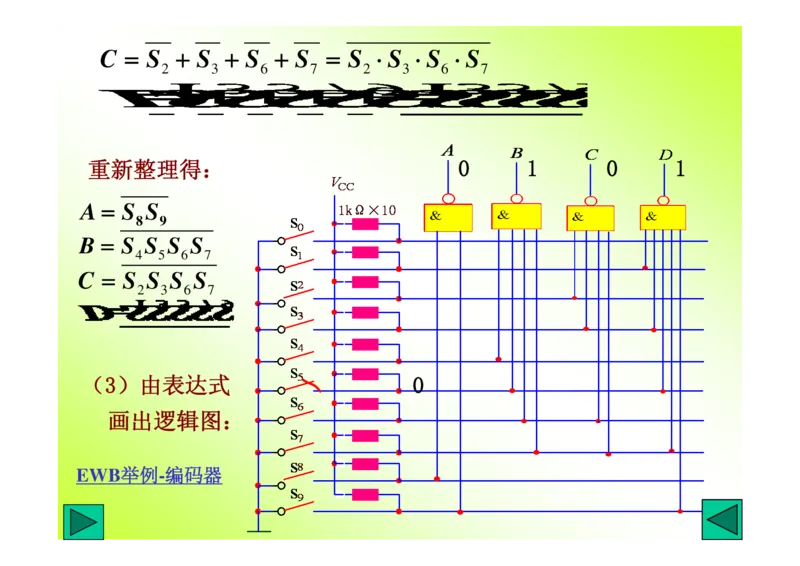

2 3 6 7 2 3 6 7

重新整理得: 0 1 0 1

A = S S

8 9

B = S S S S

4 5 6 7

C = S S S S

2 3 6 7

(3)由表达式 0

画出逻辑图:

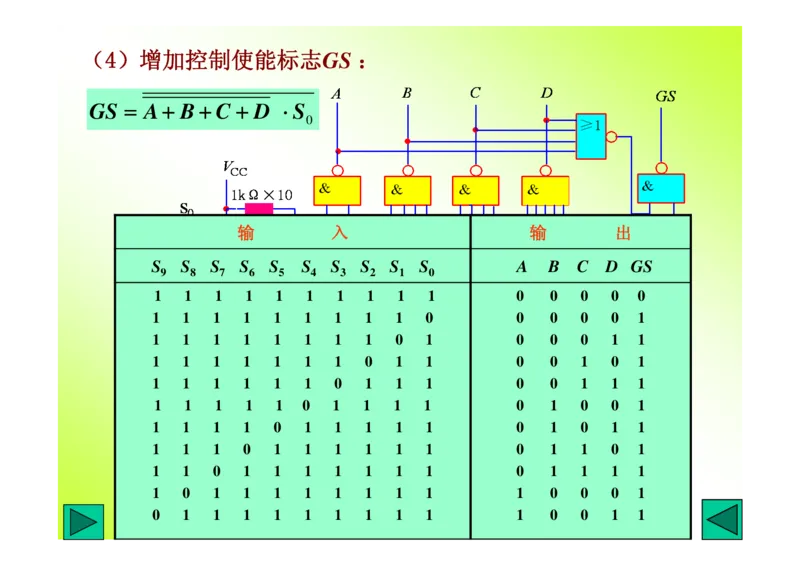

EWB举例-编码器(4)增加控制使能标志GS :

GS = A + B + C + D ⋅ S

0

输 入 输 出

S S S S S S S S S S A B C D GS

9 8 7 6 5 4 3 2 1 0

1 1 1 1 1 1 1 1 1 1 0 0 0 0 0

1 1 1 1 1 1 1 1 1 0 0 0 0 0 1

1 1 1 1 1 1 1 1 0 1 0 0 0 1 1

1 1 1 1 1 1 1 0 1 1 0 0 1 0 1

1 1 1 1 1 1 0 1 1 1 0 0 1 1 1

1 1 1 1 1 0 1 1 1 1 0 1 0 0 1

1 1 1 1 0 1 1 1 1 1 0 1 0 1 1

1 1 1 0 1 1 1 1 1 1 0 1 1 0 1

1 1 0 1 1 1 1 1 1 1 0 1 1 1 1

1 0 1 1 1 1 1 1 1 1 1 0 0 0 1

0 1 1 1 1 1 1 1 1 1 1 0 0 1 1二.二进制编码器

3位二进制编码器:8个输入端,3个输出端,常称为8线—

3线编码器。

3位二进制编码器真值表

输 入 输 出

I I I I I I I I A A A

0 1 2 3 4 5 6 7 2 1 0

1 0 0 0 0 0 0 0 0 0 0

0 1 0 0 0 0 0 0 0 0 1

0 0 1 0 0 0 0 0 0 1 0

0 0 0 1 0 0 0 0 0 1 1

0 0 0 0 1 0 0 0 1 0 0

0 0 0 0 0 1 0 0 1 0 1

0 0 0 0 0 0 1 0 1 1 0

0 0 0 0 0 0 0 1 1 1 1由真值表写出各输出的逻辑表达式为:

A = I I I I A = I I I I

2 4 5 6 7 1 2 3 6 7

A = I I I I

0 1 3 5 7

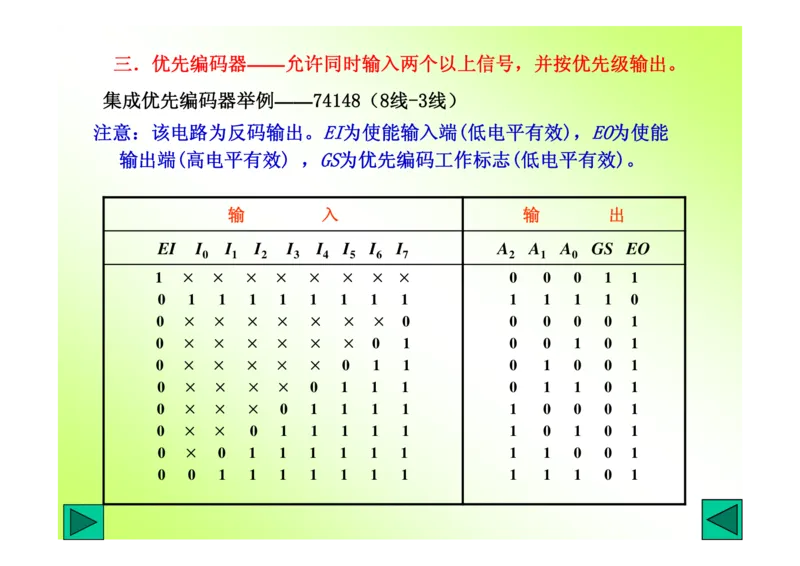

用门电路实现逻辑电路:三.优先编码器——允许同时输入两个以上信号,并按优先级输出。

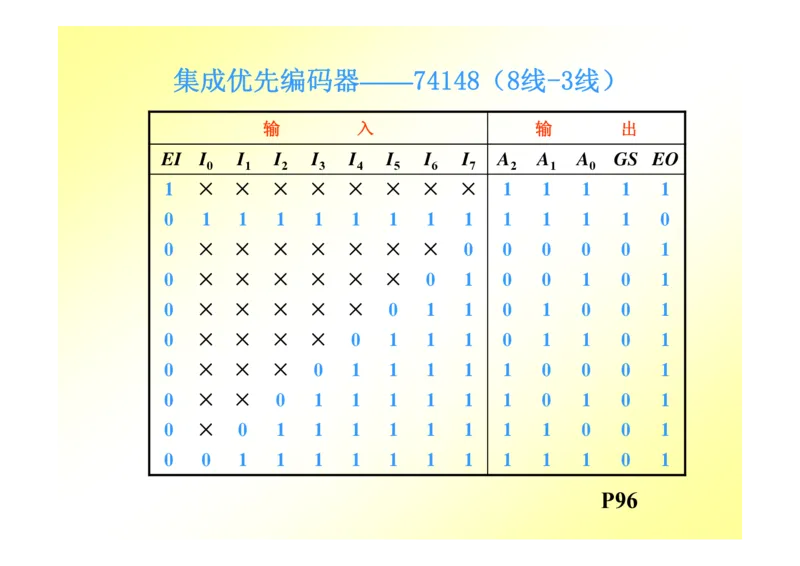

集成优先编码器举例——74148(8线-3线)

注意:该电路为反码输出。EI为使能输入端(低电平有效),EO为使能

输出端(高电平有效) ,GS为优先编码工作标志(低电平有效)。

输 入 输 出

EI I I I I I I I I A A A GS EO

0 1 2 3 4 5 6 7 2 1 0

1 × × × × × × × × 0 0 0 1 1

0 1 1 1 1 1 1 1 1 1 1 1 1 0

0 × × × × × × × 0 0 0 0 0 1

0 × × × × × × 0 1 0 0 1 0 1

0 × × × × × 0 1 1 0 1 0 0 1

0 × × × × 0 1 1 1 0 1 1 0 1

0 × × × 0 1 1 1 1 1 0 0 0 1

0 × × 0 1 1 1 1 1 1 0 1 0 1

0 × 0 1 1 1 1 1 1 1 1 0 0 1

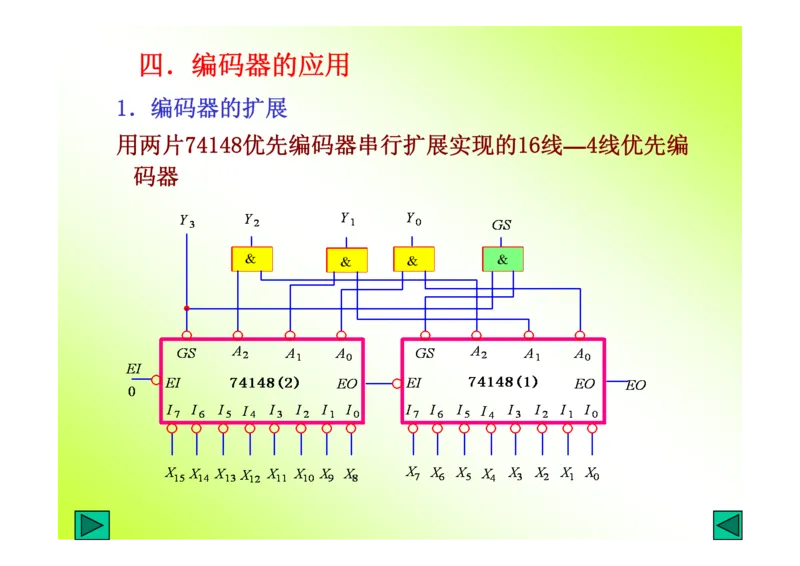

0 0 1 1 1 1 1 1 1 1 1 1 0 1四.编码器的应用

1.编码器的扩展

用两片74148优先编码器串行扩展实现的16线—4线优先编

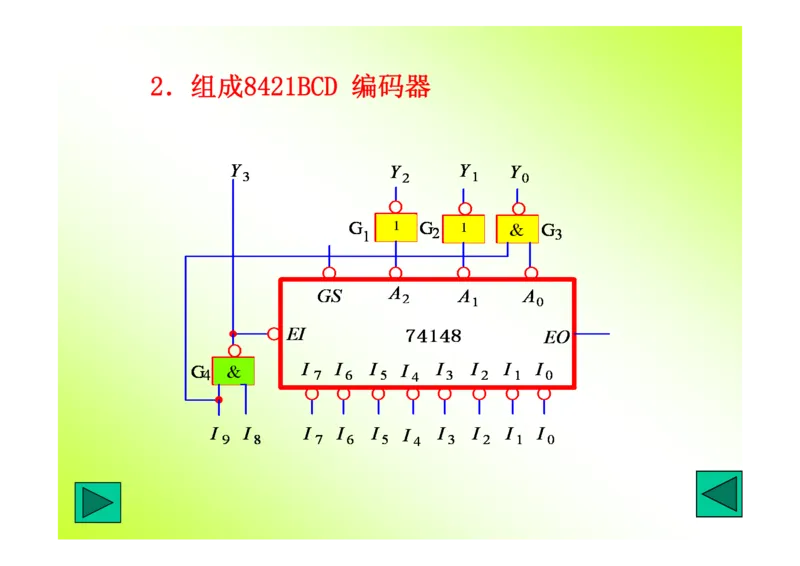

码器2.组成8421BCD 编码器4.2 译码器

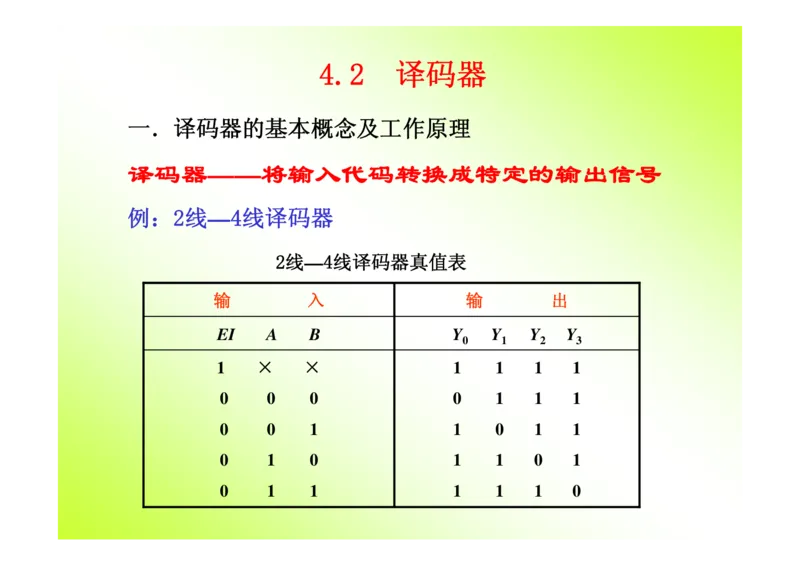

一.译码器的基本概念及工作原理

译码器——将输入代码转换成特定的输出信号

例:2线—4线译码器

2线—4线译码器真值表

输 入 输 出

EI A B Y Y Y Y

0 1 2 3

1 × × 1 1 1 1

0 0 0 0 1 1 1

0 0 1 1 0 1 1

0 1 0 1 1 0 1

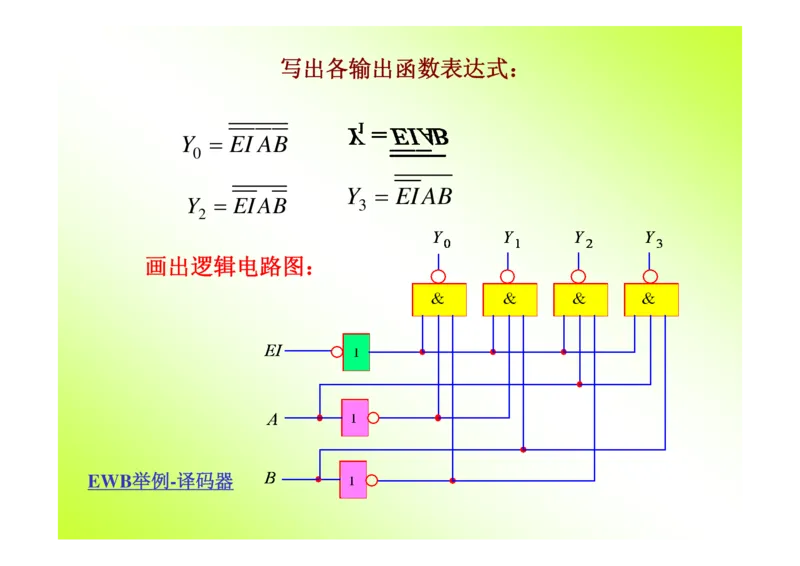

0 1 1 1 1 1 0写出各输出函数表达式:

Y = EI AB

0

Y = EI AB

Y = EI AB 3

2

画出逻辑电路图:

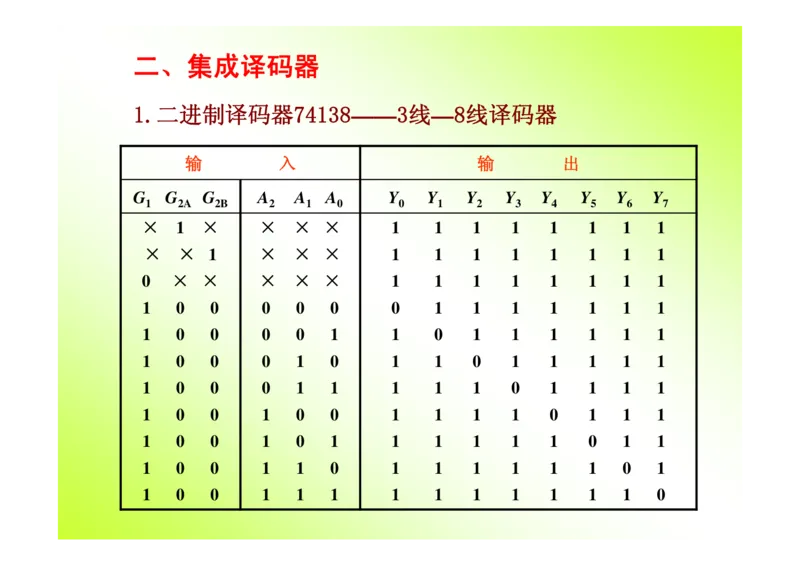

EWB举例-译码器二、集成译码器

1.二进制译码器74138——3线—8线译码器

输 入 输 出

G G G A A A Y Y Y Y Y Y Y Y

1 2A 2B 2 1 0 0 1 2 3 4 5 6 7

× 1 × × × × 1 1 1 1 1 1 1 1

× × 1 × × × 1 1 1 1 1 1 1 1

0 × × × × × 1 1 1 1 1 1 1 1

1 0 0 0 0 0 0 1 1 1 1 1 1 1

1 0 0 0 0 1 1 0 1 1 1 1 1 1

1 0 0 0 1 0 1 1 0 1 1 1 1 1

1 0 0 0 1 1 1 1 1 0 1 1 1 1

1 0 0 1 0 0 1 1 1 1 0 1 1 1

1 0 0 1 0 1 1 1 1 1 1 0 1 1

1 0 0 1 1 0 1 1 1 1 1 1 0 1

1 0 0 1 1 1 1 1 1 1 1 1 1 02.8421BCD译码器74424线-10线译码器7442真值表

输 入 输 出

A A A A Y Y Y Y Y Y Y Y Y Y

3 2 1 0 0 1 2 3 4 5 6 7 8 9

0 0 0 0 0 1 1 1 1 1 1 1 1 1

0 0 0 1 1 0 1 1 1 1 1 1 1 1

0 0 1 0 1 1 0 1 1 1 1 1 1 1

0 0 1 1 1 1 1 0 1 1 1 1 1 1

0 1 0 0 1 1 1 1 0 1 1 1 1 1

0 1 0 1 1 1 1 1 1 0 1 1 1 1

0 1 1 0 1 1 1 1 1 1 0 1 1 1

0 1 1 1 1 1 1 1 1 1 1 0 1 1

1 0 0 0 1 1 1 1 1 1 1 1 0 1

1 0 0 1 1 1 1 1 1 1 1 1 1 0

1 0 1 0 1 1 1 1 1 1 1 1 1 1

1 0 1 1 1 1 1 1 1 1 1 1 1 1

1 1 0 0 1 1 1 1 1 1 1 1 1 1

1 1 0 1 1 1 1 1 1 1 1 1 1 1

1 1 1 0 1 1 1 1 1 1 1 1 1 1

1 1 1 1 1 1 1 1 1 1 1 1 1 1三、译码器的应用

1.译码器的扩展

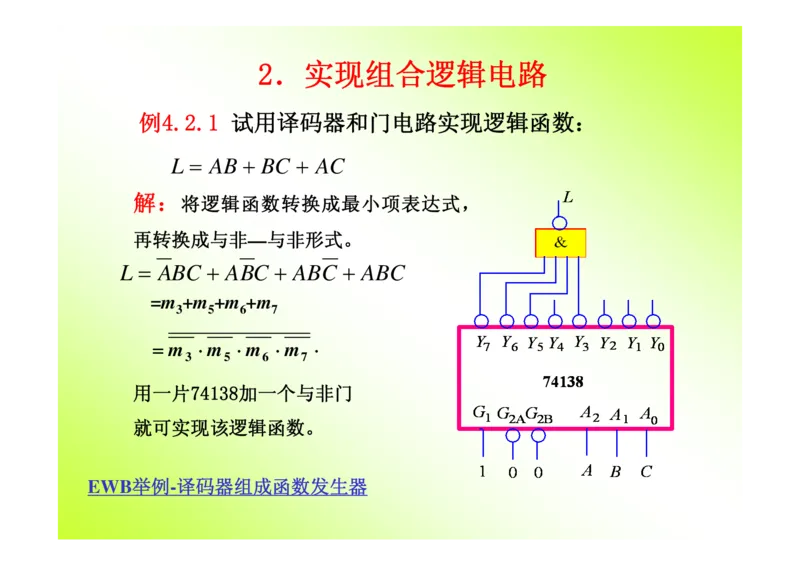

用两片74138扩展为4线—16线译码器2.实现组合逻辑电路

例4.2.1 试用译码器和门电路实现逻辑函数:

L = AB + BC + AC

解:

将逻辑函数转换成最小项表达式,

再转换成与非—与非形式。

L = ABC + ABC + ABC + ABC

=m +m +m +m

3 5 6 7

= m ⋅ m ⋅ m ⋅ m ⋅

3 5 6 7

用一片74138加一个与非门

就可实现该逻辑函数。

EWB举例-译码器组成函数发生器真值表

例4.2.2 已知某组合逻辑

电路的真值表,试用译码 输 入 输 出

A B C L F G

器和门电路设计该逻辑电

0 0 0 0 0 1

路。

0 0 1 1 0 0

0 1 0 1 0 1

0 1 1 0 1 0

解:写出各输出的最小

1 0 0 1 0 1

项表达式,再转换成 1 0 1 0 1 0

1 1 0 0 1 1

与非—与非形式:

1 1 1 1 0 0

L = ABC + ABC + ABC + ABC = m + m + m + m = m ⋅ m ⋅ m ⋅ m

1 2 4 7 1 2 4 7

F = ABC + ABC + ABC = m + m + m = m ⋅ m ⋅ m

3 5 6 3 5 6

G = ABC + ABC + ABC + ABC = m + m + m + m = m ⋅ m ⋅ m ⋅ m

0 2 4 6 0 2 4 6与非—与非形式:

L = m ⋅ m ⋅ m ⋅ m

1 2 4 7

F = m ⋅ m ⋅ m

3 5 6

G = m ⋅ m ⋅ m ⋅ m

0 2 4 6

用一片74138加三个与非门

就可实现该组合逻辑电路。

可见,用译码器实现多输出

逻辑函数时,优点更明显。3.构成数据分配器

数据分配器——将一路输入数据根据地址选择码分配给多

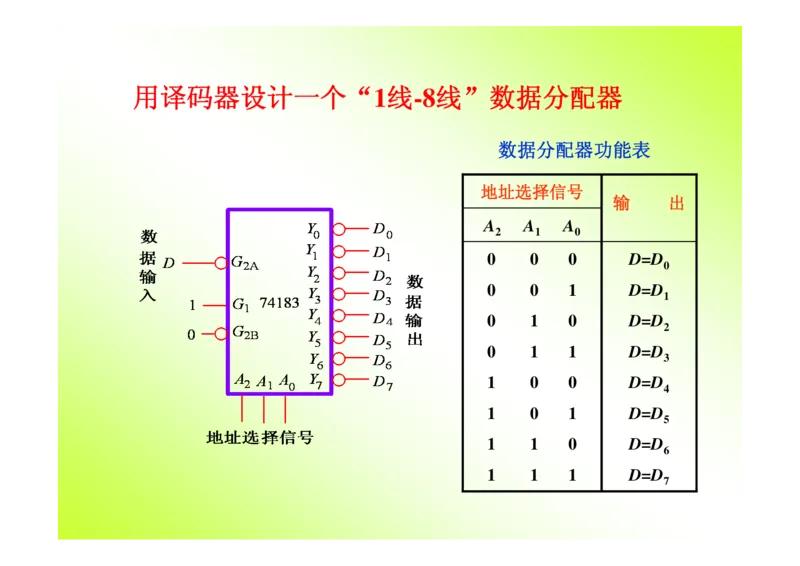

路数据输出中的某一路输出。用译码器设计一个“1线-8线”数据分配器

数据分配器功能表

地址选择信号

输 出

A A A

2 1 0

0 0 0 D=D

0

0 0 1 D=D

1

0 1 0 D=D

2

0 1 1 D=D

3

1 0 0 D=D

4

1 0 1 D=D

5

1 1 0 D=D

6

1 1 1 D=D

7四、数字显示译码器

数字显示器分类:

按显示方式分,有字型重叠式、点阵式、分段式等。

按发光物质分,有发光二极管(LED)式、荧光式、液晶显示等。

1.七段式LED显示器LED显示器有两种结构:

共阳极: 共阴极:

2.七段显示译码器7448

7448是一种与共阴极数字

显示器配合使用的集成译

码器。七段显示译码器7448的功能表

功能 输 入 输入/输出 输 出 显示

(输入) 字形

LT RBI A A A A BI/RBO a b c d e f g

3 2 1 0

0 1 1 0 0 0 0 1 1 1 1 1 1 1 0

1 1 × 0 0 0 1 1 0 1 1 0 0 0 0

2 1 × 0 0 1 0 1 1 1 0 1 1 0 1

3 1 × 0 0 1 1 1 1 1 1 1 0 0 1

4 1 × 0 1 0 0 1 0 1 1 0 0 1 1

5 1 × 0 1 0 1 1 1 0 1 1 0 1 1

6 1 × 0 1 1 0 1 0 0 1 1 1 1 1

7 1 × 0 1 1 1 1 1 1 1 0 0 0 0

8 1 × 1 0 0 0 1 1 1 1 1 1 1 1

9 1 × 1 0 0 1 1 1 1 1 0 0 1 1

10 1 × 1 0 1 0 1 0 0 0 1 1 0 1

11 1 × 1 0 1 1 1 0 0 1 1 0 0 1

12 1 × 1 1 0 0 1 0 1 0 0 0 1 1

13 1 × 1 1 0 1 1 1 0 0 1 0 1 0

14 1 × 1 1 1 0 1 0 0 0 1 1 1 1

15 1 × 1 1 1 1 1 0 0 0 0 0 0 0

灭灯 × × × × × × 0 0 0 0 0 0 0 0

灭零 1 0 0 0 0 0 0 0 0 0 0 0 0 0

试灯 0 × × × × × 1 1 1 1 1 1 1 17448的逻辑功能:

(1)正常译码显示。LT=1,BI/RBO=1时,对输入为十进制数l~15的

二进制码(0001~1111)进行译码,产生对应的七段显示码。

(2)灭零。当LT=1,而输入为0的二进制码0000时,只有当RBI =1时,

才产生0的七段显示码,如果此时输入RBI =0 ,则译码器的a~g输出

全0,使显示器全灭;所以RBI称为灭零输入端。

(3)试灯。当LT=0时,无论输入怎样,a~g输出全1,数码管七段全

亮。由此可以检测显示器七个发光段的好坏。 LT称为试灯输入端。

(4)特殊控制端BI/RBO。BI/RBO可以作输入端,也可以作输出端。

作输入使用时,如果BI=0时,不管其他输入端为何值,a~g均输出0,

显示器全灭。因此BI称为灭灯输入端。

作输出端使用时,受控于RBI。当RBI=0,输入为0的二进制码0000时,

RBO=0,用以指示该片正处于灭零状态。所以,RBO 又称为灭零输

出端。将BI/RBO和RBI配合使用,可以实现多位数显

示时的“无效0消隐”功能。4.3 数据选择器

一、 数据选择器的基本概念及工作原理

数据选择器——根据地址选择码从多路输入数据中选择一

路,送到输出。例:四选一数据选择器

四选一数据选择器的真值表

输 入 输 出

G A A D D D D Y

1 0 3 2 1 0

1 × × × × × × 0

× × × 0 0

0 0

× × × 1 1

× × 0 × 0

0 1

× × 1 × 1

× 0 × × 0

0

1 0

× 1 × × 1

0 × × × 0

1 1

1 × × × 1

根据功能表,可写出输出逻辑表达式:

Y = ( A A D + A A D + A A D + A A D )⋅G

1 0 0 1 0 1 1 0 2 1 0 3Y = ( A A D + A A D + A A D + A A D )⋅G

1 0 0 1 0 1 1 0 2 1 0 3

由逻辑表达式画出逻辑图:二、集成数据选择器

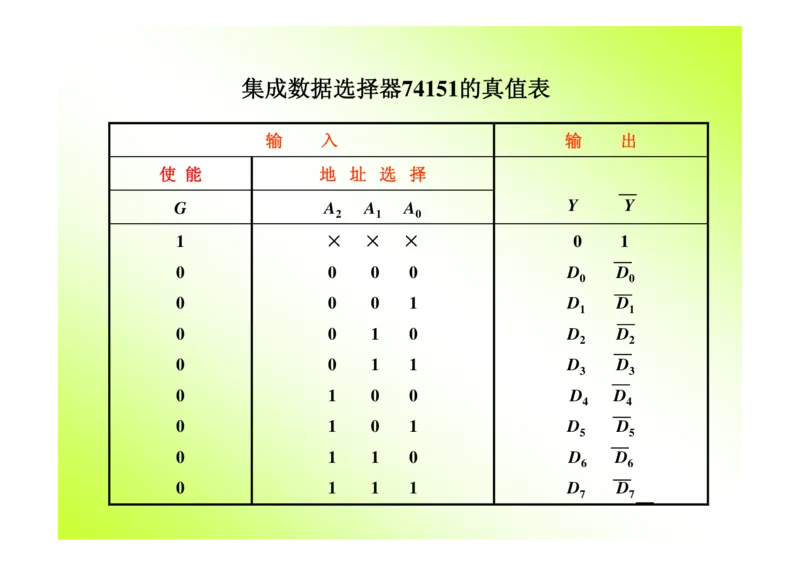

集 成 数 据 选 择 器74151

(8选1数据选择器)集成数据选择器74151的真值表

输 入 输 出

使 能 地 址 选 择

G A A A Y Y

2 1 0

1 × × × 0 1

0 0 0 0 D D

0 0

0 0 0 1 D D

1 1

0 0 1 0 D D

2 2

0 0 1 1 D D

3 3

0 1 0 0 D D

4 4

0 1 0 1 D D

5 5

0 1 1 0 D D

6 6

0 1 1 1 D D

7 7三、数据选择器的应用

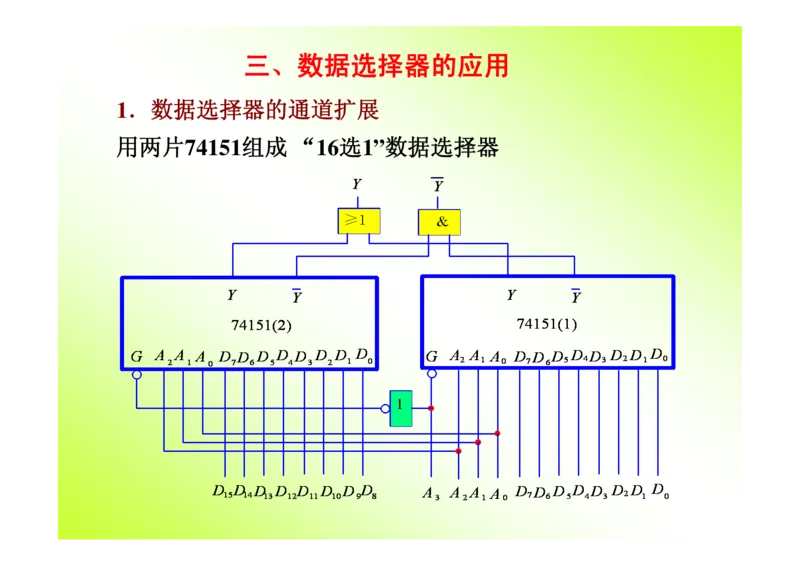

1.数据选择器的通道扩展

用两片74151组成 “16选1”数据选择器2.实现组合逻辑函数

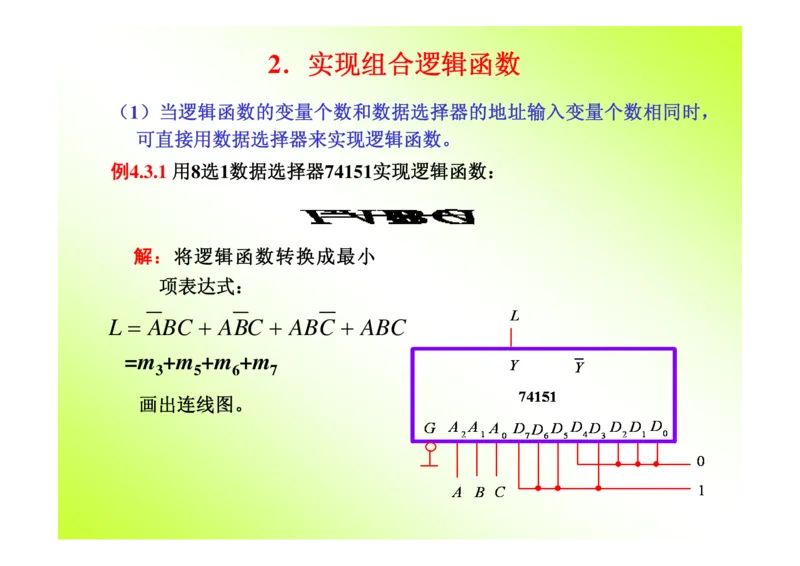

(1)当逻辑函数的变量个数和数据选择器的地址输入变量个数相同时,

可直接用数据选择器来实现逻辑函数。

例4.3.1 用8选1数据选择器74151实现逻辑函数:

解:将逻辑函数转换成最小

项表达式:

L = ABC + ABC + ABC + ABC

=m +m +m +m

3 5 6 7

画出连线图。(2)当逻辑函数的变量个数大于数据选择器的地址输入变量个数时。

例4.3.2 试用4选1数据选择器实现逻辑函数:

L = AB + BC + AC

解:将A、B接到地址输入端,C加到适当的数据输入端。

作出逻辑函数L的真值表,根据真值表画出连线图。

真值表

A B C L

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 1

1 0 1 0

1 1 0 1

1 1 1 14.4 数值比较器

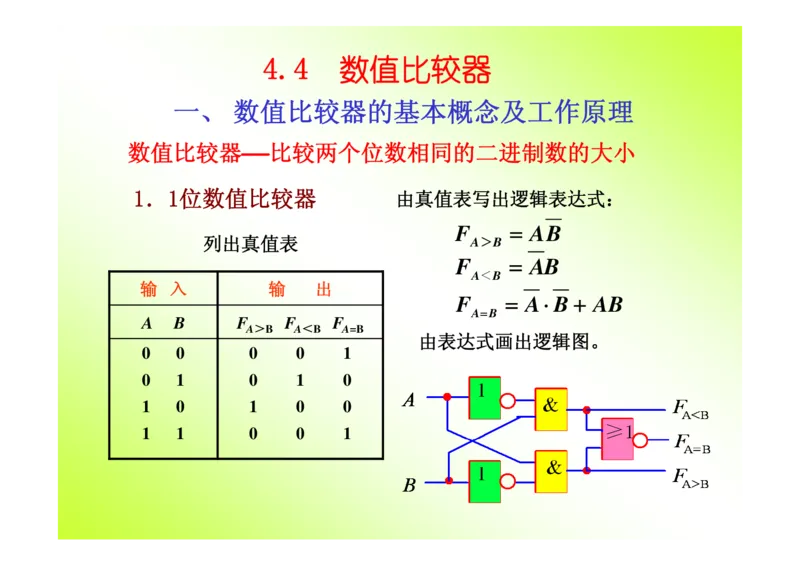

一、 数值比较器的基本概念及工作原理

数值比较器 比较两个位数相同的二进制数的大小

——

1.1位数值比较器 由真值表写出逻辑表达式:

F = AB

列出真值表 A>B

F = AB

A<B

输 入 输 出

F = A⋅ B + AB

A=B

A B F F F

A>B A<B A=B

由表达式画出逻辑图。

0 0 0 0 1

0 1 0 1 0

1 0 1 0 0

1 1 0 0 1.考虑低位比较结果的多位比较器

2

例: 位数值比较器

2

位数值比较器的真值表

2

数 值 输 入 级 联 输 入 输 出

A B A B I I I F F F

1 1 0 0 A>B A<B A=B A>B A<B A=B

A > B × × × × × 1 0 0

1 1

A < B × × × × × 0 1 0

1 1

A = B A > B × × × 1 0 0

1 1 0 0

A = B A < B × × × 0 1 0

1 1 0 0

A = B A = B 1 0 0 1 0 0

1 1 0 0

A = B A = B 0 1 0 0 1 0

1 1 0 0

A = B A = B 0 0 1 0 0 1

1 1 0 0由真值表写出逻辑表达式:

F = (A>B )+ (A = B )⋅(A >B )+ (A = B )⋅(A = B )⋅ I

A>B 1 1 1 1 0 0 1 1 0 0 A>B

F = (A <B )+ (A = B )⋅(A <B )+ (A = B )⋅(A = B )⋅ I

A<B 1 1 1 1 0 0 1 1 0 0 A<B

F = (A = B )⋅(A = B )⋅ I

A=B 1 1 0 0 A=B

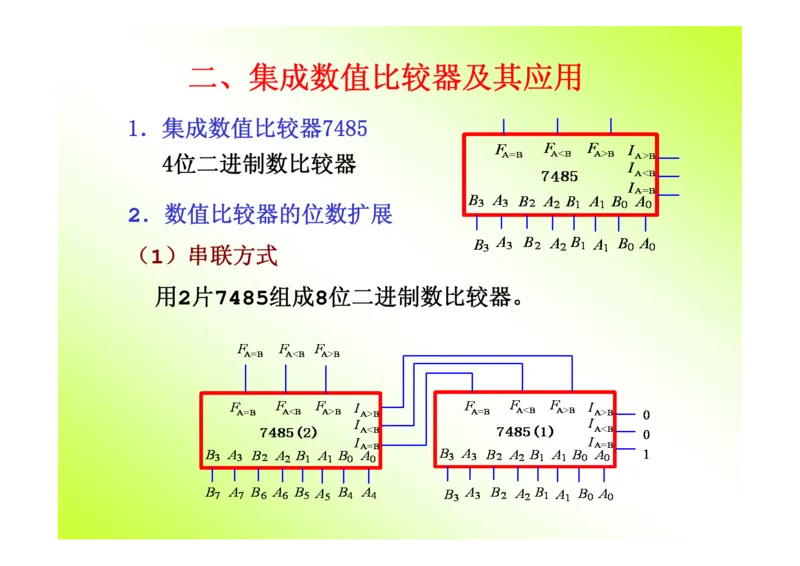

由表达式画出逻辑图:二、集成数值比较器及其应用

1.集成数值比较器7485

4位二进制数比较器

.数值比较器的位数扩展

2

( )串联方式

1

用 片 组成 位二进制数比较器。

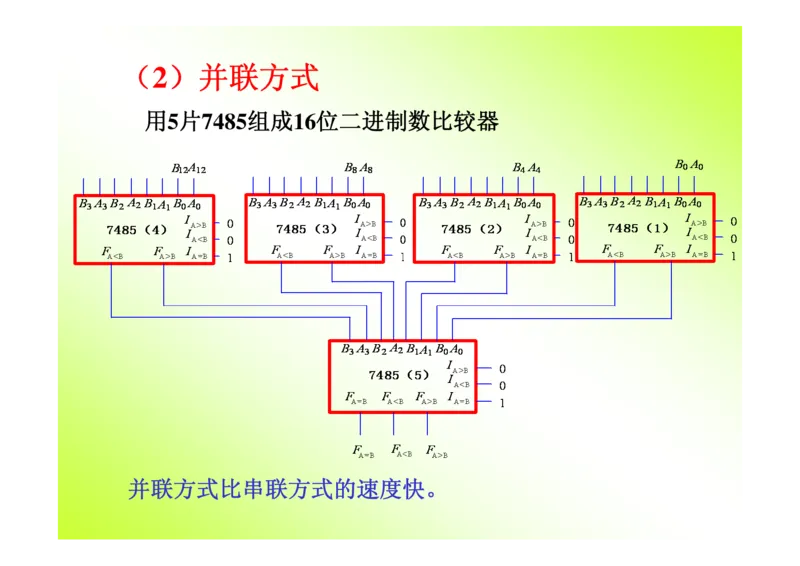

2 7485 8(2)并联方式

用5片7485组成16位二进制数比较器

并联方式比串联方式的速度快。4.5 加法器

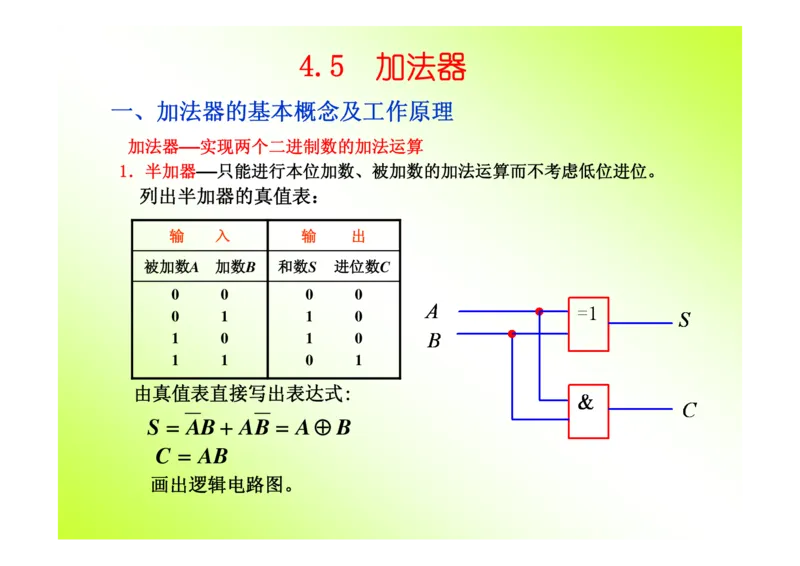

一、加法器的基本概念及工作原理

加法器——实现两个二进制数的加法运算

1.半加器——只能进行本位加数、被加数的加法运算而不考虑低位进位。

列出半加器的真值表:

输 入 输 出

被加数A 加数B 和数S 进位数C

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

由真值表直接写出表达式:

S = AB + AB = A ⊕ B

C = AB

画出逻辑电路图。如果想用与非门组成半加器,则将上式用变换成与非形式:

S = AB + AB = AB + AB + AA + BB

= A(A + B) + B(A + B) = A ⋅ AB + B ⋅ AB

= A ⋅ AB ⋅ B ⋅ AB

画出用与非门组成的半加器。2.全加器 能同时进行本位数和相邻低位的进位信号的加法运算。

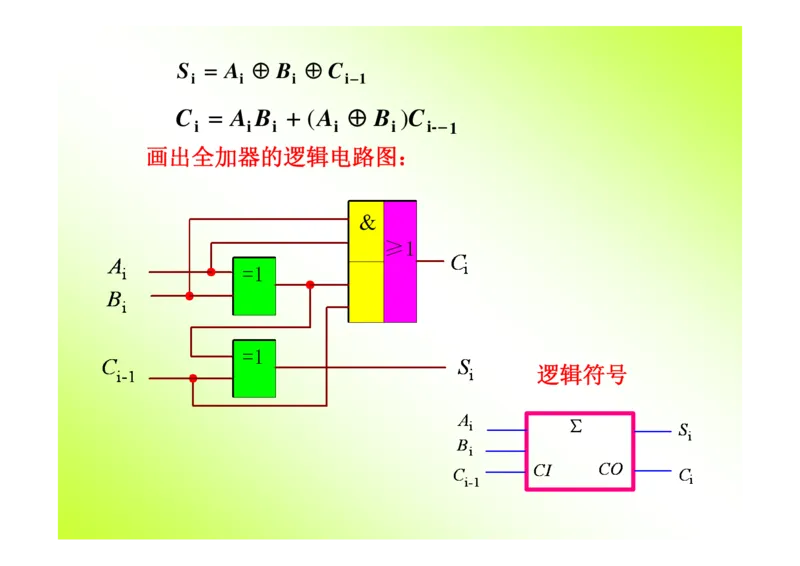

——

输 入 输 出

A B C S C

i i i-1 i i

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

由真值表直接写出逻辑表达式,再经代数法化简和转换得:

S = A ⋅ B C + A B C + A B ⋅ C + A B C

i i i i−1 i i i−1 i i i−1 i i i−1

= (A ⊕ B )C + (A ⊕ B )C = A ⊕ B ⊕ C

i i i−1 i i i−1 i i i−1

C = A B C + A B C + A B C + A B C

i i i i−1 i i i−1 i i i−1 i i i−1

= A B + (A ⊕ B )C

i i i i i-−1S = A ⊕ B ⊕ C

i i i i−1

C = A B + (A ⊕ B )C

i i i i i i-−1

画出全加器的逻辑电路图:

逻辑符号二、多位数加法器

4位串行进位加法器本章小结

1.常用的中规模组合逻辑器件包括编码器、译码器、数据

选择器、数值比较器、加法器等。

2.上述组合逻辑器件除了具有其基本功能外,还可用来设

计组合逻辑电路。应用中规模组合逻辑器件进行组合逻

辑电路设计的一般原则是:使用MSI芯片的个数和品种型

号最少,芯片之间的连线最少

3.用MSI芯片设计组合逻辑电路最简单和最常用的方法是,

用数据选择器设计多输入、单输出的逻辑函数;用二进

制译码器设计多输入、多输出的逻辑函数。第五章 触发器

5.1 基本触发器

5.2 主从触发器

5.3 边沿触发器

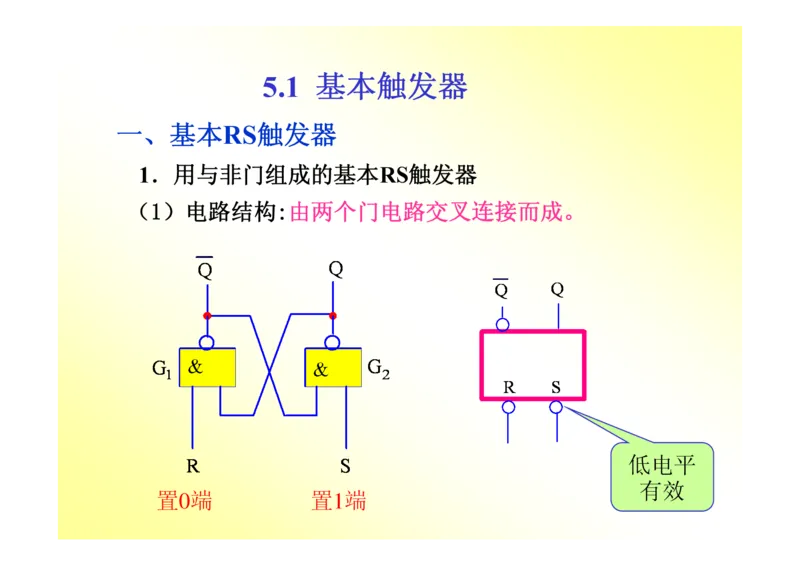

5.4 集成触发器5.1 基本触发器

一、基本RS触发器

1.用与非门组成的基本RS触发器

(1)电路结构:由两个门电路交叉连接而成。

低电平

有效

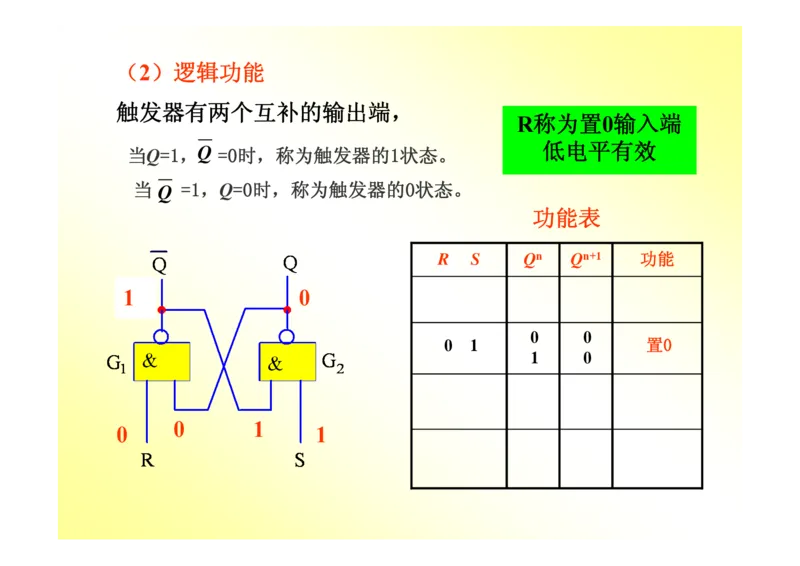

置0端 置1端(2)逻辑功能

触发器有两个互补的输出端,

R称为置0输入端

低电平有效

当Q=1,Q =0时,称为触发器的1状态。

当

Q

=1,Q=0时,称为触发器的0状态。

功能表

R S Qn Qn+1 功能

11 0

0 0

0 1 置0

1 0

0 1

0 1(2)逻辑功能

触发器有两个互补的输出端,

S称为置1输入端

低电平有效

当Q=1,Q =0时,称为触发器的1状态。

当

Q

=1,Q=0时,称为触发器的0状态。

功能表

R S Qn Qn+1 功能

0 11

0 0

0 1 置0

1 0

0 1

1 0 置1

1 1

1 0

1 0(2)逻辑功能

触发器有两个互补的输出端,

当Q=1,Q =0时,称为触发器的1状态。

当

Q

=1,Q=0时,称为触发器的0状态。

功能表

R S Qn Qn+1 功能

11 00

0 0

0 1 置0

1 0

0 1

1 0 置1

1 1

0 1

1 1

0 0

1 1 保持

1 1(2)逻辑功能

触发器有两个互补的输出端,

当Q=1,Q =0时,称为触发器的1状态。

当

Q

=1,Q=0时,称为触发器的0状态。

功能表

R S Qn Qn+1 功能

1 1 0 0 0 ×

不定

1 ×

0 0

0 1 置0

1 0

0 1

1 0 置1

1 1

1 1 1

0 10

0 0

1 1 保持

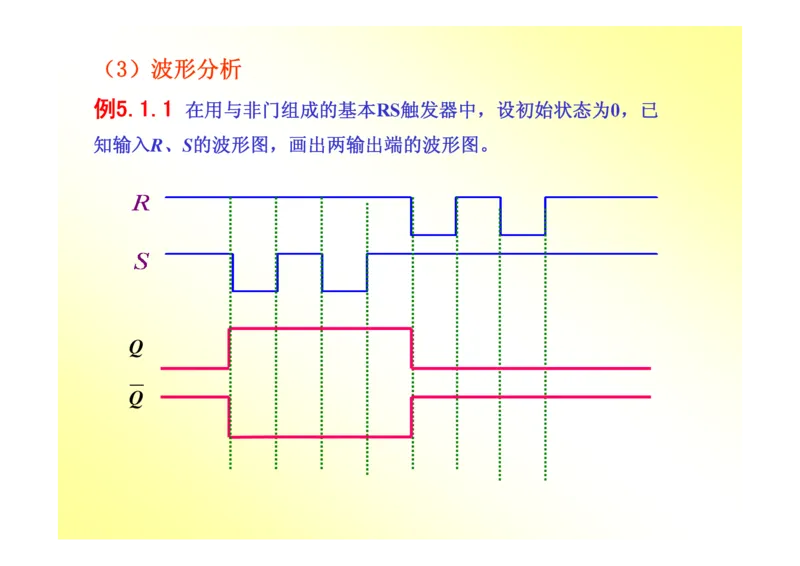

1 1(3)波形分析

例5.1.1

在用与非门组成的基本RS触发器中,设初始状态为0,已

知输入R、S的波形图,画出两输出端的波形图。

Q

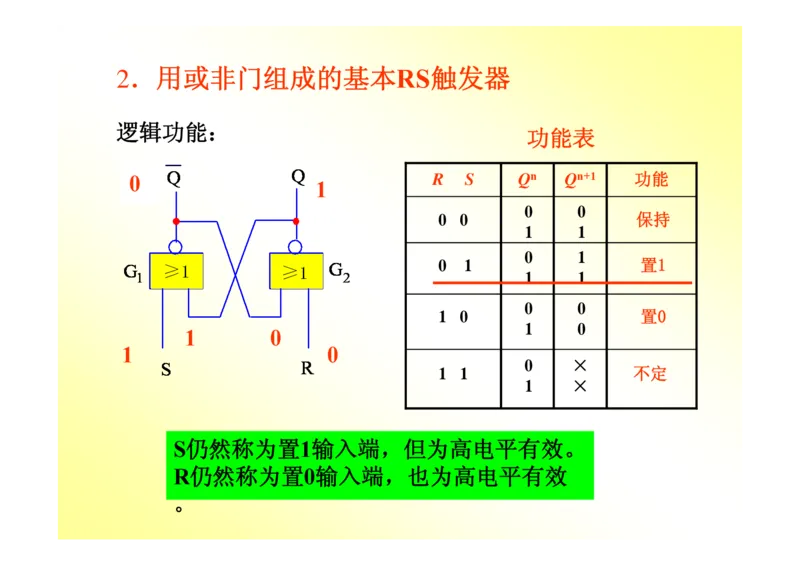

Q2.用或非门组成的基本RS触发器

逻辑功能:

功能表

00 R S Qn Qn+1 功能

1

0 0

0 0 保持

1 1

0 1

0 1 置1

1 1

0 0

1 0 置0

1 0

1 0

1 0

0 ×

1 1 不定

1 ×

S仍然称为置1输入端,但为高电平有效。

R仍然称为置0输入端,也为高电平有效

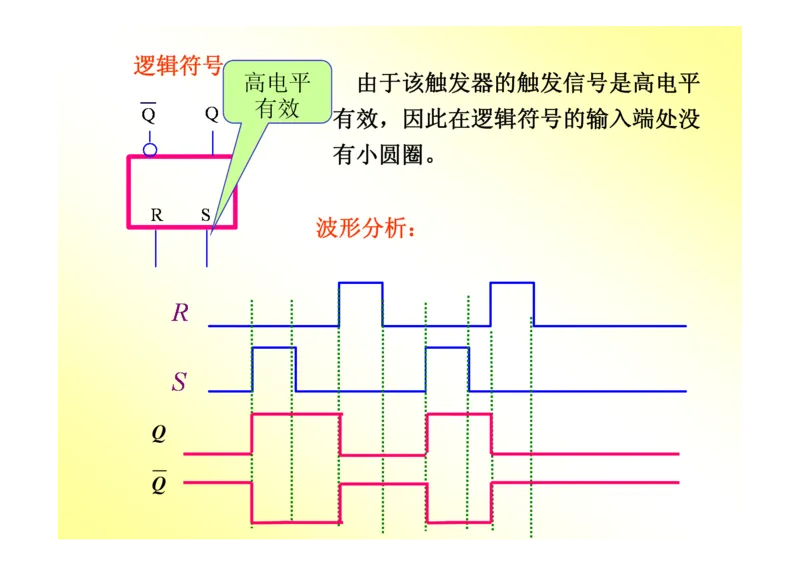

。逻辑符号:

高电平 由于该触发器的触发信号是高电平

有效

有效,因此在逻辑符号的输入端处没

有小圆圈。

波形分析:

Q

Q基本触发器的特点总结:

(1)有两个互补的输出端,有两个稳定的状态。

(2)有复位(Q=0)、置位(Q=1)、保持原状态三

种功能。

(3)R为复位输入端,S为置位输入端,可以是低电

平有效,也可以是高电平有效,取决于触发器的结

构。

(4)由于反馈线的存在,无论是复位还是置位,有

效信号只需要作用很短的一段时间,即“一触即

发”。二、 同步RS触发器

给触发器加一个时钟控制端CP,只有在CP端上出现时钟脉冲时,

触发器的状态才能改变。这种触发器称为同步触发器。

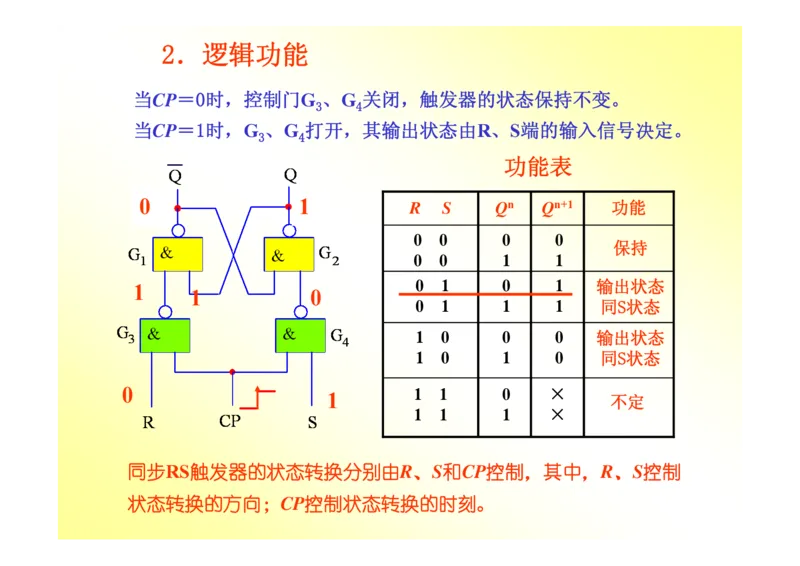

1.同步RS触发器的电路结构2.逻辑功能

当CP=0时,控制门G 、G 关闭,触发器的状态保持不变。

3 4

当CP=1时,G 、G 打开,其输出状态由R、S端的输入信号决定。

3 4

功能表

01 01 R S Qn Qn+1 功能

0 0 0 0

保持

0 0 1 1

0 1 0 1 输出状态

1

1 0

0 1 1 1 同S状态

1 0 0 0 输出状态

1 0 1 0 同S状态

0 1 1 0 ×

1

不定

1 1 1 ×

同步RS触发器的状态转换分别由R、S和CP控制,其中,R、S控制

状态转换的方向;CP控制状态转换的时刻。3.触发器功能的几种表示方法

触发器的功能除了可以用功能表表示外,还有几种表示方法:

(1)特性方程

由功能表画出卡诺图得特性方程:

功能表

R S Qn Qn+1 功能

0 0 0 0

保持

0 0 1 1

0 1 0 1 输出状态

0 1 1 1 同S状态

1 0 0 0 输出状态

1 0 1 0 同S状态 n+1 n

{ Q = S + RQ

1 1 0 × (约束条件)

RS = 0

不定

1 1 1 ×(2)状态转换图

状态转换图表示触发器从一个状态变化到另一个状态或保持原

状不变时,对输入信号的要求。

功能表

R S Qn Qn+1 功能

0 0 0 0

保持

0 0 1 1

0 1 0 1 输出状态

0 1 1 1 同S状态

1 0 0 0 输出状态

1 0 1 0 同S状态

1 1 0 ×

不定

1 1 1 ×(3)驱动表

驱动表是用表格的方式表示触发器从一个状态变化到另一

个状态或保持原状态不变时,对输入信号的要求。

功能表

RS触发器的驱动表

R S Qn Qn+1 功能

0 0 0 0

保持 Qn→ Qn+1 R S

0 0 1 1

0 0 × 0

0 1 0 1 输出状态

0 1 0 1

0 1 1 1 同S状态

1 0 1 0

1 0 0 0 输出状态

1 1 0 ×

1 0 1 0 同S状态

1 1 0 ×

不定

1 1 1 ×(4)波形图

已知同步RS触发器的输入波形,画出输出波形图。

Q

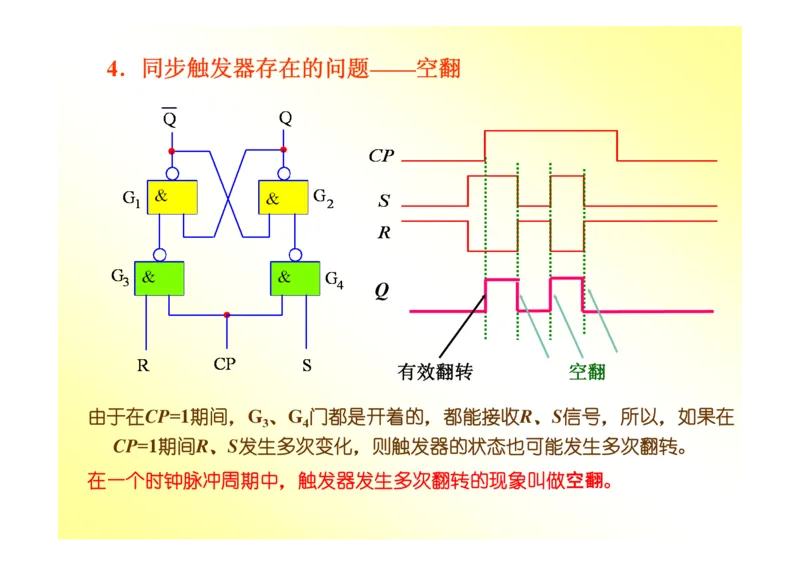

Q4.同步触发器存在的问题——空翻

Q

有效翻转 空翻

由于在CP=1期间,G 、G 门都是开着的,都能接收R、S信号,所以,如果在

3 4

CP=1期间R、S发生多次变化,则触发器的状态也可能发生多次翻转。

在一个时钟脉冲周期中,触发器发生多次翻转的现象叫做空翻。5.2 主从触发器

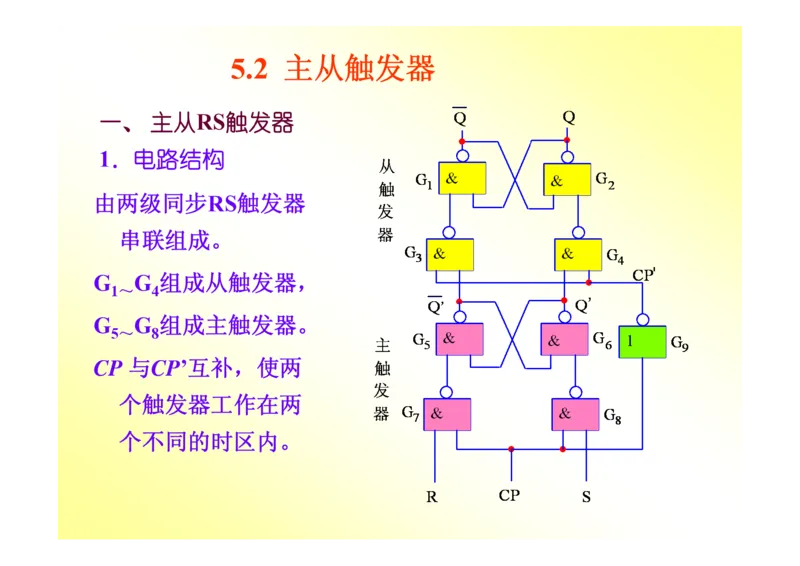

一、 主从RS触发器

1.电路结构

由两级同步RS触发器

串联组成。

G G 组成从触发器,

1~ 4

G G 组成主触发器。

5~ 8

CP 与CP’互补,使两

个触发器工作在两

个不同的时区内。主从触发器的触发翻转分为两个节拍:

2.工作原理

(1)当CP=1时,CP’ =0,”从“保持。

01 01

”主”工作,接收R和S端的输入信号。

(2)当CP 时,即CP=0、CP’ =1。

”主“保持,不再接收R、S信号;

1 1 0

”从”工作,接收主触发器输出端的状态。

功能表

1 0

0

R S Qn Qn+1 功能

0 0 0 0

保持

0 0 1 1

1 0

1

0 1 0 1 输出状态

0 1 1 1 同S状态

1 0 0 0 输出状态

1 0 1 0 同S状态

0

1 1

1 1 0 ×

不定

1 1 1 ×主从触发器的特点:

(1)主从触发器的翻转是在CP由1变0时刻(CP下

降沿)发生的。

(2)CP一旦变为0后,主触发器被封锁,其状态不

再受R、S影响,因此不会有空翻现象。

主从RS触发器的符号:二、 主从JK触发器

1.电路结构

主从RS触发器的缺点:

使用时有约束条件

RS=0

为此,将触发器

的两个互补的输出

端信号通过两根反

馈线分别引到输入

端的G 、G 门,这

7 8

样,就构成了JK触

发器。2.工作原理

1 01

0

JK触发器

1 0 功能表

1

J K Qn Qn+1 功能

0

0 0 0 0

保持

0 1

0 0 1 1

0 1 0 0 输出状态

0 1 1 0 同J状态

1 1 0 1 0 0 1 输出状态

1 0 1 1 同J状态

1 1 0 1 Qn=Qn

1 1 1 0

1

0

1

1 13.JK触发器逻辑功能的几种表示方法

(1)功能表: (2)特性方程:

JK触发器

功能表

J K Qn Qn+1 功能

0 0 0 0

保持

0 0 1 1

0 1 0 0 输出状态

0 1 1 0 同J状态

1 0 0 1 输出状态

1 0 1 1 同J状态

n+1 n n

1 1 0 1 Qn=Qn Q = JQ + KQ

1 1 1 0(3)状态转换图

JK触发器

功能表

J K Qn Qn+1 功能

0 0 0 0

保持

0 0 1 1

(4)驱动表

0 1 0 0 输出状态

0 1 1 0 同J状态

JK触发器的驱动表

1 0 0 1 输出状态

1 0 1 1 同J状态

Qn→ Qn+1 J K

1 1 0 1 Qn=Qn

0 0 0 ×

1 1 1 0

0 1 1 ×

1 0 × 1

1 1 × 0例5.2.1 已知主从JK触发器J、K的波形如图所示,画出输

出Q的波形图(设初始状态为0)。

在画主从触发器的波形图时,应注意以下两点:

(1)触发器的触发翻转发生在时钟脉冲的触发沿(这里是下降沿)

(2)判断触发器次态的依据是时钟脉冲下降沿前一瞬间输入端的状态。

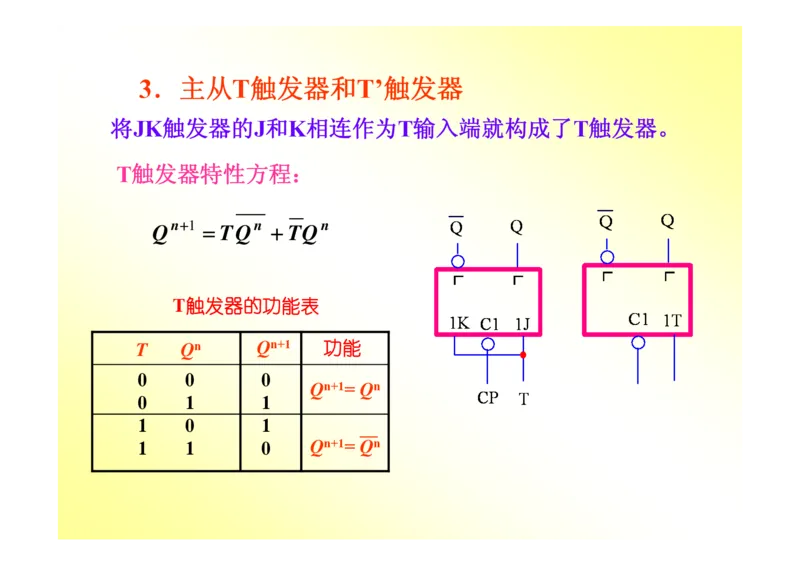

Q3.主从T触发器和T’触发器

将JK触发器的J和K相连作为T输入端就构成了T触发器。

T触发器特性方程:

n+1 n n

Q = TQ + TQ

T触发器的功能表

T Qn Qn+1 功能

0 0 0

Qn+1= Qn

0 1 1

1 0 1

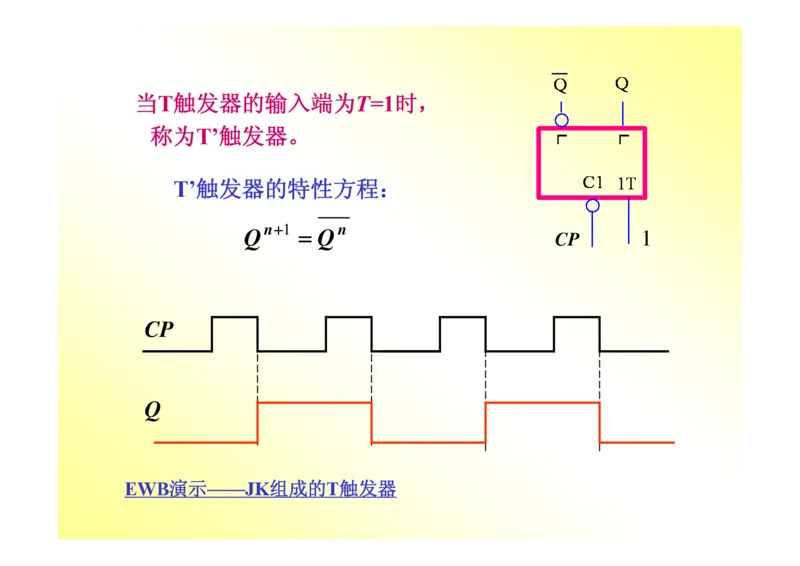

1 1 0 Qn+1= Qn当T触发器的输入端为T=1时,

称为T’触发器。

T’触发器的特性方程:

n+1 n

Q = Q 1

CP

CP

Q

EWB演示——JK组成的T触发器4.主从JK触发器存在的问题——一次变化现象

例5.2.2 已知主从JK触发器J、K的波形如图所示,画出输出Q的波形

0 1

1 0

图(设初始状态为0)。

1 0

1

01 01

Q

1 01

1

0

1 1

由此看1出,主从JK触发器100在CP=1期间,主触发器只变化(翻转)一次,

这种现象称为一次变化现象。5.3 边沿触发器

一、维持

—

阻塞边沿D触发器

1.D触发器的逻辑功能

D触发器只有一个触发输入端D,因此,逻辑关系非常简单;

D触发器的功能表

D Qn Qn+1 功能

0 0 0

0 1 0 输出状态

1 0 1 同D状态

1 1 1

D触发器的特性方程为:Qn+1=DD触发器的状态转换图:

D触发器的

功能表

D Qn Qn+1 功能

0 0 0

0 1 0 输出状

1 0 1

态同D

状态

1 1 1

D触发器的驱动表

Qn→ Qn+1 D

0 0 0

0 1 1

1 0 0

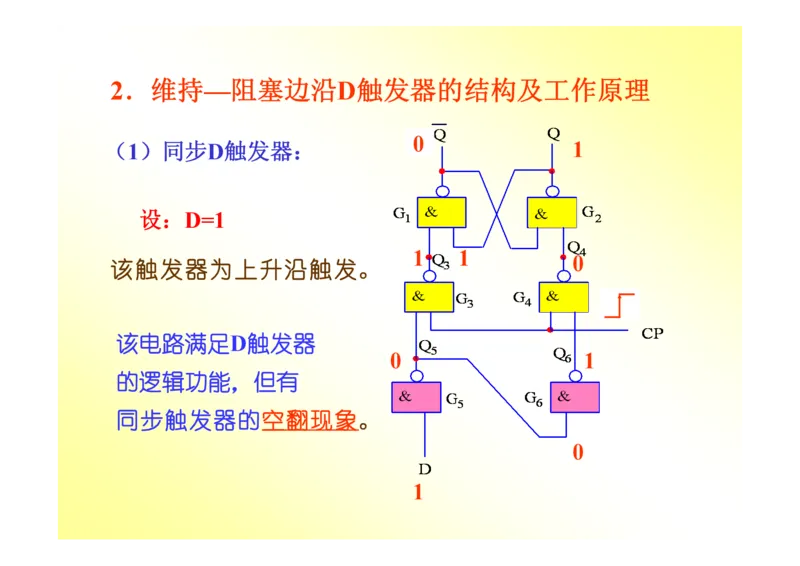

1 1 12.维持—阻塞边沿D触发器的结构及工作原理

0

(1)同步D触发器: 1

设:D=1

1 1

0

该触发器为上升沿触发。

该电路满足D触发器

0 1

的逻辑功能,但有

同步触发器的空翻现象 。

0

1(2)维持—阻塞边沿D触发器

为了克服空翻,在

0

1

原电路的基础上引入

三根反馈线。

1 1 0

①置1。

设:D=1 0

1 0 11

L 称为置1维持线。

1

L 称为置0阻塞线。

2

0

0

1

01(2)维持—阻塞边沿D触发器

②置0。

0

1

设:D=0

L 称为置0维持线。

3

1

0 1

可见,引入了维持线和阻

塞线后,将触发器的触发

1

0

翻转控制在CP上跳沿到

1

0

来的一瞬间,并接收CP

上跳沿到来前一瞬间的D

0

信号。

1 1

10例5.3.1 已知维持—阻塞D触发器的输入波形,

画出输出波形图。

解:在波形图时,应注意以下两点:

(1)触发器的触发翻转发生在CP的上升沿。

(2)判断触发器次态的依据是CP上升沿前一瞬间输入端D的状态。

QR ——直接置0端,低电平有效;

(3)触发器的直接置0和置1端

D

S ——直接置1端;低电平有效。

D

R 和S 不受CP和D信号的

D D

影响,具有最高的优先级。

R S Qn+1

D D

00 不定

010

101

11 弃权

Q Q

C1

R 1D ∧ S

R S

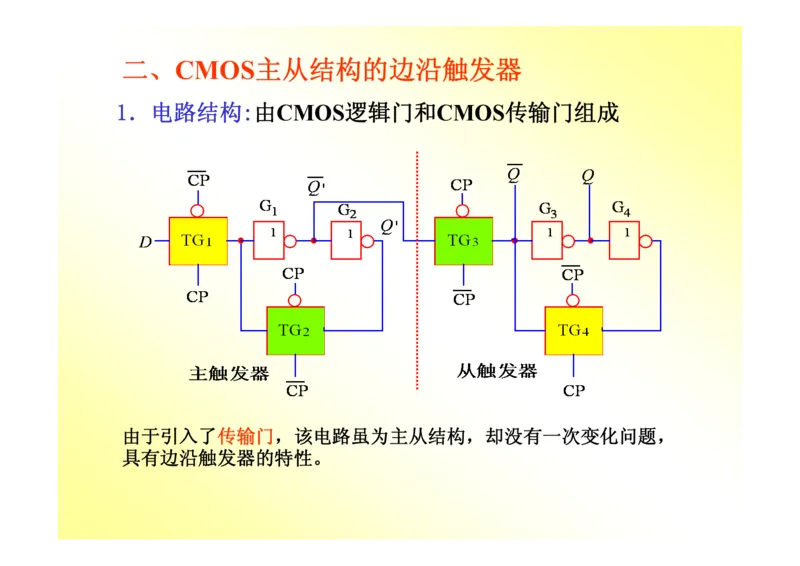

D D二、CMOS主从结构的边沿触发器

1.电路结构:由CMOS逻辑门和CMOS传输门组成

由于引入了传输门,该电路虽为主从结构,却没有一次变化问题,

具有边沿触发器的特性。2.工作原理

触发器的触发翻转分为两个节拍:

(1)当CP变为1时,TG 开通,TG 关闭。主触发器接收D信号。

1 2

同时,TG 关闭,TG 开通,从触发器保持原状态不变。

3 4

(2)当CP由1变为0时,TG 关闭,TG 开通,主触发器自保持。

1 2

同时,TG 开通,TG 关闭,从触发器接收主触发器的状态。

3 4

设:D=1(原状态Q=0) 0

1 1

0

0

1

0

1

1

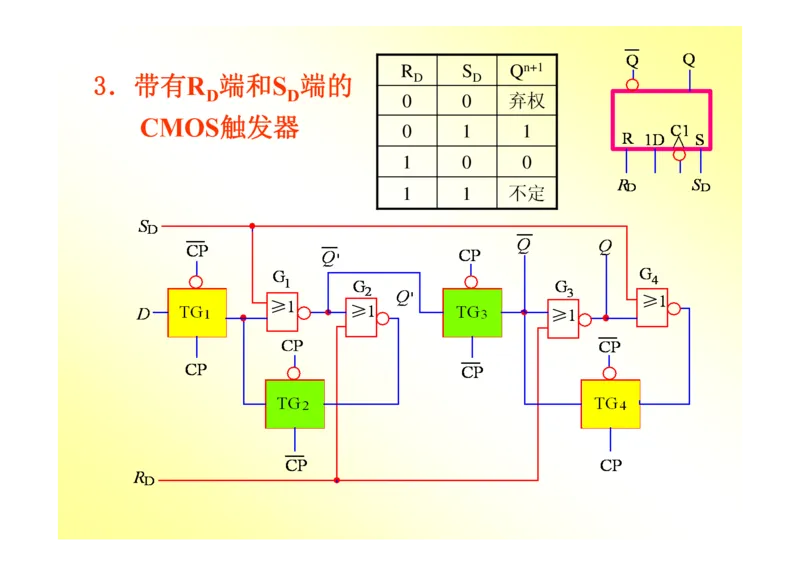

1R S Qn+1

3.带有R 端和S 端的 D D

D D

00 弃权

CMOS触发器

011

100

11 不定5.4 集成触发器

一、集成触发器举例

1.TTL主从JK触发器74LS72

特点:(1)有3个J端和3个K端,它们之间是与逻辑关系。

(2)带有直接置0端R 和直接置1端S ,都为低电平有效,不用时应接高电平。

D D

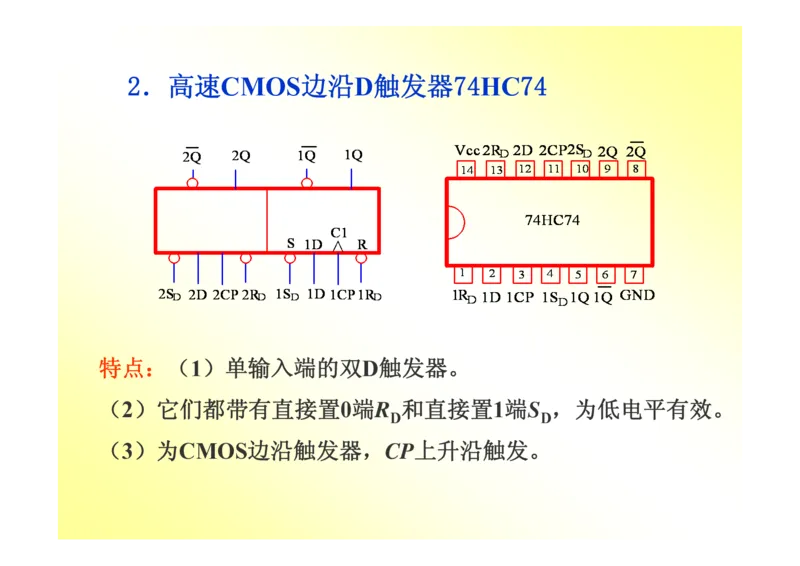

(3)为主从型结构,CP下跳沿触发。2.高速CMOS边沿D触发器74HC74

特点:(1)单输入端的双D触发器。

(2)它们都带有直接置0端R 和直接置1端S ,为低电平有效。

D D

(3)为CMOS边沿触发器,CP上升沿触发。二、触发器功能的转换

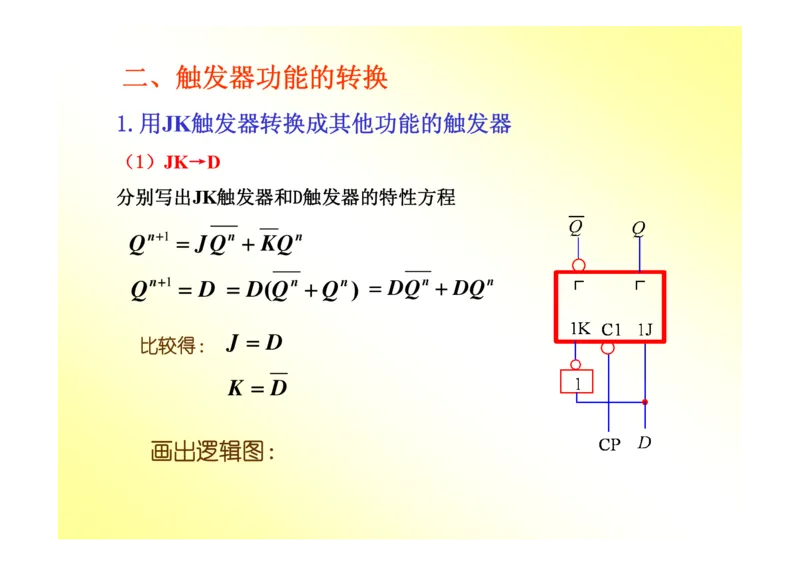

1.用JK触发器转换成其他功能的触发器

(1)JK→D

分别写出JK触发器和D触发器的特性方程

Qn+1 = JQn + KQn

Qn+1 = D = D(Qn + Qn ) = DQn + DQn

J = D

比较得:

K = D

画出逻辑图:(2)JK→T(T’ )

写出JK触发器和T触发器的特性方程:

Qn+1 = JQn + KQn

Qn+1

=

TQn

+

TQn

令T=1,即可得T’ 触发器。

比较得:J=T,K=T。2.用D触发器转换成其他功能的触发器

(1)D→JK

写出D触发器和JK触发

器的特性方程:

Qn+1 = D

Qn+1 = JQn + KQn

比较得:

D = JQn + KQn

画出逻辑图。(2)D→T

(3)D→T’三、触发器应用举例

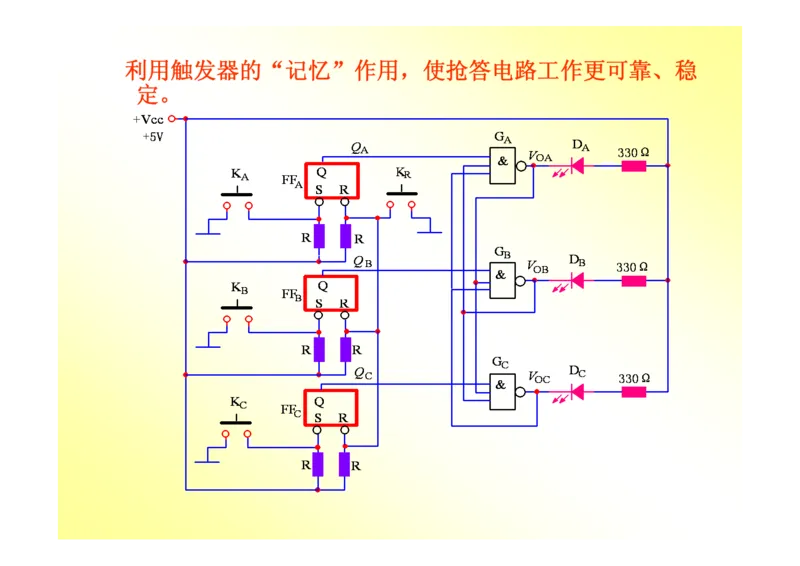

例5.4.1 设计一个3人抢答电路。3人A、B、C各控制一个按键开关

K 、K 、K 和一个发光二极管D 、D 、D 。谁先按下开关,谁的

A B C A B C

发光二极管亮,同时使其他人的抢答信号无效。利用触发器的“记忆”作用,使抢答电路工作更可靠、稳

定。本章小结

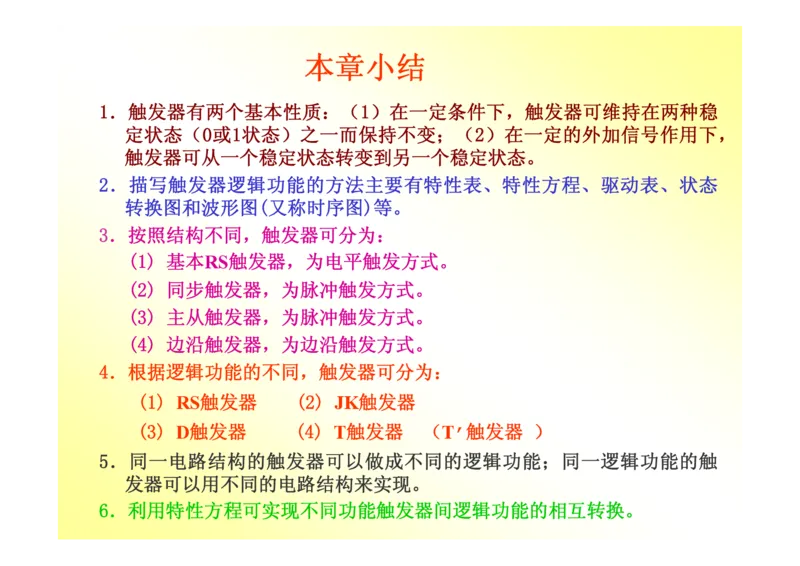

1.触发器有两个基本性质:(1)在一定条件下,触发器可维持在两种稳

定状态(0或1状态)之一而保持不变;(2)在一定的外加信号作用下,

触发器可从一个稳定状态转变到另一个稳定状态。

2.描写触发器逻辑功能的方法主要有特性表、特性方程、驱动表、状态

转换图和波形图(又称时序图)等。

3.按照结构不同,触发器可分为:

(1) 基本RS触发器,为电平触发方式。

(2) 同步触发器,为脉冲触发方式。

(3) 主从触发器,为脉冲触发方式。

(4) 边沿触发器,为边沿触发方式。

4.根据逻辑功能的不同,触发器可分为:

(1) RS触发器 (2) JK触发器

(3) D触发器 (4) T触发器 (T’ 触发器 )

5.同一电路结构的触发器可以做成不同的逻辑功能;同一逻辑功能的触

发器可以用不同的电路结构来实现。

6.利用特性方程可实现不同功能触发器间逻辑功能的相互转换。5.6 设主从JK触发器的初始状态为0,CP、J、K信号如图

题5.6所示,试画出触发器Q端的波形。

5.7 设维持—阻塞D触发器的初始状态为0,CP、D信号如图

题5.7所示,试画出触发器Q端的波形。5.8 电路如图所示,设各触发器的初态为0,画出

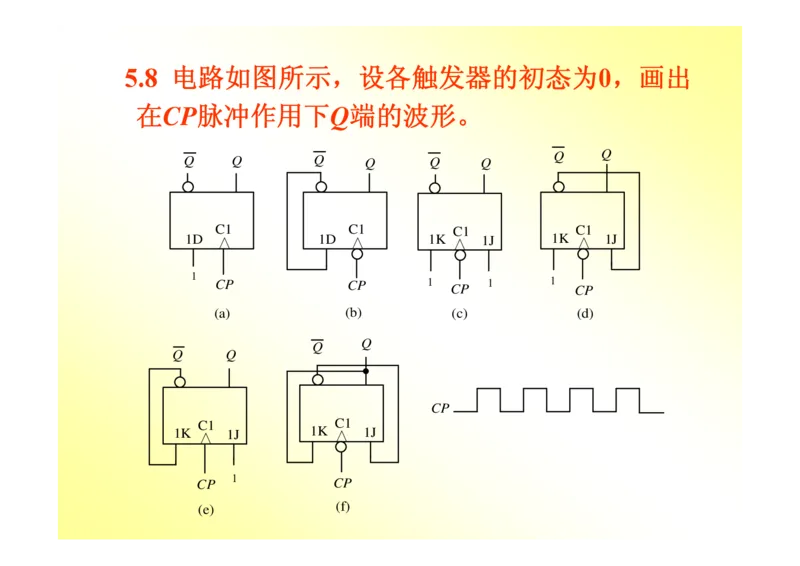

在CP脉冲作用下Q端的波形。

Q Q

Q Q Q Q Q Q

C1 C1 C1 C1

1D ∧ 1D ∧ 1K ∧ 1J 1K ∧ 1J

1

CP CP 1 1 1

CP CP

(a) (b) (c) (d)

Q

Q

Q Q

CP

C1 C1

1K ∧ 1J 1K ∧ 1J

1

CP CP

(f)

(e)5.12 电路如图所示,已知CP和X的波形,试画出

Q 和Q 的波形。设触发器的初始状态均为0。

0 1

Q Q

1 0

=1 X

1J 1J 1

C1 C1

1K 1K 1

CP

∧ ∧

CP

X5.13 电路如图所示,已知CP、R 和D的波形,试画

D

出Q 和Q 的波形。设触发器的初始状态均为1。

0 1

1J

C1

1K

∧

S

1D

C1

R

∧

Q Q

1 0

S D=1

S

CP D

1 R D

R

D

R

D

CP第六章 时序逻辑电路

6.1 时序逻辑电路的基本概念

6.2 时序逻辑电路的一般分析方法

6.3 计数器

6.4 数码寄存器与移位寄存器

6.5 时序逻辑电路的设计方法6.1 时序逻辑电路的基本概念

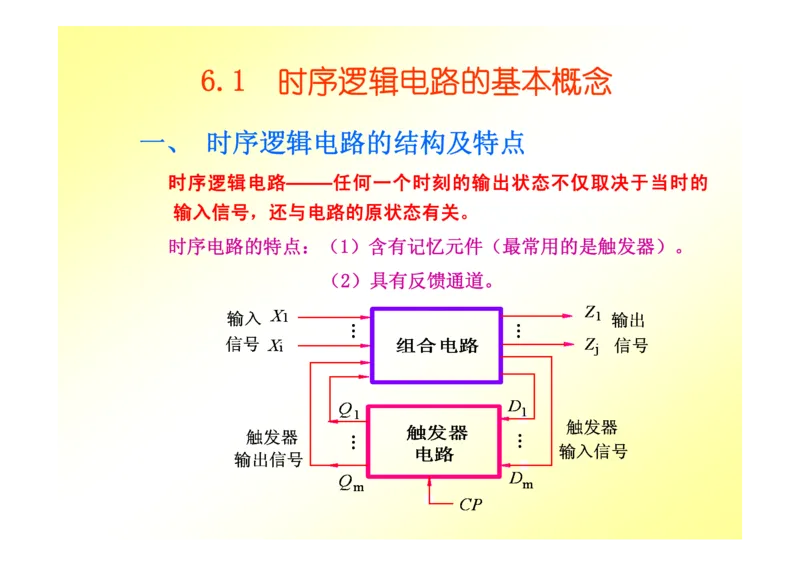

一、 时序逻辑电路的结构及特点

时序逻辑电路 任何一个时刻的输出状态不仅取决于当时的

————

输入信号,还与电路的原状态有关。

时序电路的特点:(1)含有记忆元件(最常用的是触发器)。

(2)具有反馈通道。6.2 时序逻辑电路的一般分析方法

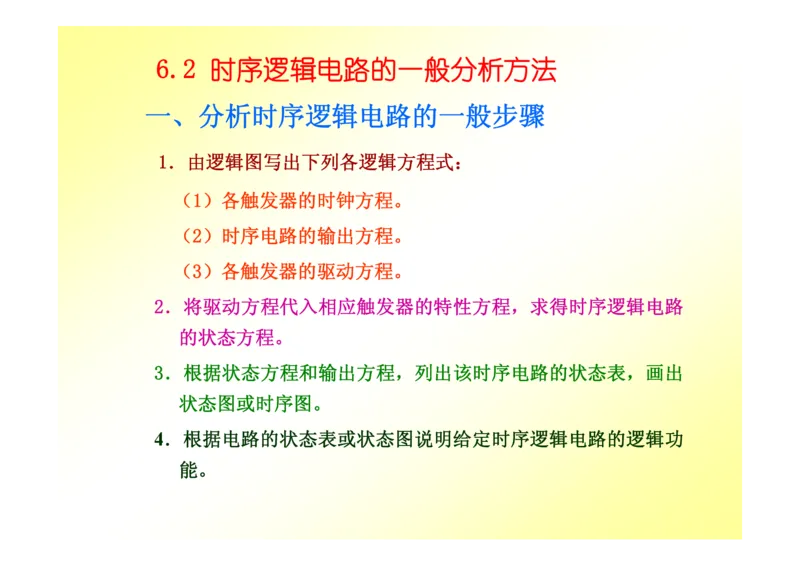

一、分析时序逻辑电路的一般步骤

1.由逻辑图写出下列各逻辑方程式:

(1)各触发器的时钟方程。

(2)时序电路的输出方程。

(3)各触发器的驱动方程。

2.将驱动方程代入相应触发器的特性方程,求得时序逻辑电路

的状态方程。

3.根据状态方程和输出方程,列出该时序电路的状态表,画出

状态图或时序图。

4.根据电路的状态表或状态图说明给定时序逻辑电路的逻辑功

能。二、同步时序逻辑电路的分析举例

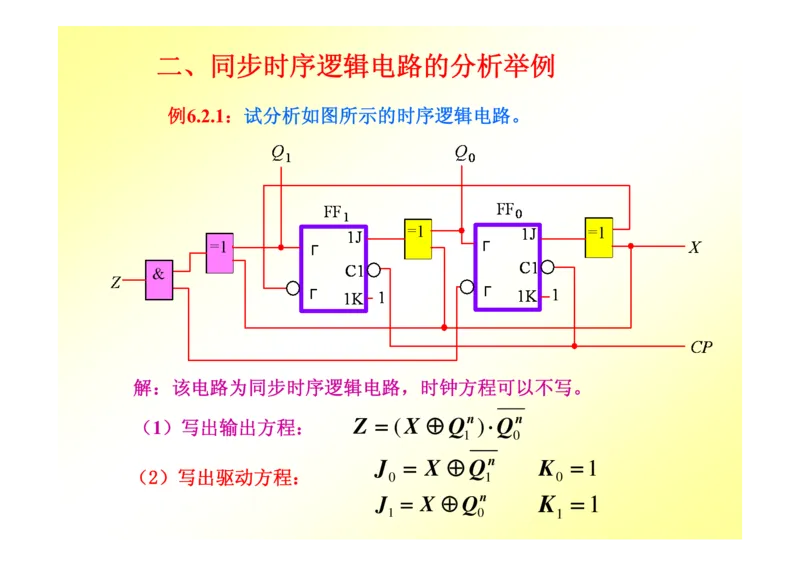

例6.2.1:试分析如图所示的时序逻辑电路。

解:该电路为同步时序逻辑电路,时钟方程可以不写。

(1)写出输出方程: Z = (X ⊕ Qn)⋅ Qn

1 0

J = X ⊕ Qn K = 1

(2)写出驱动方程:

0 1 0

J = X ⊕ Qn K = 1

1 0 1(3)写出JK触发器的特性方程,然后将各驱动方程代入JK触发器的

特性方程,得各触发器的次态方程:

Q n+1 = J Qn + K Qn = (X ⊕ Qn)Qn

0 0 0 0 0 1 0

Q n+1 = J Q n + K Qn = (X ⊕ Qn)⋅Qn

1 1 1 1 1 0 1

(4 J )作 = 状 X 态 ⊕ 转 Q 换n表及状 K 态图 =1 J = X ⊕Q n K = 1

0 1 0 1 0 1

Q n+1 = QnQn

①当X=0时:触发器的次态方程简化为:

0 1 0

Qn+1 = QnQn

输出方程简化为: Z = QnQn

1 0 1

1 0

Z = (X ⊕ Qn)⋅ Qn

作出X=0的状态表:

1 0

现 态 次 态 输 出

Q n Q n Q n+1 Q n+1 Z

1 0 1 0

0 0 0 1 0

0 1 1 0 0

1 0 0 0 1各触发器的次态方程: Q n+1 = J Qn + K Qn = (X ⊕ Qn)Qn

0 0 0 0 0 1 0

Q n+1 = J Q n + K Qn = (X ⊕ Qn)⋅Qn

1 1 1 1 1 0 1

②当X=1时:触发器的次态方程简化为:

Q n+1 = QnQn Qn+1 = QnQn

0 1 0 1 0 1

输出方程简化为: Z = QnQn Z = (X ⊕ Qn)⋅ Qn

1 0 1 0

作出X=1的状态表:

现 态 次 态 输 出

Q n Q n Q n+1 Q n+1 Z

1 0 1 0

0 0 1 0 1

1 0 0 1 0

0 1 0 0 0

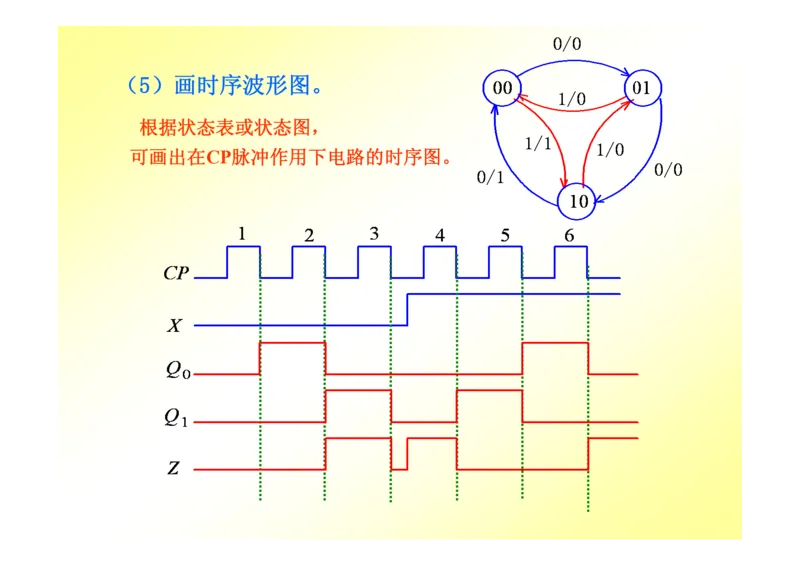

将X=0与X=1的状态图合并起来得完整的状态图。(5)画时序波形图。

根据状态表或状态图,

可画出在CP脉冲作用下电路的时序图。(6)逻辑功能分析:

该电路一共有3个状态00、01、10。

当X=0时,按照加1规律从00→01→10→00循环变化,

并每当转换为10状态(最大数)时,输出Z=1。

当X=1时,按照减1规律

从10→01→00→10循环变化,

并每当转换为00状态(最小数)时,

输出Z=1。

所以该电路是一个可控的

3进制计数器。三、异步时序逻辑电路的分析举例

例6.2.2:试分析如图所示的时序逻辑电路

该电路为异步时序逻辑电路。具体分析如下:

(1)写出各逻辑方程式。

①时钟方程:

)

CP =CP (时钟脉冲源的上升沿触发。

0

CP =Q (当FF 的Q 由0→1时,Q 才可能改变状态。)

1 0 0 0 1①时钟方程: CP =CP CP =Q

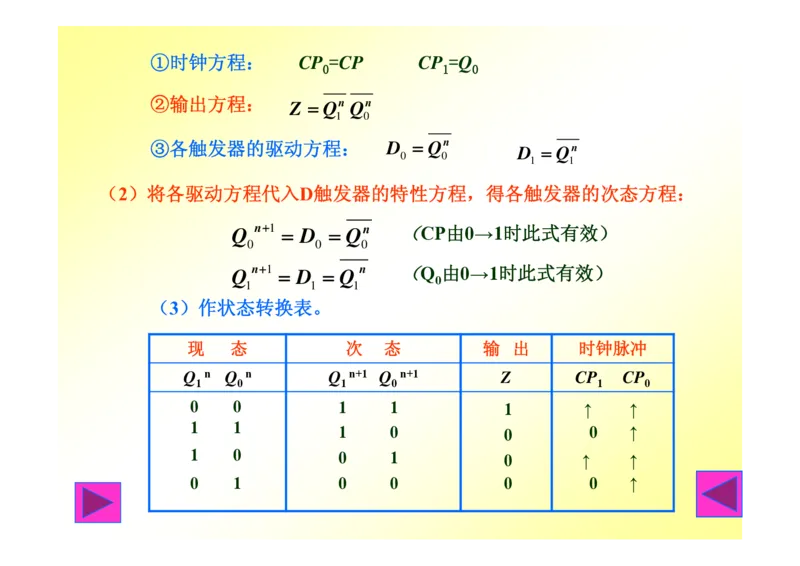

0 1 0

②输出方程: Z = Qn Qn

1 0

③各触发器的驱动方程: D = Qn

D = Qn

0 0

1 1

(2)将各驱动方程代入D触发器的特性方程,得各触发器的次态方程:

Q n+1 = D = Qn (CP由0→1时此式有效)

0 0 0

Q

n+1

= D = Q

n (Q 由0→1时此式有效)

0

1 1 1

(3)作状态转换表。

现 态 次 态 输 出 时钟脉冲

Q n Q n Q n+1 Q n+1 ZCP CP

1 0 1 0 1 0

0 0 1 1 1 ↑ ↑

1 1

1 0 0 0 ↑

1 0 0 1

0 ↑ ↑

0 1 0 0 0 0 ↑(4)作状态转换图、时序图。 (5)逻辑功能分析

该电路一共有4个状态00、01、10、

11,在CP作用下,按照减1规律循

环变化,所以是一个4进制减法计

数器,Z是借位信号。6.3 计数器

计数器 用以统计输入脉冲CP个数的电路。

——

计数器的分类:

(1)按计数进制可分为二进制计数器和非二进

制计数器。

非二进制计数器中最典型的是十进制计数器。

(2)按数字的增减趋势可分为加法计数器、减

法计数器和可逆计数器。

(3)按计数器中触发器翻转是否与计数脉冲同

步分为同步计数器和异步计数器。一、二进制计数器

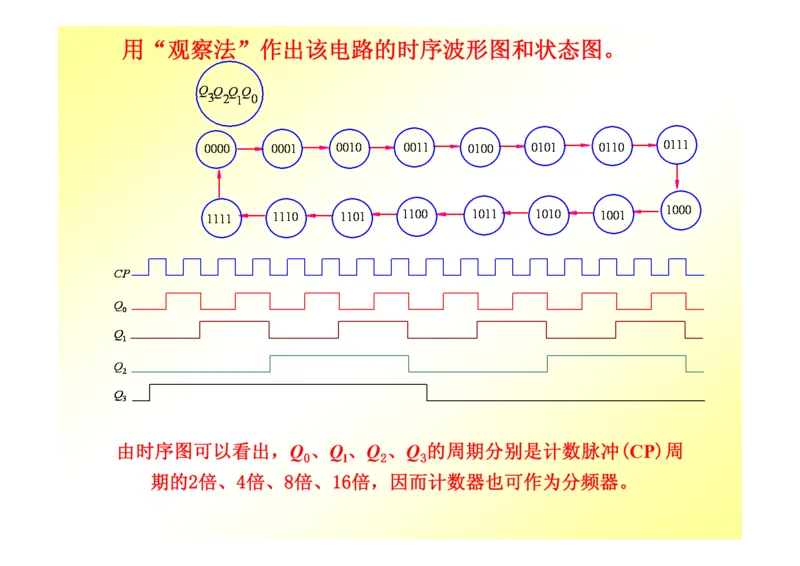

1.二进制异步计数器

(1)二进制异步加法计数器(4位)

工作原理: 4个JK触发器都接成T’ 触发器。

每来一个CP的下降沿时,FF 向相反的状态翻转一次;

0

每当Q 由1变0,FF 向相反的状态翻转一次;

0 1

每当Q 由1变0,FF 向相反的状态翻转一次;

1 2

每当Q 由1变0,FF 向相反的状态翻转一次。

2 3用“观察法”作出该电路的时序波形图和状态图。

由时序图可以看出,Q 、Q 、Q 、Q 的周期分别是计数脉冲(CP)周

0 l 2 3

期的2倍、4倍、8倍、16倍,因而计数器也可作为分频器。(2)二进制异步减法计数器

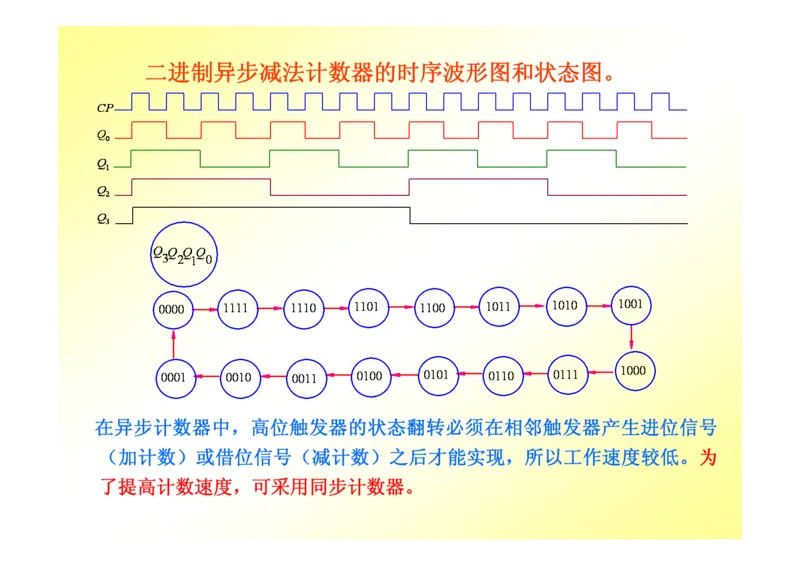

用4个上升沿触发的D触发器组成的4位异步二进制减法计数器。

工作原理:D触发器也都接成T’ 触发器。

由于是上升沿触发,则应将低位触发器的Q端与相邻高位触发

器的时钟脉冲输入端相连,即从Q端取借位信号。

它也同样具有分频作用。二进制异步减法计数器的时序波形图和状态图。

在异步计数器中,高位触发器的状态翻转必须在相邻触发器产生进位信号

(加计数)或借位信号(减计数)之后才能实现,所以工作速度较低。为

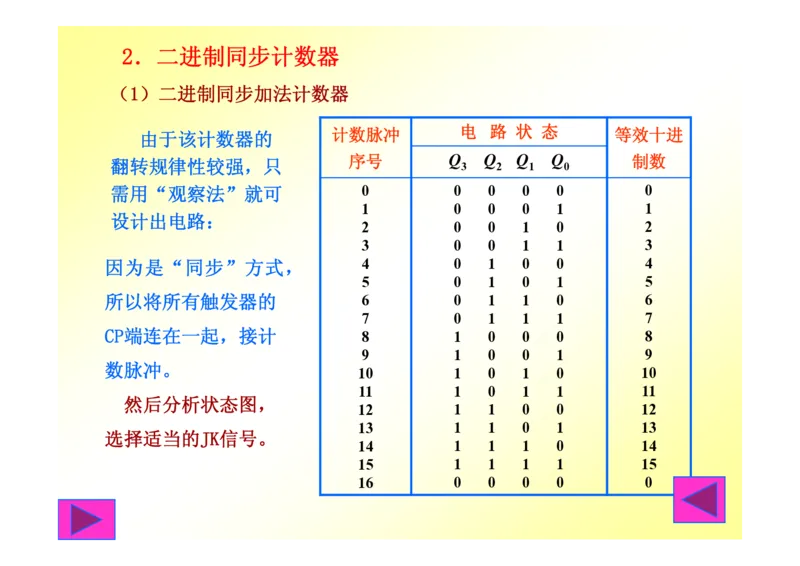

了提高计数速度,可采用同步计数器。2.二进制同步计数器

(1)二进制同步加法计数器

电 路 状 态

计数脉冲 等效十进

由于该计数器的

序号 Q Q Q Q 制数

翻转规律性较强,只

3 2 1 0

需用“观察法”就可 0 0 0 0 0 0

1 0 0 0 1 1

设计出电路:

2 0 0 1 0 2

3 0 0 1 1 3

因为是“同步”方式, 4 0 1 0 0 4

5 0 1 0 1 5

所以将所有触发器的 6 0 1 1 0 6

7 0 1 1 1 7

CP端连在一起,接计

8 1 0 0 0 8

9 1 0 0 1 9

数脉冲。

10 1 0 1 0 10

11 1 0 1 1 11

然后分析状态图,

12 1 1 0 0 12

13 1 1 0 1 13

选择适当的JK信号。

14 1 1 1 0 14

15 1 1 1 1 15

16 0 0 0 0 0分析状态图可见:

FF :每来一个CP,向相反的状态翻转一次。所以选:J =K =1

0 0 0

FF :当Q =1时,来一个CP,向相反的状态翻转一次。

1 0

所以选:J =K = Q

1 1 0

FF :当Q Q =1时, 来一个CP,向相反的状态翻转一次。

2 0 1

所以选:J =K = Q Q

2 2 0 1

FF : 当Q Q Q =1时, 来一个CP,向相反的状态翻转一次。

3 0 1 2

所以选:J =K = Q Q Q

3 3 0 1 2(2)二进制同步减法计数器

分析4位二进制同步减法计数器的状态表,很容易看出,只要将各

触发器的驱动方程改为:

J = K = 1

J = K = Q

0 0

1 1 0

J = K = Q Q J = K = Q Q Q

2 2 0 1 3 3 0 1 2

就构成了4位二进制同步减法计数器。

(3)二进制同步可逆计数器

将加法计数器和减法计数器合并起来,并引入一加/减控制信号X便构

成4位二进制同步可逆计数器,各触发器的驱动方程为:

J = K = 1

0 0

J = K = XQ + X Q

1 1 0 0

J = K = XQ Q + X Q Q

2 2 0 1 0 1

J = K = XQ Q Q + X Q Q Q

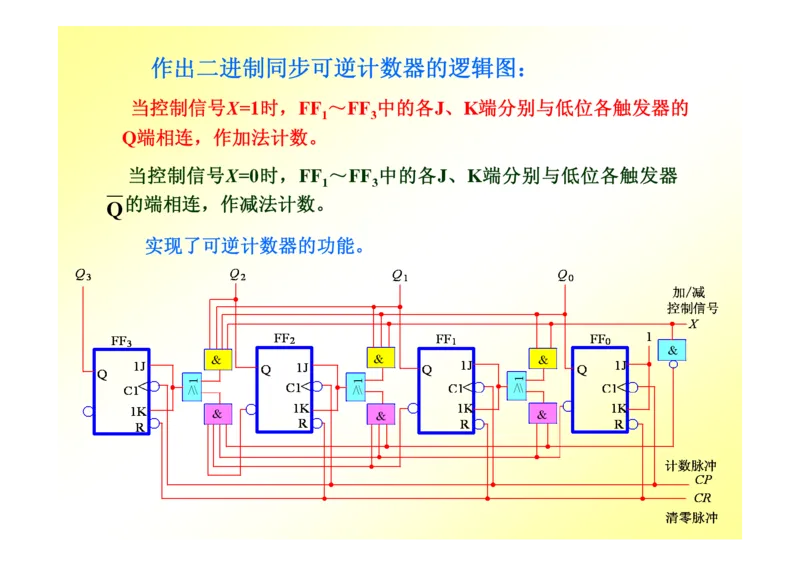

3 3 0 1 2 0 1 2作出二进制同步可逆计数器的逻辑图:

当控制信号X=1时,FF ~FF 中的各J、K端分别与低位各触发器的

1 3

Q端相连,作加法计数。

当控制信号X=0时,FF ~FF 中的各J、K端分别与低位各触发器

1 3

的端相连,作减法计数。

Q

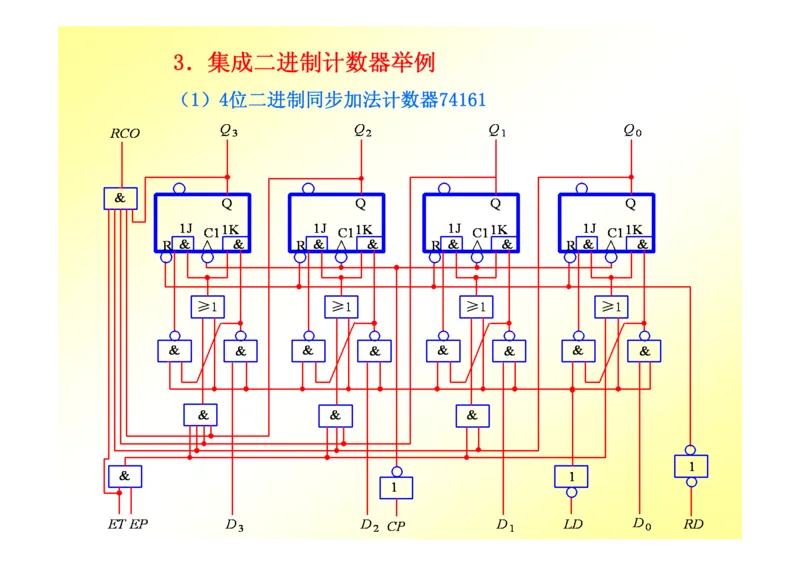

实现了可逆计数器的功能。3.集成二进制计数器举例

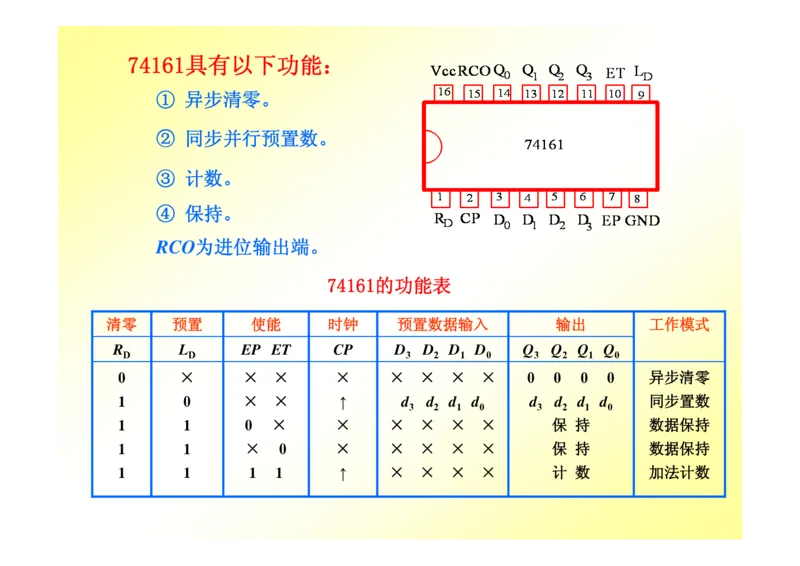

(1)4位二进制同步加法计数器7416174161具有以下功能:

① 异步清零。

② 同步并行预置数。

③ 计数。

④ 保持。

RCO为进位输出端。

74161的功能表

清零 预置 使能 时钟 预置数据输入 输出 工作模式

R L EP ET CP D D D D Q Q Q Q

D D 3 2 1 0 3 2 1 0

0 × × × × × × × × 0 0 0 0 异步清零

1 0 × × ↑ d d d d d d d d 同步置数

3 2 1 0 3 2 1 0

1 1 0 × × × × × × 保 持 数据保持

1 1 × 0 × × × × × 保 持 数据保持

1 1 1 1 ↑ × × × × 计 数 加法计数(2)4位二进制同步可逆计数器74191

74191的功能表

预置 使能 加/减控制 时钟 预置数据输入 输 出 工作模式

L EN D/ U CP D D D D Q Q Q Q

D 3 2 1 0 3 2 1 0

0 × × × d d d d d d d d 异步置数

3 2 1 0 3 2 1 0

1 1 × × × × × × 保 持 数据保持

1 0 0 ↑ × × × × 计 数 加法计数

1 0 1 ↑ × × × × 计 数 减法计数二、非二进制计数器

N进制计数器又称模N计数器。

当N=2n时,就是前面讨论的n位二进制计数器;

当N≠2n时,为非二进制计数器。非二进制计数

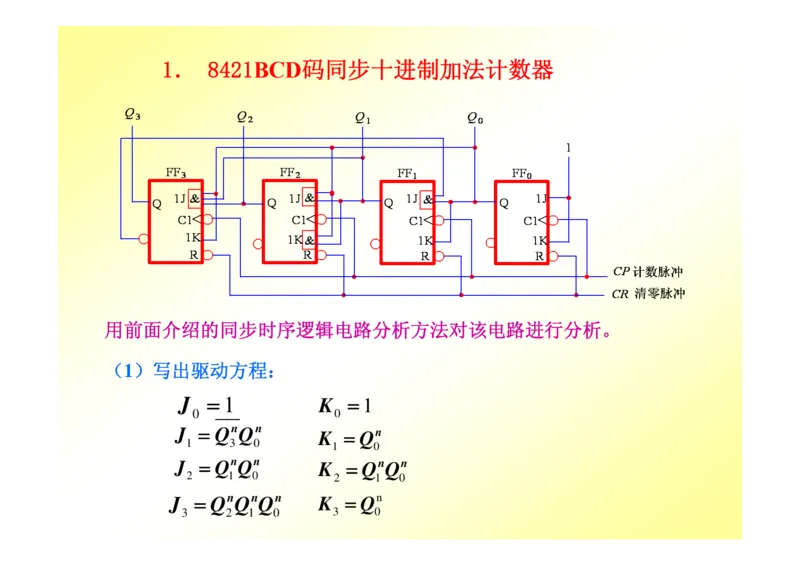

器中最常用的是十进制计数器。1. 8421BCD码同步十进制加法计数器

用前面介绍的同步时序逻辑电路分析方法对该电路进行分析。

(1)写出驱动方程:

J = 1 K = 1

0 0

J = QnQn K = Qn

1 3 0

1 0

J = QnQn K = QnQn

2 1 0 2 1 0

J = QnQnQn K = Qn

3 2 1 0 3 0J = 1 K = 1

0 0

J = QnQn K = Qn

1 3 0 1 0

J = QnQn K = QnQn

2 1 0 2 1 0

J = QnQnQn K = Qn

3 2 1 0 3 0

(2)转换成次态方程:

先写出JK触发器的特性方程 Qn+1 = JQn + KQn

然后将各驱动方程代入JK触发器的特性方程,得各触发器的次态方程:

Q n+1 = J Qn + K Qn = Qn

0 0 0 0 0 0

Q n+1 = J Q n + K Qn = QnQnQn + QnQn

1 1 1 1 1 3 0 1 0 1

Q n+1 = J Qn + K Qn = QnQnQn + QnQnQn

2 2 2 2 2 1 0 2 1 0 2

Q n+1 = J Qn + K Qn = QnQnQnQn + QnQn

3 3 3 3 3 2 1 0 3 0 3Q n+1 = Qn Q n+1 = QnQnQn + QnQn

0 0 1 3 0 1 0 1

Q n+1 = QnQnQn + QnQnQn Q n+1 = QnQnQnQn + QnQn

2 1 0 2 1 0 2 3 2 1 0 3 0 3

(3)作状态转换表。

设初态为Q Q Q Q =0000,代入次态方程进行计算,得状态转换表。

3 2 1 0

现 态 次 态

Q n Q n Q n Q n Q n+1 Q n+1Q n+1Q n+1

3 2 1 0 3 2 1 0

0 0 0 0 0 0 0 1

0 0 0 1 0 0 1 0

0 0 1 0 0 0 1 1

0 0 1 1 0 1 0 0

0 1 0 0 0 1 0 1

0 1 0 1 0 1 1 0

0 1 1 0 0 1 1 1

0 1 1 1 1 0 0 0

1 0 0 0 1 0 0 1

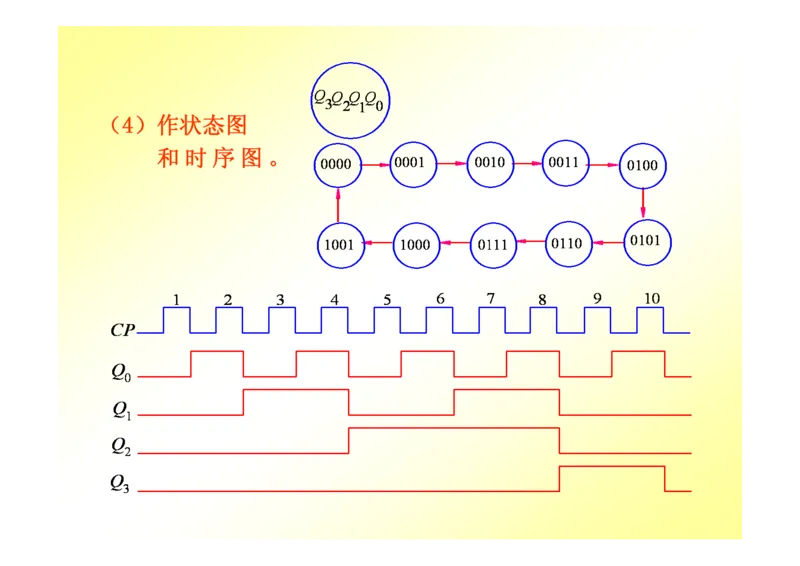

1 0 0 1 0 0 0 0(4)作状态图

和 时 序 图 。(5)检查电路能否自启动

由于电路中有4个触发器,它们的状态组合共有16种。而在8421BCD码

计数器中只用了10种,称为有效状态。其余6种状态称为无效状态。

Q n+1 = Qn Q n+1 = QnQnQn + QnQn

当由于某种原因,使计数器进入无效状态时,如果能在时钟信号作用

0 0 1 3 0 1 0 1

下,最终

Q

进n入+1 有

= Q

效n状

Q

态nQ ,n我

+ Q

们n就

Q

称nQ 该n 电路

Q

具n有+1自

=

启

Q

动

nQ

能

nQ

力

n

。

Qn + QnQn

2 1 0 2 1 0 2 3 2 1 0 3 0 3

用同样的分析方法分别求出6种无效状态下的次态,得到完整的状态

转换图。

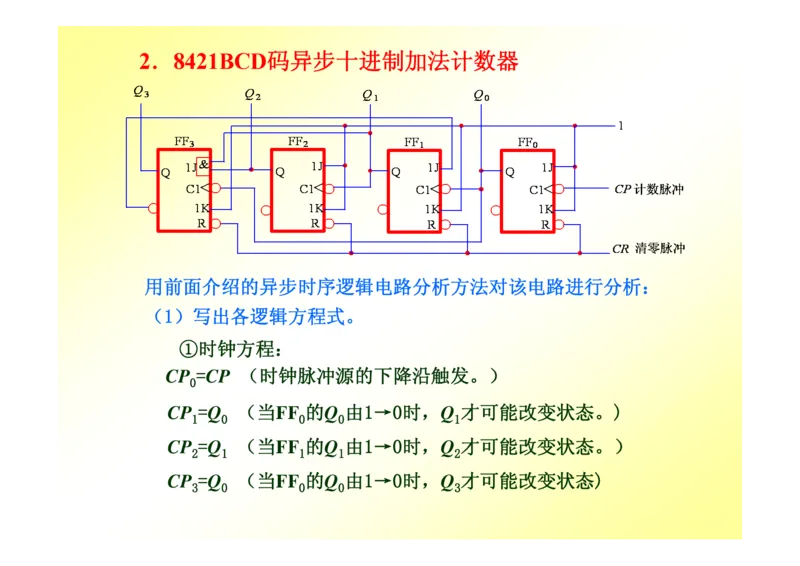

可见,该计数器能够自启动。2.8421BCD码异步十进制加法计数器

用前面介绍的异步时序逻辑电路分析方法对该电路进行分析:

(1)写出各逻辑方程式。

①时钟方程:

CP =CP (时钟脉冲源的下降沿触发。)

0

CP =Q (当FF 的Q 由1→0时,Q 才可能改变状态。)

1 0 0 0 1

CP =Q (当FF 的Q 由1→0时,Q 才可能改变状态。)

2 1 1 1 2

CP =Q (当FF 的Q 由1→0时,Q 才可能改变状态)

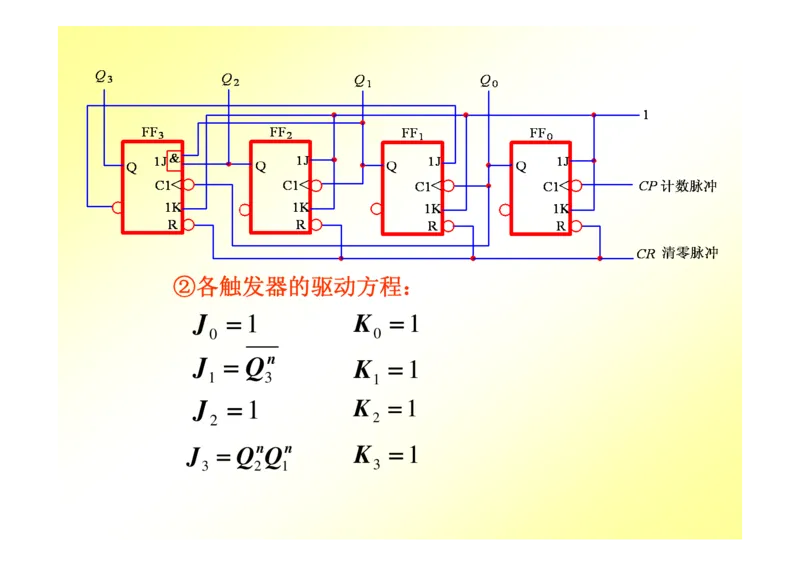

3 0 0 0 3②各触发器的驱动方程:

J = 1 K = 1

0 0

n

J = Q K = 1

1 3 1

J = 1 K = 1

2 2

J = Q n Q n K = 1

3 2 1 3J = 1

K = 1

0

0

J = Qn

K = 1

1 3

1

J = 1

K = 1

2

2

J = Q n Q n K = 1

3 2 1 3

(2)将各驱动方程代入JK触发器的特性方程,得各触发器的

次态方程:

Q n+1 = J Qn + K Qn = Qn

(CP由1→0时此式有效)

0 0 0 0 0 0

Q n+1 = J Q n + K Qn = QnQn (Q 由1→0时此式有效)

1 1 1 1 1 3 1 0

Q n+1 = J Q n + K Q n = Q n (Q 由1→0时此式有效)

2 2 2 2 2 2 1

Q n+1 = J Qn + K Qn = QnQnQn(Q 由1→0时此式有效)

0

3 3 3 3 3 2 1 3Q n+1 = Qn Q n+1 = QnQn(Q 由1→0时)

(CP由1→0时)

0 0 1 3 1 0

Q n+1 = Q n(Q 由1→0时) Q n+1 = QnQnQn (Q 由1→0时)

2 2 1 3 2 1 3 0

(3)作状态转换表。

设初态为Q Q Q Q =0000,代入次态方程进行计算,得状态转换表。

3 2 1 0

现 态 次 态 时钟脉冲

Q n Q n Q n Q Q n+1 Q n+1Q n+1Q n+1 CP CP CP CP

3 2 1 0 3 2 1 0 3 2 1 0

0 0 0 0 0 0 0 1 0 0 0 ↓

0 0 0 1 0 0 1 0 ↓ 0 ↓ ↓

0 0 1 0 0 0 1 1 0 0 0 ↓

0 0 1 1 0 1 0 0 ↓ ↓ ↓ ↓

0 1 0 0 0 1 0 1 0 0 0 ↓

0 1 0 1 0 1 1 0 ↓ 0 ↓ ↓

0 1 1 0 0 1 1 1 0 0 0 ↓

0 1 1 1 1 0 0 0 ↓ ↓ ↓ ↓

1 0 0 0 1 0 0 1 1 0 0 ↓

1 0 0 1 0 0 0 0 ↓ 0 ↓ ↓3.集成十进制计数器举例

(1)8421BCD码同步加法计数器74160

74160的功能表

清零 预置 使能 时钟 预置数据输入 输出 工作模式

R L EP ET CP D D D D Q Q Q Q

D D 3 2 1 0 3 2 1 0

0 × × × × × × × × 0 0 0 0 异步清零

1 0 × × ↑ d d d d d d d d 同步置数

3 2 1 0 3 2 1 0

1 1 0 × × × × × × 保 持 数据保持

1 1 × 0 × × × × × 保 持 数据保持

1 1 1 1 ↑ × × × × 十进制计 数 加法计数(2)二 五 十进制异步加法计数器74290

— —

74290包含一个独立的1位二进制计数器和一个独立的五进制计数器。

二进制计数器的时钟输入端为CP ,输出端为Q ;

1 0

五进制计数器的时钟输入端为CP ,输出端为Q 、Q 、Q 。

2 1 2 3

如果将Q 与CP 相连,CP 作时钟输入端,Q ~Q 作输出端,则为

0 2 1 0 3

8421BCD码十进制计数器。如果将Q 与CP 相连,CP 作时钟输入端,从高

3 0 2

位到低位的输出为Q Q Q Q 时,则构成5421BCD码十进制计数器。

0 3 2 174290的功能:

① 异步清零。

② 异步置数(置9)。

③ 计数。

复位输入 置位输入 时 钟 输 出

工作模式

R R R R CP Q Q Q Q

0(1) 0(2) 9(1) 9(2) 3 2 1 0

1 1 0 × × 0 0 0 0 异步清零

1 1 × 0 × 0 0 0 0

0 × 1 1 × 1 0 0 1 异步置数

× 0 1 1 × 1 0 0 1

0 × 0 × ↓ 计 数

0 × × 0 ↓ 计 数 加法计数

× 0 0 × ↓ 计 数

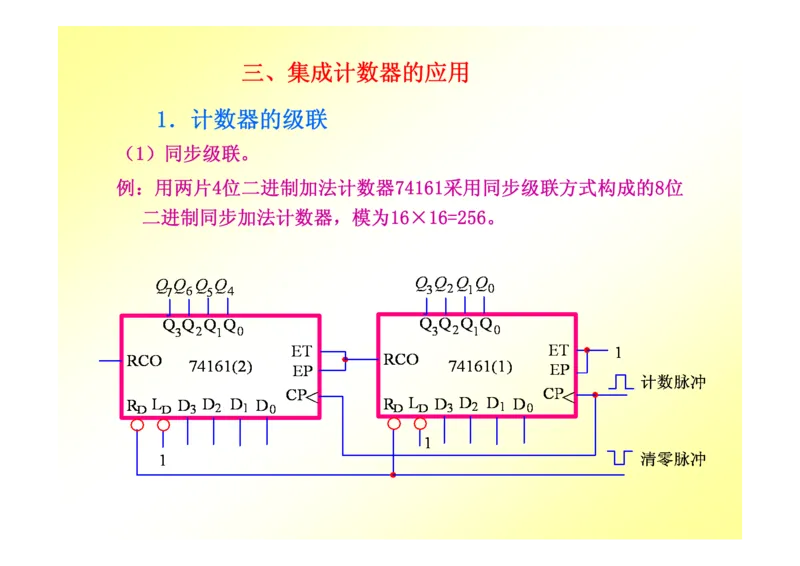

× 0 × 0 ↓ 计 数三、集成计数器的应用

1.计数器的级联

(1)同步级联。

例:用两片4位二进制加法计数器74161采用同步级联方式构成的8位

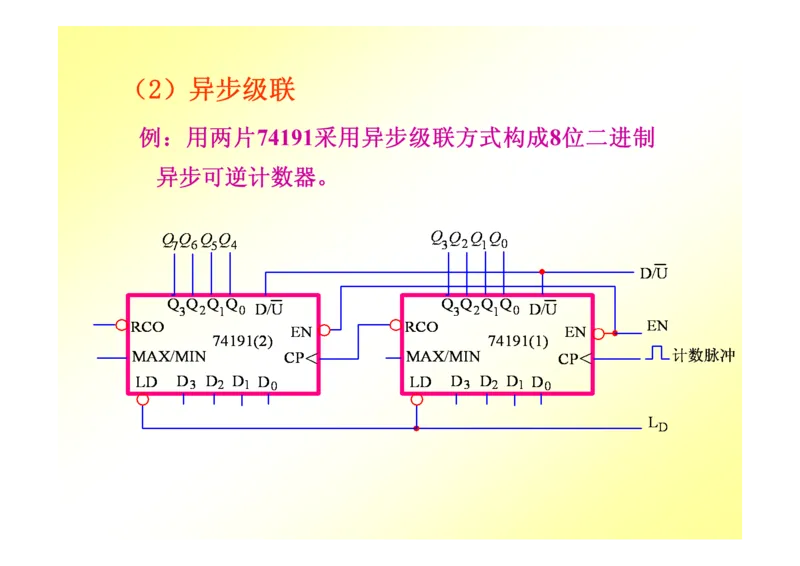

二进制同步加法计数器,模为16×16=256。(2)异步级联

例:用两片74191采用异步级联方式构成8位二进制

异步可逆计数器。(3)用计数器的输出端作进位/借位端

有的集成计数器没有进位/借位输出端,这时可根据具体情况,

用计数器的输出信号Q 、Q 、Q 、Q 产生一个进位/借位。

3 2 1 0

例:用两片74290采用异步级联方式组成的二位8421BCD码十进制

加法计数器。

模为10×10=1002.组成任意进制计数器

(1)异步清零法——适用于具有异步清零端的集成计数器。

例:用集成计数器74160和与非门组成的6进制计数器。

EWB演示——160组成6进制(2)同步清零法

同步清零法适用于具有同步清零端的集成计数器。

例:用集成计数器74163和与非门组成的6进制计数器。

EWB演示——163组成6进制(3)异步预置数法

异步预置数法适用于具有异步预置端的集成计数器。

例:用集成计数器74191和与非门组成的余3码10进制计数器。

EWB演示——191组成

余3码十进制(4)同步预置数法

同步预置数法适用于具有同步预置端的集成计数器。

例:用集成计数器74160和与非门组成的7进制计数器。

EWB演示——160组成7进制例6.3.1 用74160组成48进制计数器。

解:因为N=48,而74160为模10计数器,所以要用两片74160构成.。

先将两芯片采用同步级联方式连接成100进制计数器,

然后再用异步清零法组成了48进制计数器。3.组成分频器

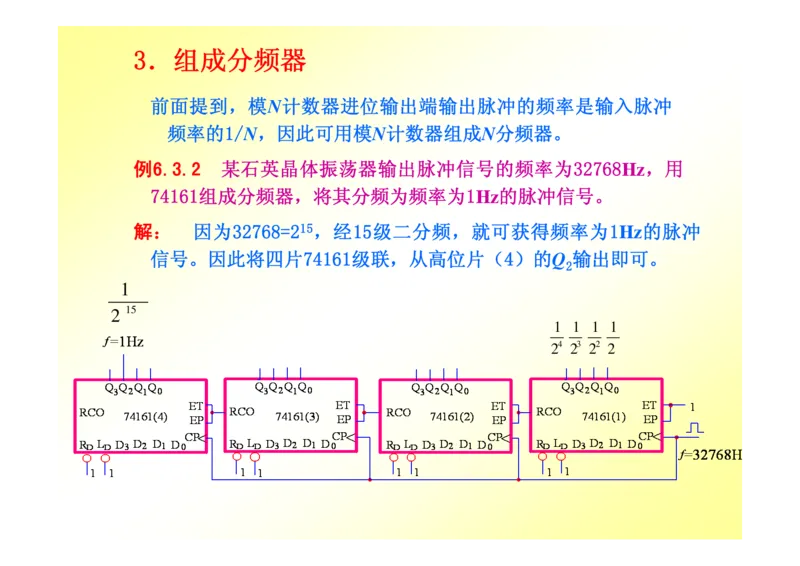

前面提到,模N计数器进位输出端输出脉冲的频率是输入脉冲

频率的1/N,因此可用模N计数器组成N分频器。

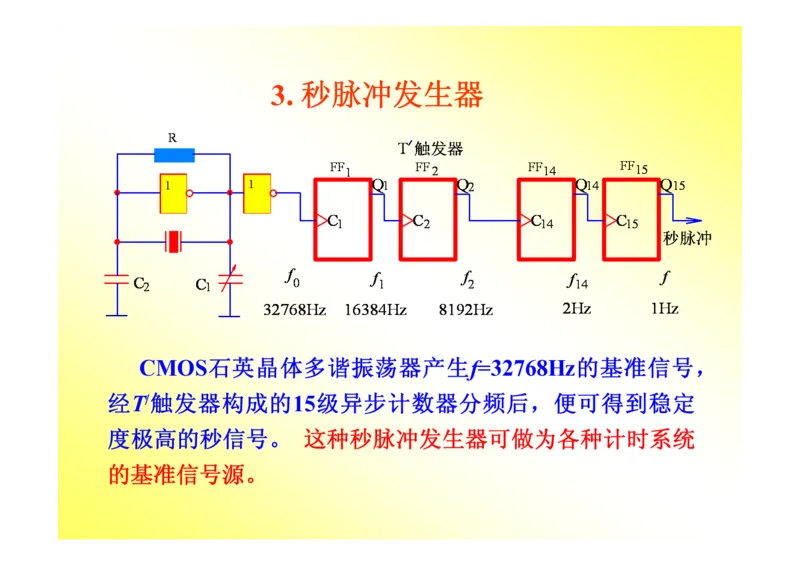

例6.3.2 某石英晶体振荡器输出脉冲信号的频率为32768Hz,用

74161组成分频器,将其分频为频率为1Hz的脉冲信号。

解: 因为32768=215,经15级二分频,就可获得频率为1Hz的脉冲

信号。因此将四片74161级联,从高位片(4)的Q 输出即可。

2

1

2 15

1 1 1 1

24 23 22 24.组成序列信号发生器

序列信号——在时钟脉冲作用下产生的一串周期性的二进制信号。

例:用74161及门电路构成序列信号发生器。

其中74161与G 构成了一个模5计数器。

1

Z = Q Q

,因此,这是一个01010序列信号发生器,序列长度P=5。

0 2

状 态 表

现 态 次 态 输出

Q n Q n Q n Q n+1 Q n+1 Q n+1 Z

2 1 0 1 1 0

0 0 0 0 0 1 0

0 0 1 0 1 0 1

0 1 0 0 1 1 0

0 1 1 1 0 0 1

1 0 0 0 0 0 0例6.3.3 试用计数器74161和数据选择器设计一个01100011

序列发生器。

解:由于序列长度P=8,故将74161构成模8计数器,并选

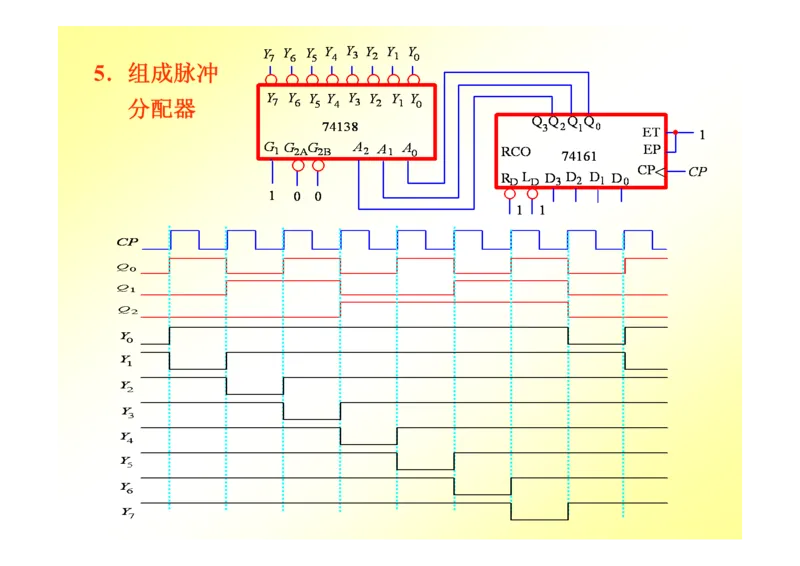

用数据选择器74151产生所需序列。5.组成脉冲

分配器6.4 数码寄存器与移位寄存器

一、 数码寄存器

数码寄存器——存储二进制数码的时序电路组件

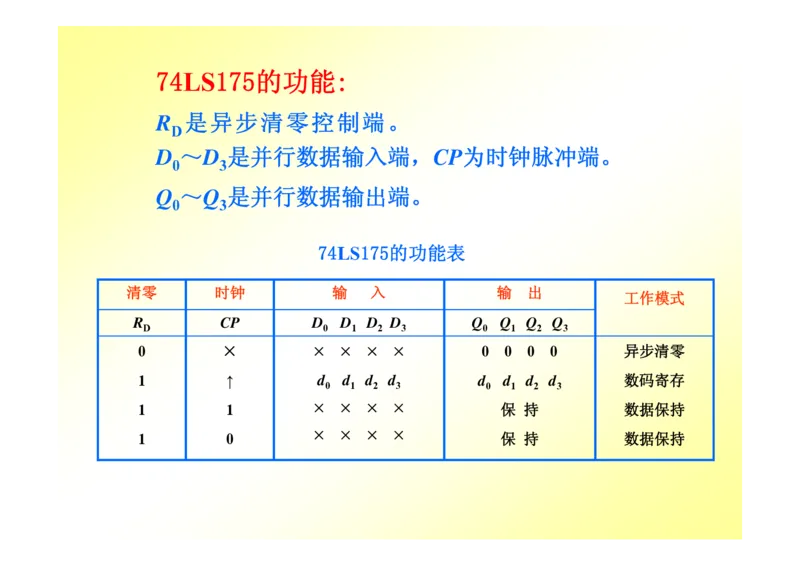

集成数码寄存器74LSl75 :74LS175的功能:

R 是异步清零控制端。

D

D ~D 是并行数据输入端,CP为时钟脉冲端。

0 3

Q ~Q 是并行数据输出端。

0 3

74LS175的功能表

清零 时钟 输 入 输 出

工作模式

R CP D D D D Q Q Q Q

D 0 1 2 3 0 1 2 3

0 × × × × × 0 0 0 0 异步清零

1 ↑ d d d d d d d d 数码寄存

0 1 2 3 0 1 2 3

1 1 × × × × 保 持 数据保持

1 0 × × × × 保 持 数据保持二、移位寄存器

移位寄存器 不但可以寄存数码,而且在移位脉冲作用

——

下,寄存器中的数码可根据需要向左或向右移动1位。

1.单向移位寄存器

(1)右移寄存器(D触发器组成的4位右移寄存器)

右移寄存器的结构特点:左边触发器的输出端接右邻触发器的输入端。设移位寄存器的初始状态为0000,串行输入数码D =1101,从高

I

位到低位依次输入。其状态表如下:

移位脉冲 输入数码 输 出

CP D Q Q Q Q

I 0 1 2 3

0 0 0 0 0

1 1 1 0 0 0

2 1 1 1 0 0

3 0 0 1 1 0

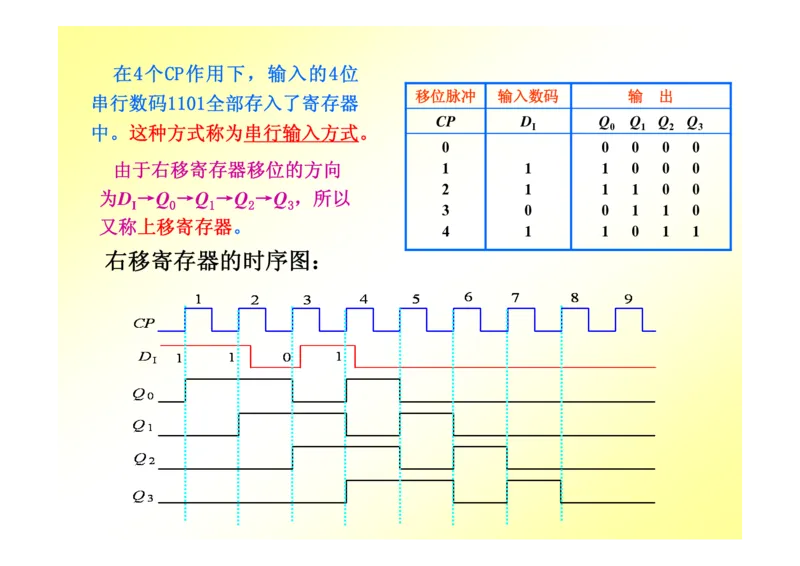

4 1 1 0 1 1在4个CP作用下,输入的4位

移位脉冲 输入数码 输 出

串行数码1101全部存入了寄存器

CP D Q Q Q Q

中。这种方式称为串行输入方式。 I 0 1 2 3

0 0 0 0 0

由于右移寄存器移位的方向 1 1 1 0 0 0

2 1 1 1 0 0

为D →Q →Q →Q →Q ,所以

I 0 1 2 3

3 0 0 1 1 0

又称上移寄存器。

4 1 1 0 1 1

右移寄存器的时序图:(2)左移寄存器

左移寄存器的结构特点:右边触发器的输出端接左邻触发器的输入端。

2 .双向移位寄存器

将右移寄存器和左移寄存器组合起来,并引入一控制端S便构成

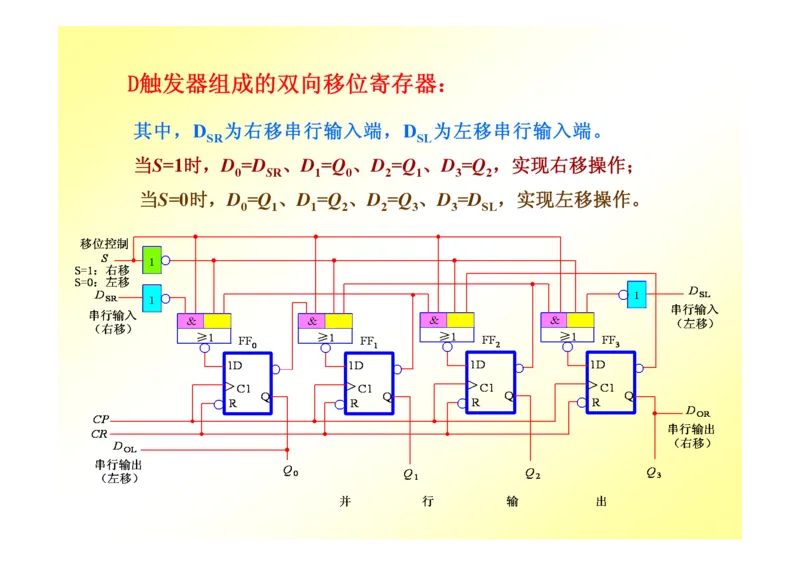

既可左移又可右移的双向移位寄存器。D触发器组成的双向移位寄存器:

其中,D 为右移串行输入端,D 为左移串行输入端。

SR SL

当S=1时,D =D 、D =Q 、D =Q 、D =Q ,实现右移操作;

0 SR 1 0 2 1 3 2

当S=0时,D =Q 、D =Q 、D =Q 、D =D ,实现左移操作。

0 1 1 2 2 3 3 SL三、集成移位寄存器74194

74194为四位双向移位寄存器。

D 和D 分别是左移和右移串行输入。D 、D 、D 和D 是并行输

SL SR 0 1 2 3

入端。

Q 和Q 分别是左移和右移时的串行输出端,Q 、Q 、Q 和Q 为

0 3 0 1 2 3

并行输出端。74194的功能表

输 入 输 出

清零 控 制 串行输入 时钟 并行输入 工作模式

R S S D D CP D D D D Q Q Q Q

D 1 0 SL SR 0 1 2 3 0 1 2 3

0 × × × × × × × × × 0 0 0 0 异步清零

10 0 × × × × × × × Q n Q n Q n Q n 保 持

0 1 2 3

1 0 1 × 1 ↑ × × × × 1 Q n Q n Q n 右 移

0 1 2

1 0 1 × 0 ↑ × × × × 0 Q n Q n Q n

0 1 2

1 1 0 1 × ↑ × × × × Q n Q n Q n 1 左 移

1 2 3

1 1 0 0 × ↑ × × × × Q n Q n Q n 0

1 2 3

11 1 × × ↑ D D D D D D D D 并行置数

0 1 2 3 0 1 2 3四、移位寄存器构成的移位型计数器

1. 环形计数器

环形计数器的特点:

电路简单,N位移位寄存器可以计N个数,实现模N计数器。状态为1

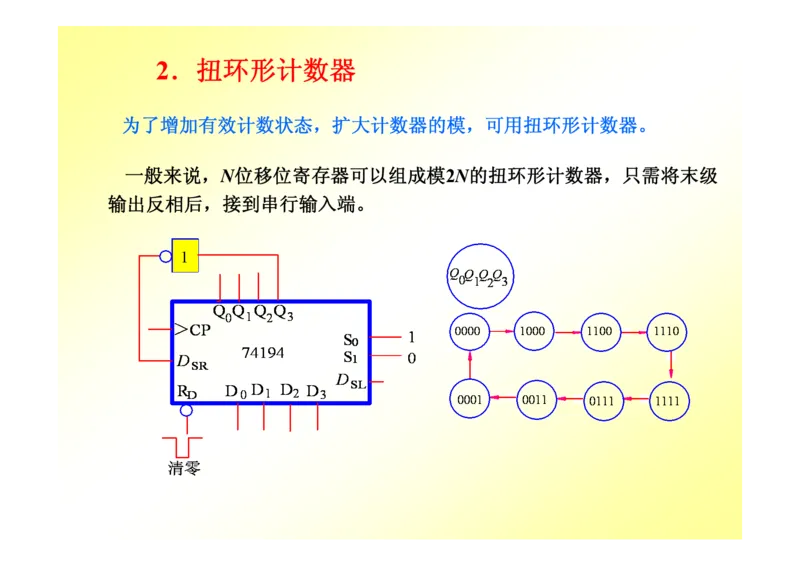

的输出端的序号等于计数脉冲的个数,通常不需要译码电路。2.扭环形计数器

为了增加有效计数状态,扩大计数器的模,可用扭环形计数器。

一般来说,N位移位寄存器可以组成模2N的扭环形计数器,只需将末级

输出反相后,接到串行输入端。6.5 时序逻辑电路的设计方法

一、同步时序逻辑电路的设计方法

1.同步时序逻辑电路的设计步骤

(1)根据设计要求,设定状态,导出对应状态图或状态表。

(2)状态化简。消去多余的状态,得简化状态图(表)。

(3)状态分配,又称状态编码。即把一组适当的二进制代码分配给

简化状态图(表)中各个状态。

(4)选择触发器的类型。

(5)根据编码状态表以及所采用的触发器的逻辑功能,导出待设计

电路的输出方程和驱动方程。

(6)根据输出方程和驱动方程画出逻辑图。

(7)检查电路能否自启动。2.同步计数器的设计举例

例6.5.1 设计一个同步5进制加法计数

器

(1)根据设计要求,设定状态,

画出状态转换图。该状态图不须化简。

(2)状态分配,列状态转换编码表。

状态转换编码表

现 态 次 态 输 出

状态转换顺序

Q n Q n Q n Q n+1 Q n+1 Q n+1 Y

2 1 0 1 1 0

S 0 0 0 0 0 1 0

0

S 0 0 1 0 1 0 0

1

S 0 1 0 0 1 1 0

2

S 0 1 1 1 0 0 0

3

S 1 0 0 0 0 0 1

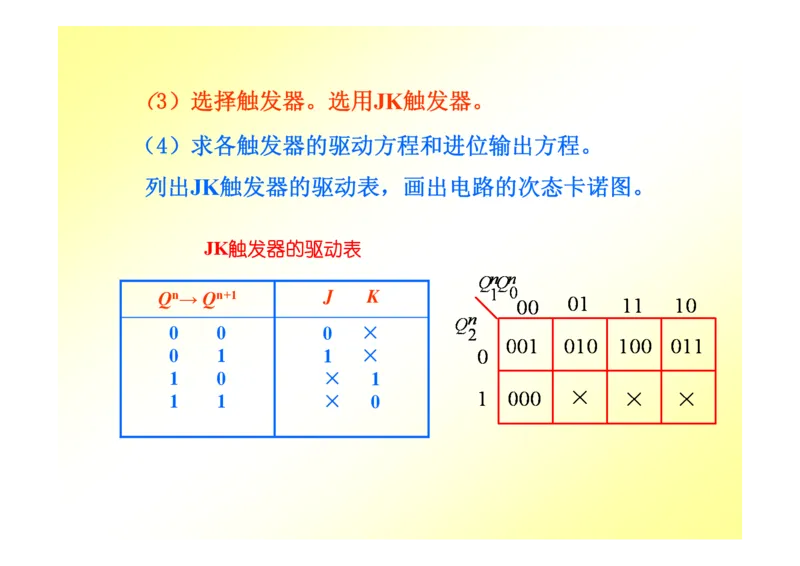

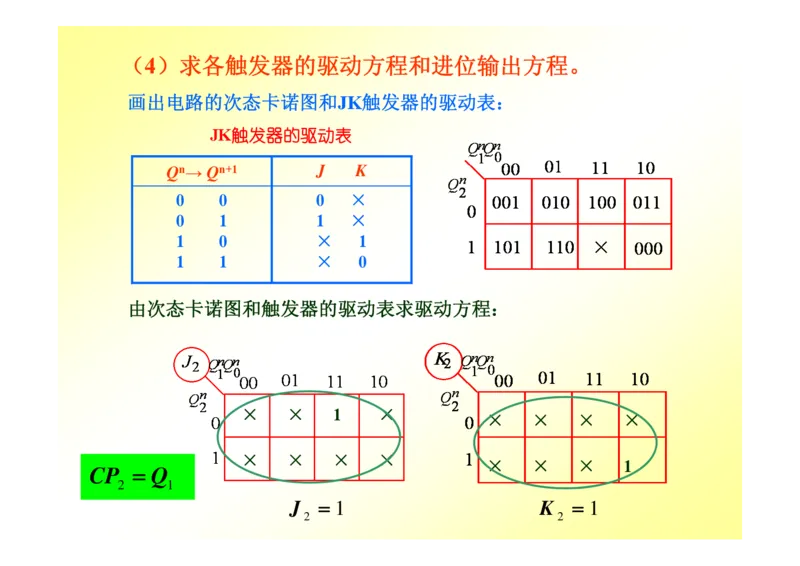

4(3)选择触发器。选用JK触发器。

(4)求各触发器的驱动方程和进位输出方程。

列出JK触发器的驱动表,画出电路的次态卡诺图。

JK触发器的驱动表

Qn→ Qn+1 J K

0 0 0 ×

0 1 1 ×

1 0 × 1

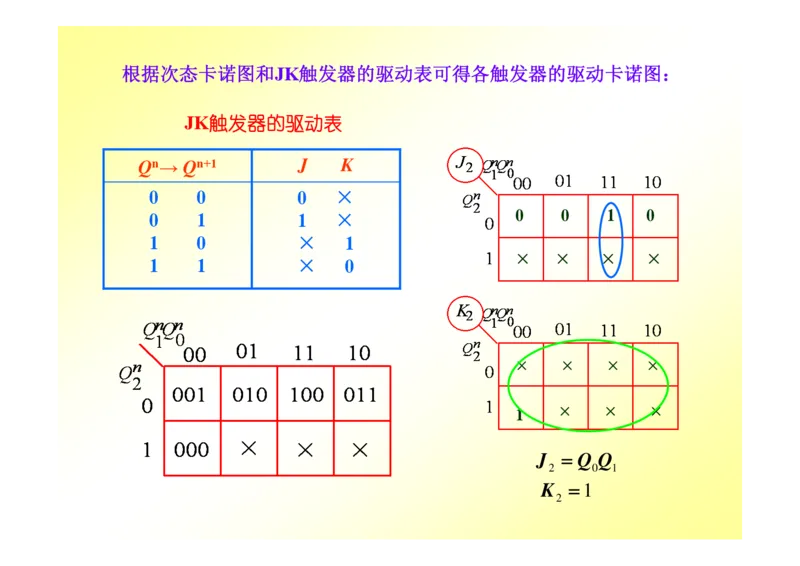

1 1 × 0根据次态卡诺图和JK触发器的驱动表可得各触发器的驱动卡诺图:

JK触发器的驱动表

Qn→ Qn+1 J K

0 0 0 ×

0 0 1 0

0 1 1 ×

1 0 × 1

× × × ×

1 1 × 0

× × × ×

1 × × ×

J = Q Q

2 0 1

K = 1

2JK触发器的驱动表

Qn→ Qn+1 J K

0 0 0 ×

0 1 1 ×

1 0 × 1

1 1 × 0

J = Q

0 1 × × × × 1 0 1 0

K = Q

1 0

0 × × × × × × ×

J = Q

1 × × 1 × 1 1 ×

0 2

K = 1

0

× × × × × ×

0 ×再画出输出卡诺图

可得电路的输出方程: Y = Q

2

(5)将各驱动方程归纳如下:

K = 1

J = Q

0

0 2

J = Q K = Q

1 0 1 0

J = Q Q K = 1

2 0 1 2

(6)画逻辑图。(7)检查能否自启动

利用逻辑分析的方法画出电路完整的状态图。

可见,如果电路进入无效状态101、110、111时,在CP

脉冲作用下,分别进入有效状态010、010、000。所以

电路能够自启动。3.一般时序逻辑电路的设计举例

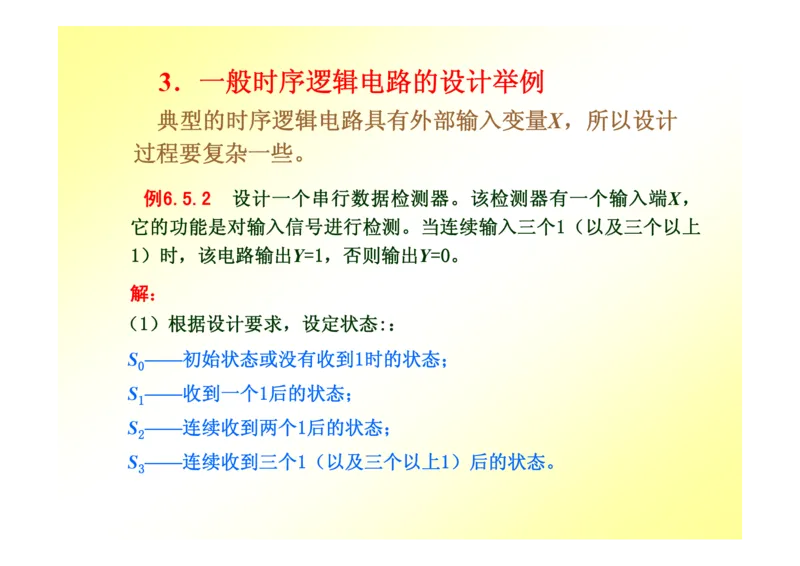

典型的时序逻辑电路具有外部输入变量X,所以设计

过程要复杂一些。

例6.5.2 设计一个串行数据检测器。该检测器有一个输入端X,

它的功能是对输入信号进行检测。当连续输入三个1(以及三个以上

1)时,该电路输出Y=1,否则输出Y=0。

解:

(1)根据设计要求,设定状态::

S ——初始状态或没有收到1时的状态;

0

S ——收到一个1后的状态;

1

S ——连续收到两个1后的状态;

2

S ——连续收到三个1(以及三个以上1)后的状态。

3(2)根据题意可画

出原始状态图:

(3)状态化简。

观察上图可知,S

2

和S 是等价状态,

3

所以将S 和S 合并,

2 3

并用S 表示,得简

2

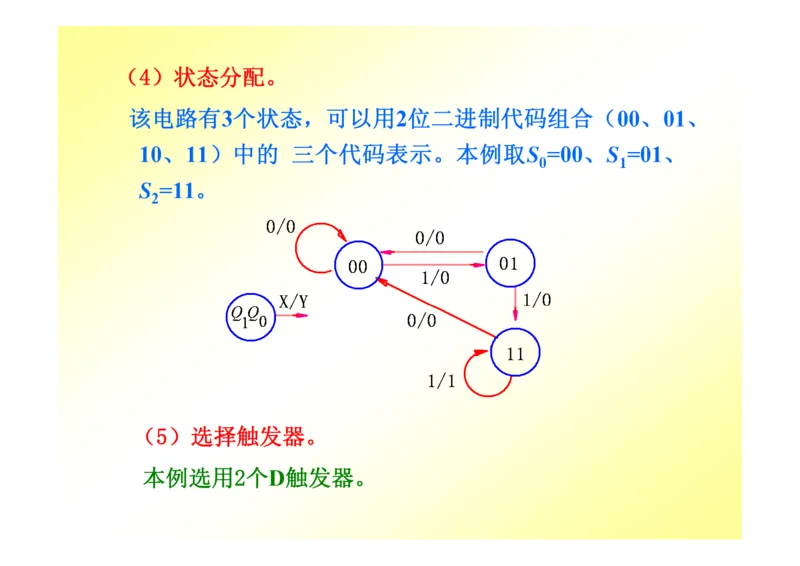

化状态图:(4)状态分配。

该电路有3个状态,可以用2位二进制代码组合(00、01、

10、11)中的 三个代码表示。本例取S =00、S =01、

0 1

S =11。

2

(5)选择触发器。

本例选用2个D触发器。(6)求出状态方程、驱动方程和输出方程。

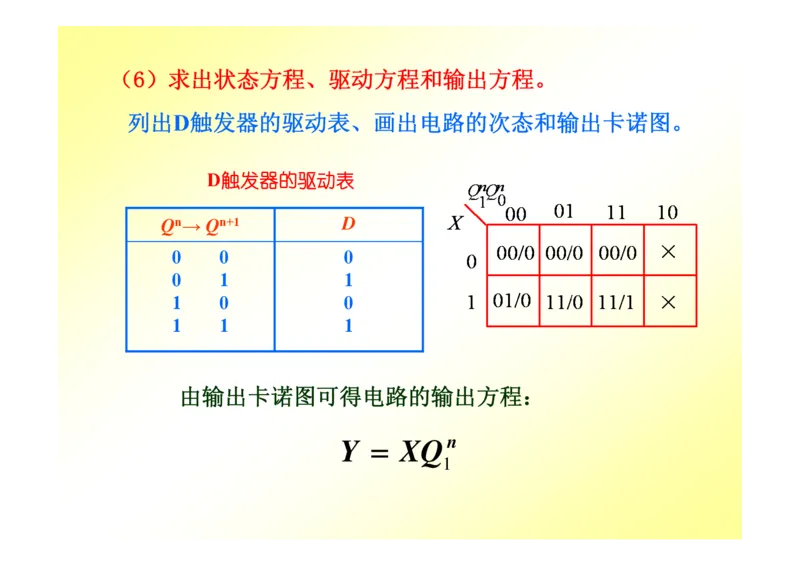

列出D触发器的驱动表、画出电路的次态和输出卡诺图。

D触发器的驱动表

Qn→ Qn+1 D

0 0 0

0 1 1

1 0 0

1 1 1

由输出卡诺图可得电路的输出方程:

n

Y = XQ

1根据次态卡诺图和D触发器的驱动表可得各触发器的驱动卡诺图:

D触发器的驱动表

Qn→ Qn+1 D

0 0 0

0 1 1

1 0 0

1 1 1

0 0 0 × 0 0 0 ×

0 1 1 × 1 1 1 ×

由各驱动卡诺图可得电路的驱动方程: D = XQn

1 0

D = X

0(7)画逻辑图。

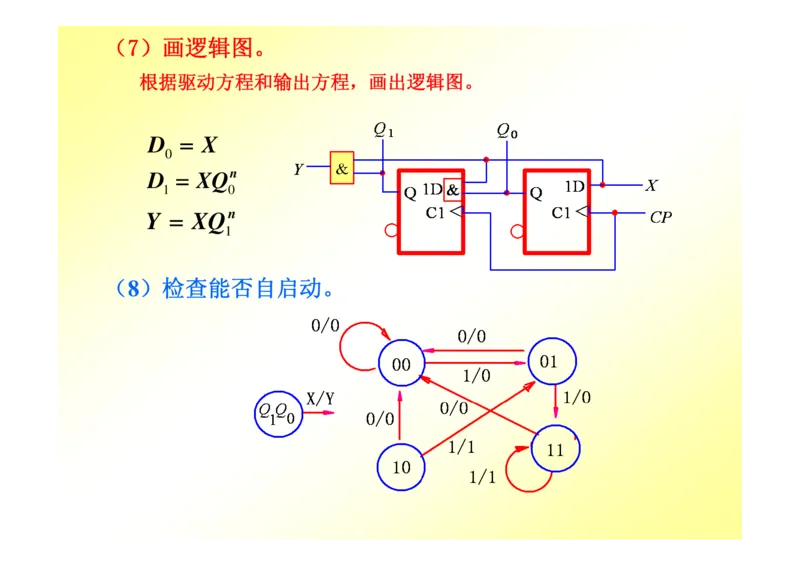

根据驱动方程和输出方程,画出逻辑图。

D = X

0

D = XQn

1 0

n

Y = XQ

1

(8)检查能否自启动。二、异步时序逻辑电路的设计方法

异步时序电路的设计比同步电路多一步,即求各触发器的时钟方程。

例6.5.3 设计一个异步7进制加法计数器.

(1)根据设计要求,设定7个状态S ~S 。进行状态编码后,列出

0 6

状态转换表。

现 态 次 态 进位输出

状态转换顺序

Q n Q n Q n Q n+1 Q n+1 Q n+1 Y

2 1 0 2 1 0

S 0 0 0 0 0 1 0

0

S 0 0 1 0 1 0 0

1

S 0 1 0 0 1 1 0

2

S 0 1 1 1 0 0 0

3

S 1 0 0 1 0 1 0

4

S 1 0 1 1 1 0 0

5

S 1 1 0 0 0 0 1

6(2)选择触发器。本例选用下降沿触发的JK触发器。

(3)求各触发器的时钟方程,即为各触发器选择时钟信号。

为触发器选择时钟信号的原则是:

①触发器状态需要翻转时,必须要有时钟信号的翻转沿送到。

②触发器状态不需翻转时,“多余的” 时钟信号越少越好。

根据上述原则,选:

画出7进制计数器的时序图:

CP = CP

0

CP = CP

1

CP = Q

2 1(4)求各触发器的驱动方程和进位输出方程。

画出电路的次态卡诺图和JK触发器的驱动表:

JK触发器的驱动表

Qn→ Qn+1 J K

0 0 0 ×

0 1 1 ×

1 0 × 1

1 1 × 0

由次态卡诺图和触发器的驱动表求驱动方程:

× × 1 ×

× × × ×

× × × ×

× × × 1

CP = Q

2 1

J = 1 K = 1

2 2JK触发器的驱动表

Qn→ Qn+1 J K

0 0 0 ×

0 1 1 ×

1 0 × 1

1 1 × 0

CP = CP

1

J = Q

0 1 × × × × 1 0

1 0

K = Q + Q

0 1 × × × × × 1 1 0 2

CP = CP

0

J = Q + Q

1 × × 1 × 1 1 × 0 2 1

K = 1

0

1 × × 0 × 1 × ×再画出输出卡诺图,

得电路的输出方程:Y = Q Q

2 1

将各驱动方程归纳如下:

0 0 0 0

J = Q + Q K = 1

0 2 1 0

0 0 × 1

J = Q K = Q + Q

1 0 1 0 2

J = 1 K = 1

2 2

(5)画逻辑图。(6)检查能否自启动。

用逻辑分析的方法画出电路完整的状态图:

可见,当电路进入无效状态111时,在CP脉冲作用下

可进入有效状态000。所以电路能够自启动。本章小结

1.时序逻辑电路的特点;任一时刻输出状态不仅取决于当时的输入

信号,还与电路的原状态有关。因此时序电路中必须含有存储器

件。

2.描述时序逻辑电路逻辑功能的方法有状态转换真值表、状态转换

图和时序图等。

3.时序逻辑电路的分析步骤一般为:逻辑图→时钟方程(异步)、

驱动方程、输出方程→状态方程→状态转换真值表→状态转换图

和时序图→逻辑功能。

4.时序逻辑电路的设计步骤一般为:设计要求→最简状态表→编码

表→次态卡诺图→驱动方程、输出方程→逻辑图。

5.计数器是一种简单而又最常用的时序逻辑器件。计数器不仅能用于

统计输入脉冲的个数,还常用于分频、定时、产生节拍脉冲等。

6.用已有的M进制集成计数器产品可以构成N(任意)进制的计数器。

7.寄存器也是一种常用的时序逻辑器件。寄存器分为数码寄存器

和移位寄存器两种。6.9 试分析图示的计数器电路。写出它的驱动方程、

状态方程,列出状态转换真值表和状态图,说明

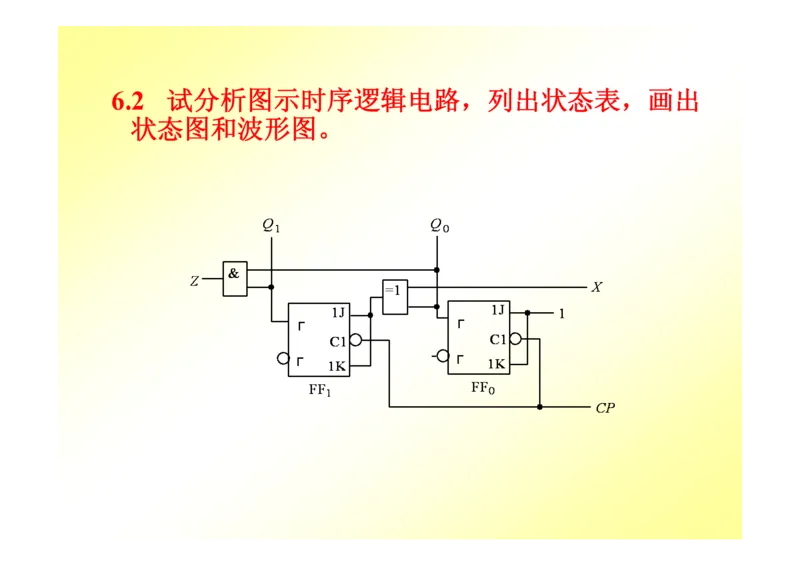

是几进制计数器。6.2 试分析图示时序逻辑电路,列出状态表,画出

状态图和波形图。6.8 试分析图示的计数器电路。写出它的驱动方程、

状态方程,列出状态转换真值表和状态图,说明

是几进制计数器。6.12 试分析图示电路,画出它的状态图,说明它是

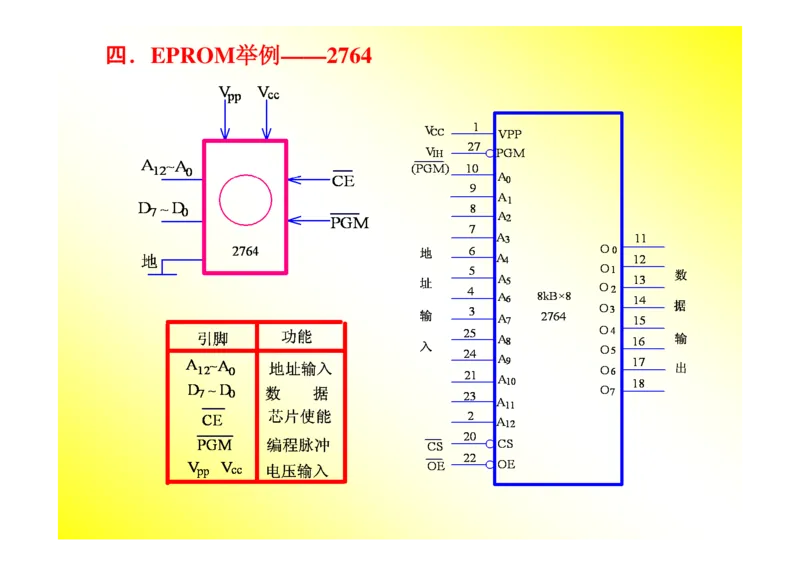

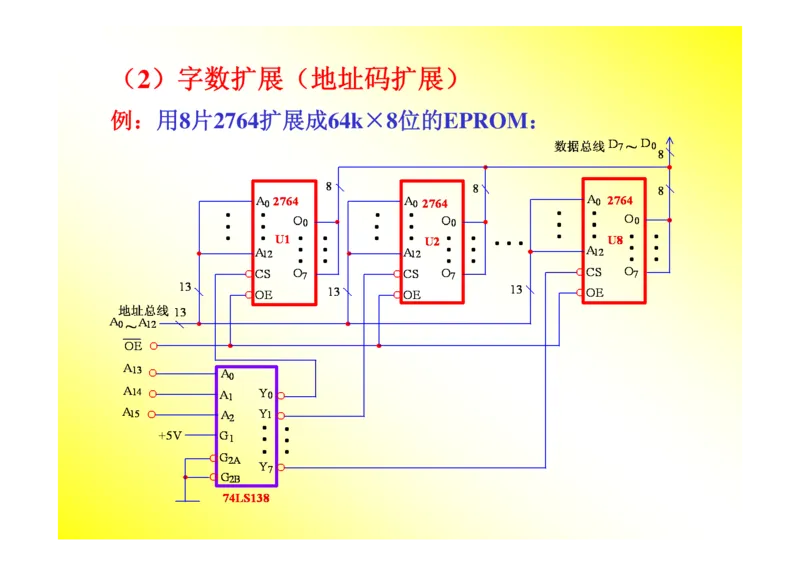

几进制计数器。第七章 半导体存储器

7.1 随机存取存储器(RAM)

RAM的基本结构

RAM的存储单元

RAM的容量扩展

RAM的芯片介绍

7.2 只读存储器(ROM)

ROM的分类

ROM的结构及工作原理

ROM的应用

ROM的容量扩展存储器的基本概念

存储器——用以存储二进制信息的器件。

半导体存储器的分类:

根据使用功能的不同,半导体存储器可分为两大类:

(1)随机存取存储器(RAM)也叫做读/写存储器。既能

方便地读出所存数据,又能随时写入新的数据。RAM的

缺点是数据易失,即一旦掉电,所存的数据全部丢失。

(2)只读存储器(ROM)。其内容只能读出不能写入。

存储的数据不会因断电而消失,即具有非易失性。

存储器的容量:存储器的容量=字长(n)×字数(m)7.1 随机存取存储器(RAM)

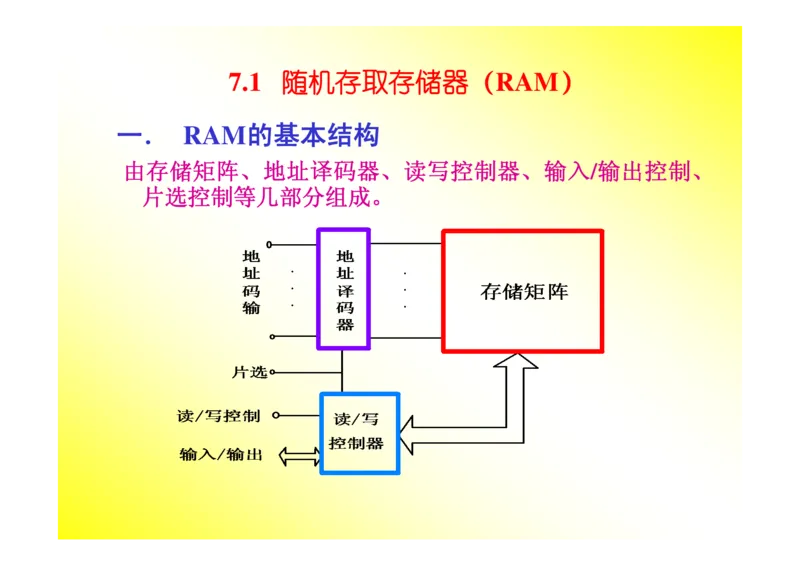

一. RAM的基本结构

由存储矩阵、地址译码器、读写控制器、输入/输出控制、

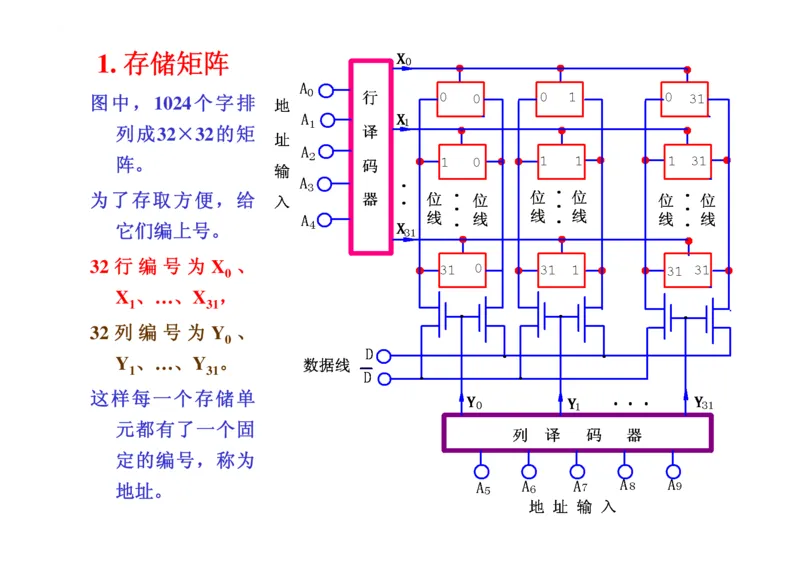

片选控制等几部分组成。1. 存储矩阵

图中,1024个字排

列成32×32的矩

阵。

为了存取方便,给

它们编上号。

32 行 编 号 为 X 、

0

X 、…、X ,

1 31

32 列 编 号 为 Y 、

0

Y 、…、Y 。

1 31

这样每一个存储单

元都有了一个固

定的编号,称为

地址。2.地址译码器—— 将寄

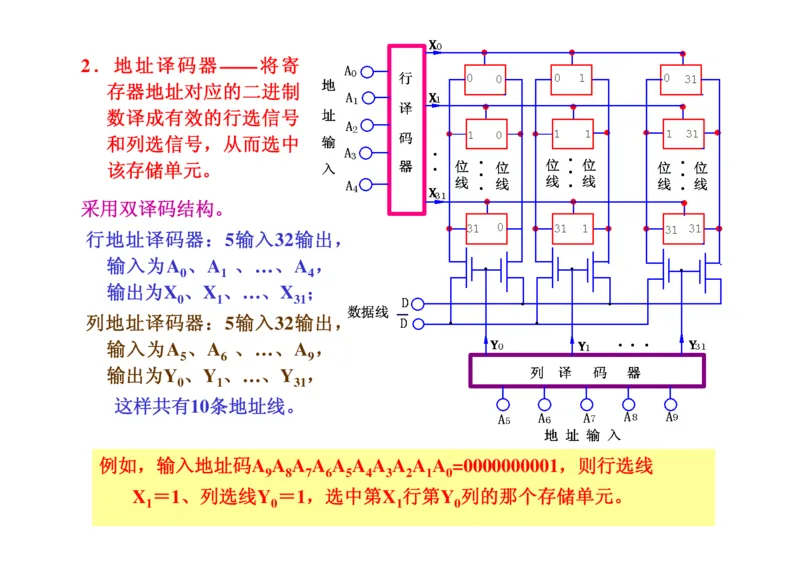

存器地址对应的二进制

数译成有效的行选信号

和列选信号,从而选中

该存储单元。

采用双译码结构。

行地址译码器:5输入32输出,

输入为A 、A 、…、A ,

0 1 4

输出为X 、X 、…、X ;

0 1 31

列地址译码器:5输入32输出,

输入为A 、A 、…、A ,

5 6 9

输出为Y 、Y 、…、Y ,

0 1 31

这样共有10条地址线。

例如,输入地址码A A A A A A A A A A =0000000001,则行选线

9 8 7 6 5 4 3 2 1 0

X =1、列选线Y =1,选中第X 行第Y 列的那个存储单元。

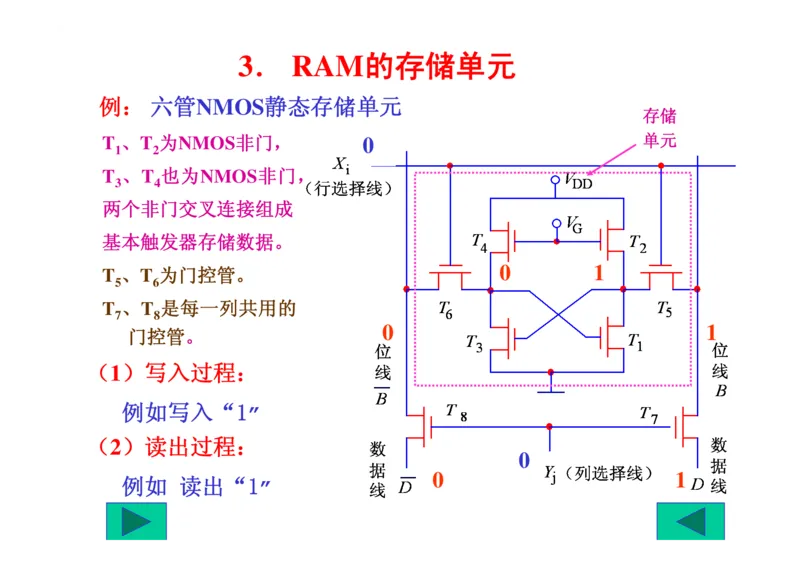

1 0 1 03. RAM的存储单元

例: 六管NMOS静态存储单元

存储

T 、T 为NMOS非门, 0 单元

1 2 1

T 、T 也为NMOS非门,

3 4

两个非门交叉连接组成

基本触发器存储数据。

0 1

T 、T 为门控管。

5 6

T 、T 是每一列共用的

7 8

0 1

门控管。

(1)写入过程:

例如写入“1

”

(2)读出过程:

01

0 1

例如 读出“1

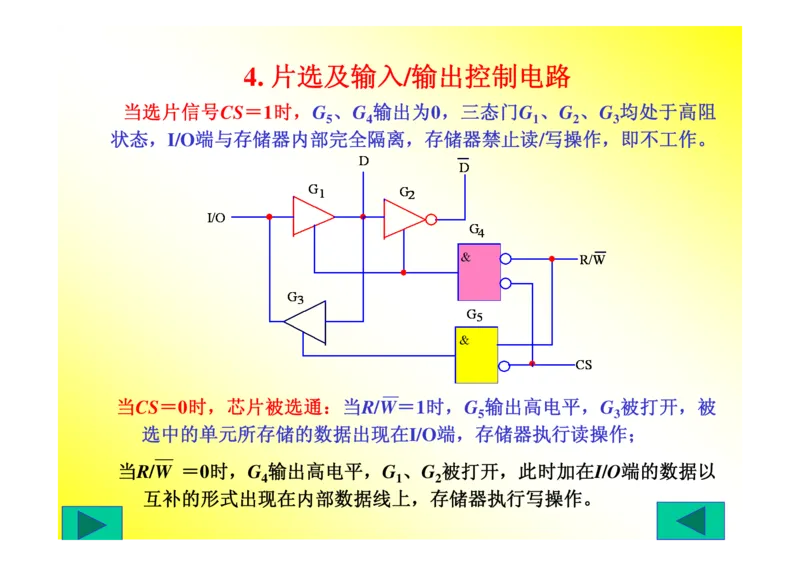

”4. 片选及输入/输出控制电路

当选片信号CS=1时,G 、G 输出为0,三态门G 、G 、G 均处于高阻

5 4 1 2 3

状态,I/O端与存储器内部完全隔离,存储器禁止读/写操作,即不工作。

当CS=0时,芯片被选通:当R/W=1时,G 输出高电平,G 被打开,被

5 3

选中的单元所存储的数据出现在I/O端,存储器执行读操作;

当R/W =0时,G 输出高电平,G 、G 被打开,此时加在I/O端的数据以

4 1 2

互补的形式出现在内部数据线上,存储器执行写操作。二. RAM的工作时序(以写入过程为例)

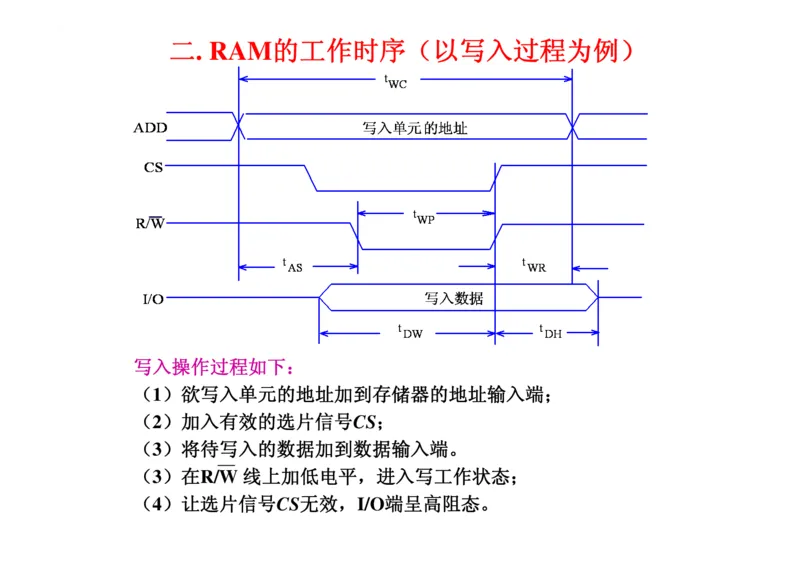

写入操作过程如下:

(1)欲写入单元的地址加到存储器的地址输入端;

(2)加入有效的选片信号CS;

(3)将待写入的数据加到数据输入端。

(3)在R/W 线上加低电平,进入写工作状态;

(4)让选片信号CS无效,I/O端呈高阻态。三. RAM的容量扩展

1.位扩展

用8片1024(1K)×1位RAM构成的1024×8位RAM系统。2.字扩展

例:用8片1K×8位RAM构成的8K×8位RAM。四、RAM芯片简介(6116)

6116为2K×8位的静态CMOSRAM

A ~A 是地址码输入端,

0 10

D ~D 是数据输出端,

0 7

CS是选片端,

OE是输出使能端,

WE是读写控制端。

6116的功能表

片选 输出使能 读/写控制 地址码输入 输 出

工作模式

CS OE WE A ~ A D ~ D

0 10 0 7

1 × × × 高 阻 态 低功耗维持

0 0 1 稳定 输 出 读

0 × 0 稳定 输 入 写7.2 只读存储器(ROM)

一. ROM的分类

按照数据写入方式特点不同,ROM可分为以下几种:

(1)固定ROM。厂家把数据写入存储器中,用户无法进行任何修改。

(2)一次性可编程ROM(PROM)。出厂时,存储内容全为1(或全

为0),用户可根据自己的需要编程,但只能编程一次。

(3)光可擦除可编程ROM(EPROM)。采用浮栅技术生产的可编程

存储器。其内容可通过紫外线照射而被擦除,可多次编程。

(4)电可擦除可编程ROM(E2PROM)。也是采用浮栅技术生产的可

编程ROM,但是构成其存储单元的是隧道MOS管,是用电擦除,并

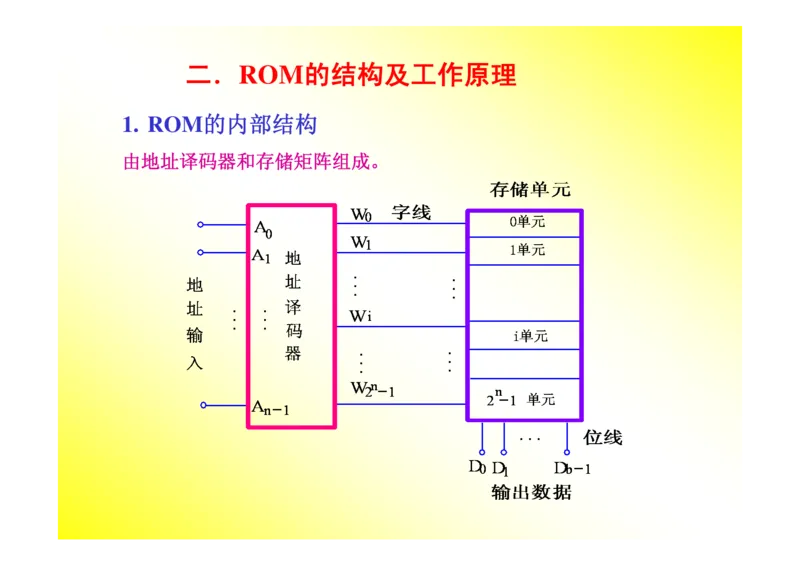

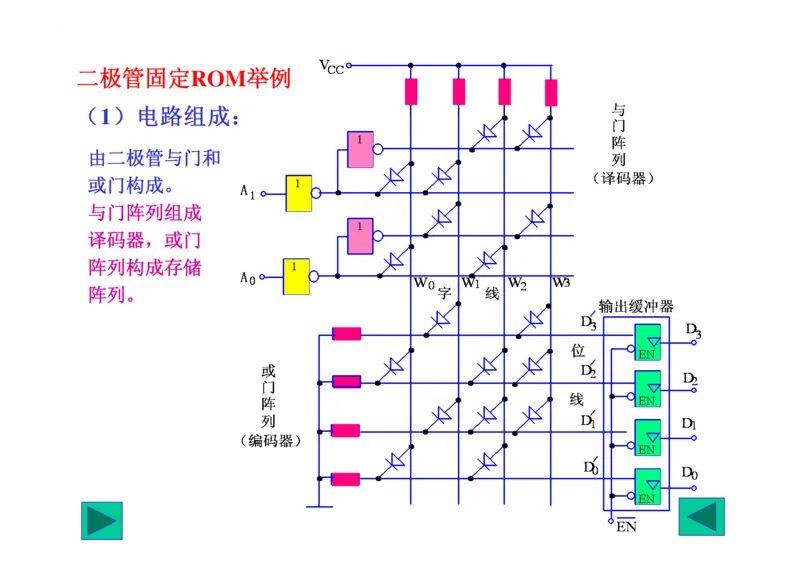

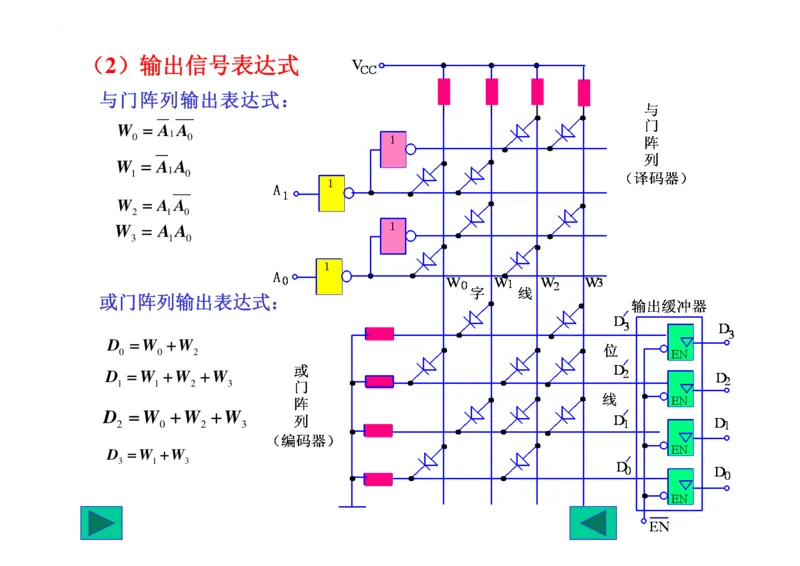

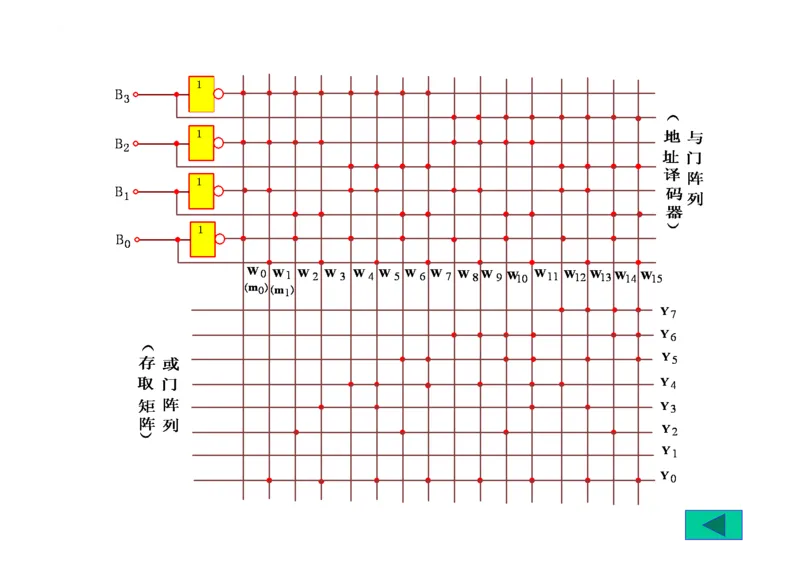

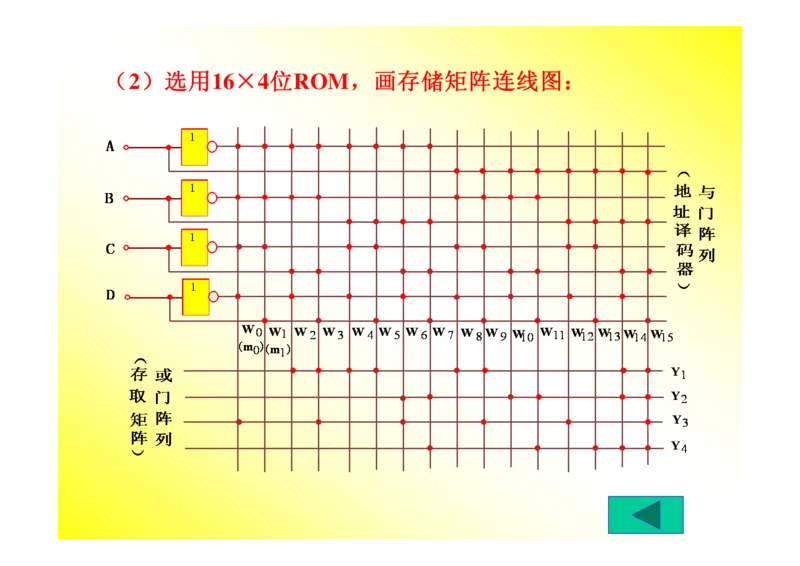

且擦除的速度要快的多(一般为毫秒数量级)。E2PROM的电擦除