AI半导体封装技术实战指南:从TSV到混合键合的全景解析

随着ChatGPT等AI技术的爆发式增长,AI半导体面临高功耗、数据瓶颈等挑战。本文深入解析2.5D/3D封装、TSV、HBM、Chiplet、混合键合等核心技术,为工程师提供实战技术指南。

📋 技术目录

1. AI半导体架构演进 — 从CPU/GPU到专用AI芯片

2. 2.5D封装实战 — 硅中介层、EMIB、玻璃中介层

3. 3D TSV技术 — 铜填充工艺与可靠性控制

4. Chiplet架构 — 异构集成的设计策略

5. 混合键合 — 无凸块的直接铜键合技术

一、AI半导体架构演进与技术挑战

在AI半导体专用化之前,CPU和GPU承担着AI运算和数据处理任务。CPU擅长顺序处理,GPU具有并行处理能力,更适合基于矩阵运算的AI计算。然而GPU并非专为AI设计,因此出现了FPGA和ASIC形式的NPU(神经网络处理器)。

⚡ 关键技术痛点

功耗瓶颈:超大规模AI运算参数量大,训练数据多,导致功耗急剧上升

速度制约:传统冯·诺伊曼架构下,内存与处理器分离造成数据瓶颈

物理极限:前道工艺7nm以下成本激增,单纯靠缩小工艺难以突破性能瓶颈

1.1 PIM(存内计算)架构

PIM技术将内存和处理器集成在同一芯片内部,打破传统冯·诺伊曼架构的内存墙限制。数据无需在内存和CPU之间频繁传输,从根本上解决了数据瓶颈和高功耗问题。

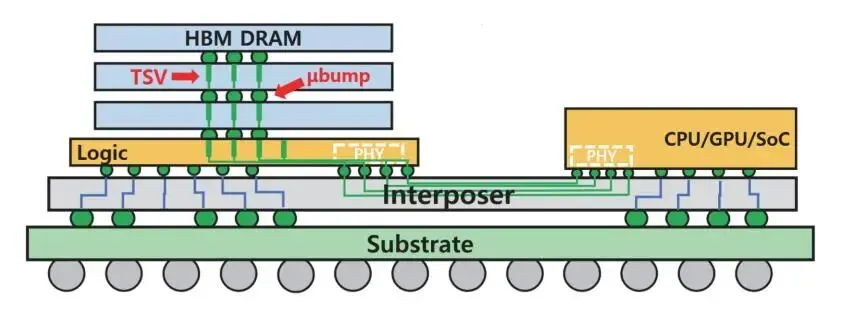

1.2 HBM(高带宽内存)技术

HBM通过TSV工艺将内存芯片垂直堆叠,大幅提升数据传输带宽并降低功耗。相比传统DRAM,HBM在容量、带宽和功耗效率上都有显著提升,是AI高速数据处理的必备技术。

图1 HBM的TSV垂直堆叠结构

二、2.5D封装技术实战解析

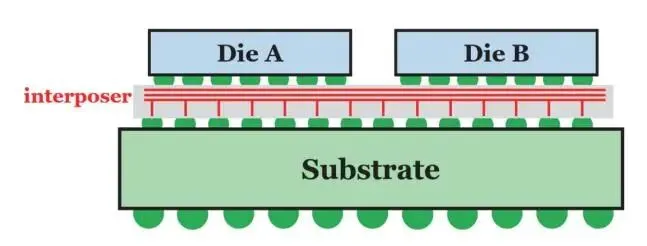

传统2D封装的MCM结构受限于互连线长度,带宽扩展遇到瓶颈。2.5D封装技术融合2D平面技术和3D堆叠技术优势,通过硅中介层实现芯片间高密度互连。

2.1 硅中介层技术

硅中介层通过微凸块、RDL重布线层、TSV和C4凸块实现芯片间互连。其超细线宽特性使得高带宽和快速数据运算成为可能。台积电CoWoS技术已成功应用于AI内存HBM。

🔧 工程师实战要点

互连结构:微凸块 → RDL布线 → TSV → C4凸块,形成完整信号路径

关键优势:线宽可缩小至微米级,带宽密度提升10倍以上

应用场景:HBM与GPU/CPU的集成,带宽需求超过500GB/s

图2 硅中介层2.5D封装结构

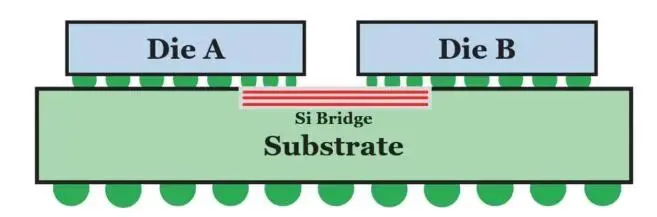

2.2 EMIB嵌入式桥接技术

Intel的EMIB技术使用硅桥形式连接异构芯片,相比硅中介层成本更低。EMIB在芯片间集成高密度互连,减小了板级面积和封装高度,显著提升芯片间数据传输速度。

图3 EMIB嵌入式桥接封装结构

2.3 玻璃中介层技术

硅中介层在高集成度时需要大量TSV,导致电损耗和热翘曲问题。玻璃中介层采用玻璃基板替代硅基板,具有高弹性模量和优异表面特性。使用500mm直径薄面板玻璃,相比300mm硅晶圆可显著降低封装成本。

💡 技术创新亮点

材料优势:玻璃介电常数低,导体损耗比硅减少30%以上

成本优势:500mm面板尺寸使单位面积成本降低40%

热性能:热膨胀系数与PCB基板接近,减少热应力

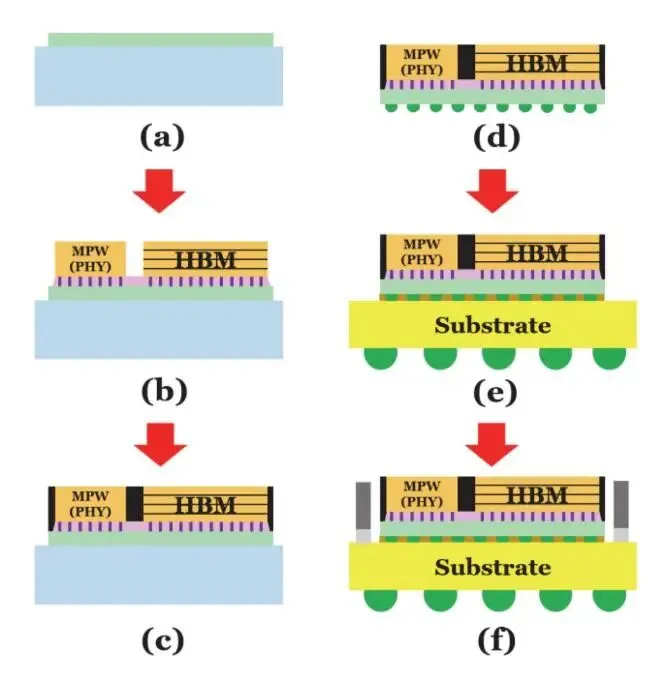

2.4 RDL中介层技术

RDL中介层用聚合物基RDL替代硅中介层,设计灵活度高。研究表明,RDL中介层金属线比硅中介层更厚时,25GHz频率下反射值降低4.714dB,信号反射损耗更小,电气性能更优。

图4 2.5D RDL中介层封装工艺流程

三、3D TSV封装技术与可靠性控制

传统PoP或SiP结构使用键合线,集成度提升困难且数据传输速度慢。TSV技术在芯片中形成通孔,用导电材料填充,实现上下芯片垂直电气连接,无需键合线。

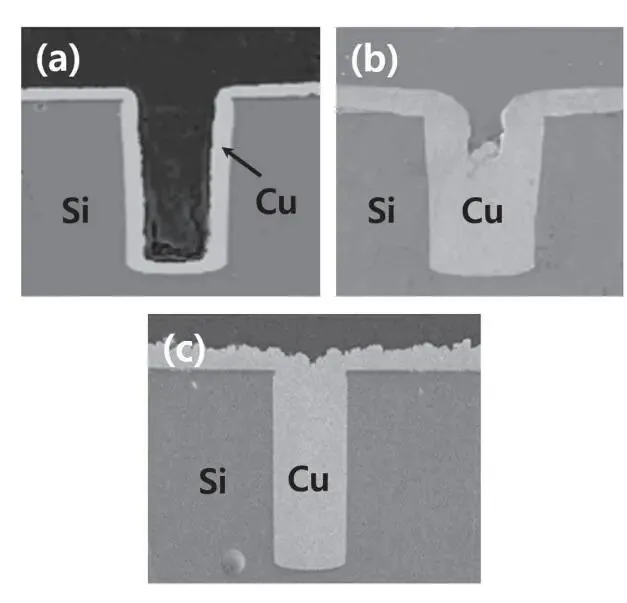

3.1 TSV铜填充工艺

TSV通常通过电镀铜填充。铜具有优异导电性、低成本和良好兼容性。然而铜离子优先在TSV入口和壁面还原,容易形成空洞缺陷。因此必须实现从底部向上的超共角电镀。

⚠️ 工艺控制要点

缺陷控制:Void缺陷会导致电气短路,影响AI计算性能

填充策略:采用3步PPR(周期脉冲反向)电流波形实现底部向上填充

高宽比挑战:随着深宽比增大,完整填充难度指数级上升

3.2 PPR电流波形优化

使用周期性脉冲电流可使镀铜周围铜离子浓度分布更均匀。但电镀与蚀刻反复循环导致填充时间延长。研究表明,优化后的PPR波形可将TSV填充时间缩短47%,显著提升生产效率。

图5 3步PPR电流TSV铜填充结果

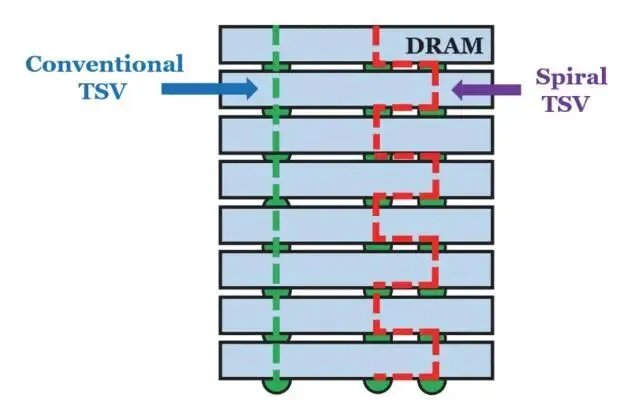

3.3 螺旋TSV创新设计

最新研究提出螺旋TSV阵列通道设计,通过改变每层DRAM连接方向提升传输性能。螺旋TSV间的接地引脚分配有效降低了通道损耗和通孔间串扰,为AI大数据高速运算提供解决方案。

图6 传统TSV与螺旋TSV结构对比

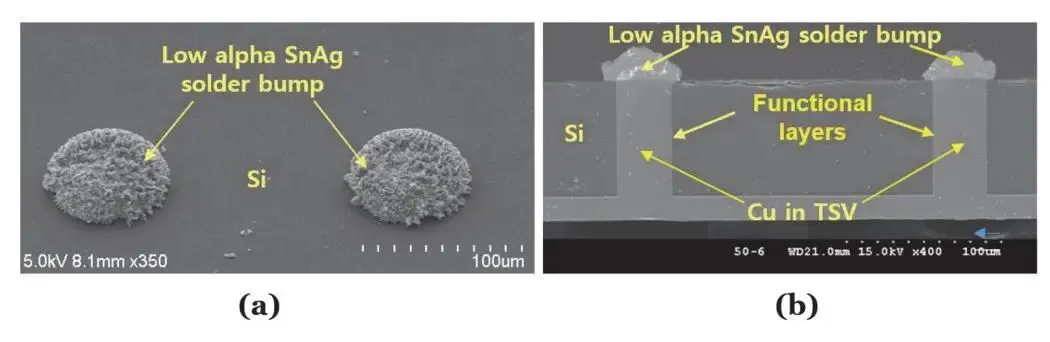

3.4 低α焊料凸块技术

AI半导体需要海量数据处理,必须无故障运行。普通焊料释放的α粒子会引起软错误,导致内存信息丢失和计算性能下降。低α焊料凸块(α放射量<5α/khr-cm²)是AI封装的必备技术。

图7 低α焊料凸块形貌(a)俯视图(b)截面图

🎯 可靠性测试数据

剪切强度:SAC105低α焊料在1.0m/s剪切速度下达到369.63mN峰值

失效模式:随剪切速度增加,脆性断裂比例上升

应用标准:LC3级低α焊料是AI封装的最低要求

四、Chiplet异构集成架构

Chiplet技术将单片芯片按功能拆分,通过TSV互连。相比单片设计,Chiplet在技术开发效率和量产良率方面具有显著优势。

4.1 良率与成本优势

实验数据显示,360mm²单片芯片良率仅15%,而4个Chiplet(各99mm²)良率达37%,提升两倍以上。虽然4个Chiplet总面积增加约10%的面积惩罚,但良率的显著改善可直接转化为成本节约。

📊 商业成功案例

Xilinx案例:2011年Virtex-7 FPGA因芯片过大导致良率极低

Chiplet方案:重新设计为4个小Chiplet,TSMC以高良率量产

产业意义:首个商业化Chiplet设计和异构集成封装产品

4.2 技术升级灵活性

单片芯片应用最新技术需要重新开发整个芯片,而Chiplet可按功能分区,只需选择性升级目标芯片。AMD的3D Chiplet集成技术使用有源TSV中介层,数据传输能力提升3倍,游戏性能平均提高15%。

五、混合键合技术前沿

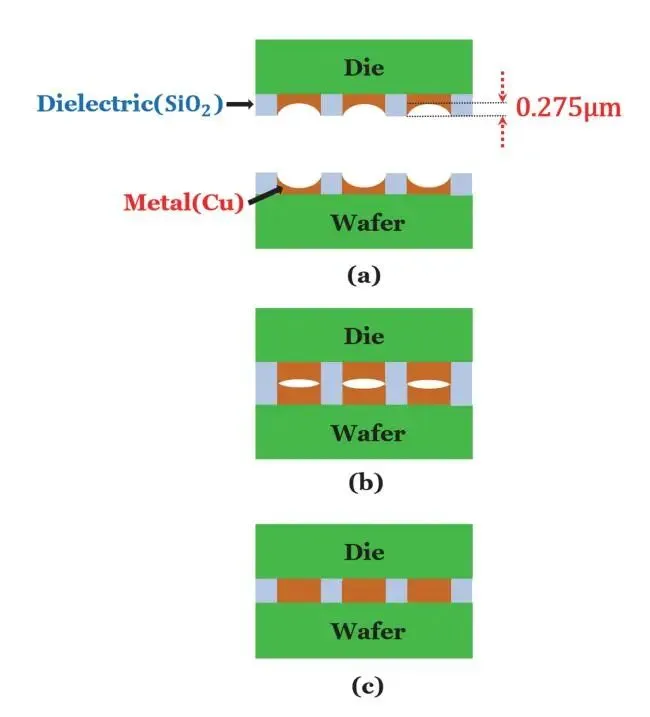

混合键合无需凸块,直接实现金属与介质或金属与聚合物的同步连接。通过CVD沉积铜形成电极,暴露铜电极相互键合形成Cu-SiO₂ 3D封装。理想Cu-SiO₂混合键合分三个主要阶段完成。

图8 Cu-SiO₂混合键合工艺流程

5.1 混合键合三阶段工艺

第一阶段是晶圆预处理,通过CMP化学机械抛光使介质和金属表面平整。第二阶段在室温下以低于15N压力将芯片与晶圆键合,此时由于碟状凹陷铜尚未接触。第三阶段经低温和高温退火后完成铜键合,形成理想混合键合结构。

🔬 关键工艺参数

CMP控制:Cu凹陷深度控制在0.275μm以内,确保键合质量

压力控制:键合压力<15N,避免晶圆损伤

退火工艺:低温退火消除应力,高温退火完成Cu扩散键合

5.2 低温混合键合突破

高温键合会降低已制造器件性能,系统半导体要求350°C以下,存储半导体要求250°C以下。采用纳米晶铜材料可在150°C低温下实现晶圆间混合键合,键合强度达12J/m²,形成极强键合界面。

5.3 表面预处理技术

铜表面氧化会形成扩散阻挡层,阻碍低温高质量键合。采用H₂SO₄、HCl、CH₃COOH和C₆H₈O₇酸溶液湿法预处理,可获得洁净无氧化物的铜表面,实现低温Cu-Cu混合键合。

⚡ 混合键合优势

互连密度:相比凸块键合,互连尺寸减小10倍,间距可达1μm以下

电气性能:寄生电感和电容显著降低,信号完整性大幅提升

带宽优势:满足AI半导体对超高密度互连和超大带宽需求

六、技术趋势与工程建议

AI半导体封装技术正在经历革命性变革。中介层技术通过高密度和细间距提升带宽,实现AI快速数据运算。HBM-PIM结构利用TSV封装实现高集成度并消除瓶颈。Chiplet和混合键合提供超高密度互连、更细间距和高可靠性。

🎯 工程师实战建议

1. 技术选型:根据应用带宽需求选择2.5D或3D封装方案

2. 可靠性设计:重点关注TSV填充缺陷控制和低α焊料应用

3. 成本优化:Chiplet架构可显著提升良率,降低总体成本

4. 前沿跟踪:混合键合是未来方向,建议提前布局研发

随着AI持续增长,对半导体封装产业将产生深远影响。前道工艺集成度提升面临物理极限,AI半导体先进封装技术的研发必须积极推进。封装工程师需要掌握TSV、混合键合等关键技术,设备工程师需要理解工艺对设备精度和稳定性的要求。

📚 关键技术总结

2.5D封装:硅中介层、EMIB、玻璃中介层、RDL中介层各有优势

3D TSV:铜填充工艺是核心,PPR电流波形优化提升效率

Chiplet:异构集成提升良率和设计灵活性

混合键合:无凸块直接键合,超高密度互连的未来方向

关注我们,私聊发送”资料+从TSV到混合键合的全景解析“,免费获取资料

每天分享最新的半导体技术文档、设备手册、应用案例

✅ KLA / ASML / Applied Materials 等设备资料

✅ 晶圆制造、封装测试、可靠性测试等技术文档

✅ 行业报告、技术白皮书、培训材料

点击关注 → 每天更新,助您技术进阶!

本文技术资料来源:首尔市立大学新材料工程系

翻译整理:半导体技术实战团队

转载请注明出处

夜雨聆风

夜雨聆风