AI ASIC:从台系ASIC厂商发展历程看国产产业链机遇(15页报告)

如需报告请联系客服或扫码获取更多报告

1. ASIC 设计服务:技术复杂性与成本优化双轮驱动

1.1. 先进制程复杂度抬升,ASIC 服务商成为关键枢纽

专业设计服务商是连接 IC 架构与 Foundry/OSAT 生态、并实现首片成功与系统级 稳定性的必要中介。先进制程下工艺复杂度的提升使得芯片设计成为严格的多物理场、多层次建模与精确协同问题,从而必然依赖专业的芯片设计服务商以保证首片成功与系统级性能达成。

1)器件与互连的制造变异增大,阈值电压漂移、线宽与栅极变化等随机/系统性工艺偏差对时序裕度和功能正确性产生显著影响,要求在设计阶段采用更精细的统计时序 分析与工艺-电路联合建模。

2)随着频率与集成度提升,信号完整性与电源完整性成为耦合问题:耦合串扰、时钟/数据抖动、包内电源阻抗和局部 IR-drop 必须在芯片-封装-板级跨域仿真中同时优化,单纯逻辑级或版图级的孤立验证已无法捕捉关键失效模式。

3)异构集成与多芯片架构把热、机械应力和电磁互联的影响带入几何尺度更小、互连更密的设计空间,TSV/微凸点/硅中介层的互连行为会反过来改变信号延迟与功耗分布,必须在早期物理分区和接口规范上与封装厂、晶圆厂协同定义。

4)高阶可靠性问题在亚纳米节点下对长期时序与噪声裕度的影响逐渐成为设计约束,要求将老化模型与在场传感/补偿机制纳入设计-验证流,避免运行期性能退化导致系统功能失效。

先进制程的这些技术性耦合与模型复杂性超出了典型单一产品团队在工具链、跨域仿真经验与晶圆/封装厂协同能力上的常规能力范围,因此需要具备端到端多物理场建模、统计验证、与 Foundry/OSAT 联合调试能力的专业芯片设计服务商来主导复杂系统的设计与验证流程。

工艺复杂度攀升促使设计服务商强化前端规划、后端布局与封装测试的一体化服务, 提高客户价值和项目成功率。随着制程节点不断收缩,多物理效应的协同设计已成必需,单靠后期实验难以保证成功率。先进制程和异构封装技术的迅速发展,迫使 ASIC 设计服务商通过一站式方案提升竞争力。ASIC 设计商能够将不同制程节点的逻辑和存储块在一套封装中整合,提高系统性能并缩短上市周期。

1.2. 量产导向成本优化,系统协同压缩价差

设计服务商将高度集中的一次性开发支出通过规模化项目实现分摊与可控化,通过 集中采购与工具/知识资产的复用,显著降低单案的软成本。先进制程下的固定开发成本已成为门槛性费用,单一项目独立承担将极大提升商业风险。设计服务商通过并行承接多项目、复用流程与模板,把不可回收的固定支出摊分到更广的客户群体。而 EDA 与商业 IP 本身具有高许可与维护成本,单个 IC 团队难以有效摊销;服务商通过内部化工具链、复用 IP 库与自动化签核套件,将这些长期性投入以摊销形式分担给多个项目,从而降低每案边际成本并提升交付效率。

服务商可通过组织共享原型与 Multi-Project Wafer 等并行投片机制,节省早期掩 膜与小批量试产成本。利用 MPW/shuttle run 等模式把多家设计聚合于同一掩膜/晶圆,能在原型验证阶段显著降低单案掩膜与试产开销,可以降低早期现金投入与验证风险。

设计服务商通过与 Foundry/OSAT 的长期协作与议价能力,降低因排期、迭代与返 工带来的隐性成本。具有稳定项目池和交付记录的服务商更易在晶圆/封测资源紧张时获得优先排产与批量调配,从而缩短整体迭代周期与避免多次返片导致的重复开销;Foundry 生态中也明确鼓励 Design-Enablement 伙伴协同以提升项目可预测性。

服务商的流程化项目管理与质量保障能把不可预见的返工成本转化为可量化的流 程费用。通过标准化的设计流程、验收门槛与可复用测试向量,服务商将传统上难以量化的管理与往返沟通成本变为可控的项目费用,减少因信息不对称或经验不足带来的额外支出,从而提高资本使用效率。

2. 从台系 ASIC 产业链的崛起看成长性

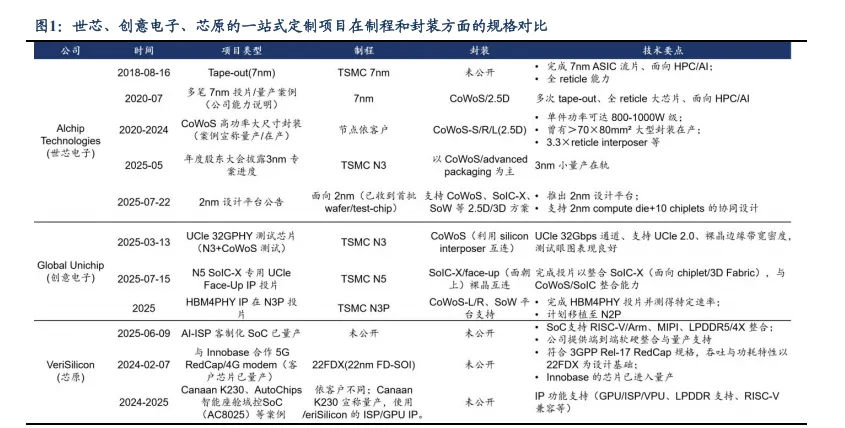

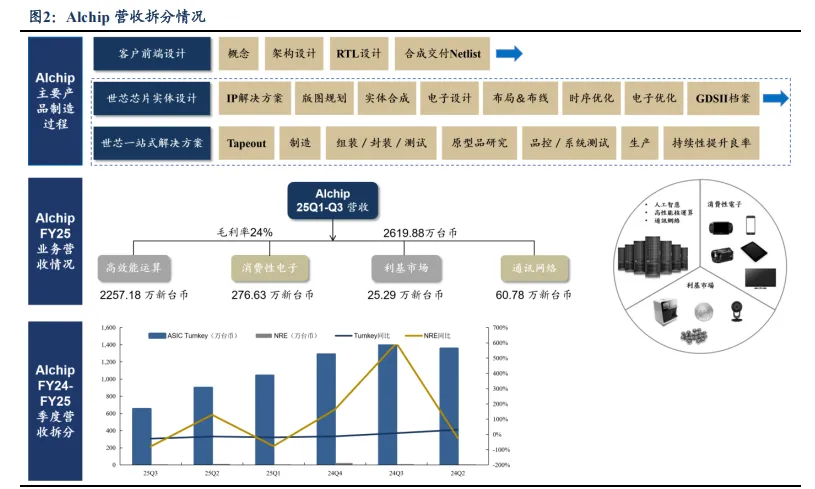

2.1. 世芯-KY:平台化 Turnkey 切入 AI/HPC 高价值订单

2.1.1. 发展历程:Turnkey 与先进封装驱动商业模式升级

世芯电子自 2003 年成立以来,始终以承接客户 ASIC/SoC 设计为核心并逐步制度 化其交付与产制能力。

模式 1.0(2003–约 2014)定位为受托 ASIC/SoC 设计的 fabless 公司。在该阶段,世芯主要对外提供 SoC 前端架构设计、RTL 整合、物理后端实现与基础的 IP 整合服务,客户关系以按案委托为主,公司的组织与交付聚焦于实现客户规格并完成首片/良率验证。世芯在 2003 年 8 月完成第一枚 0.13µm 芯片设计,并在随后的世代(90nm→65nm→40nm→28nm→16/14nm 等)陆续实现 tape-out 与量产,这是其从“纯设计接案”奠基到能够承担更复杂工程交付的技术根基。

模式 2.0(约 2010s–2021)定位为“Turnkey 一站式交付与分层委外体系化”。世芯在这一时期把服务从单纯的设计扩展为覆盖前端→后端→流片协调→封装/测试→量产导入的完整价值链,并在官网上以“Flexible Business Models”将客户合作模式制度化为 PD0(spec-in)→ PD1/PD1.5(RTL/netlist hand-off)→ PD2(GDS hand-off)→ PD2.5(chip hand-off)→ PD3(量产与良率改善),使其既能服务只需后端实现的系统厂商,也能服务需要全套 turnkey 的客户。这一转变依赖于:1)与 foundry(例如 TSMC)和OSAT 封测伙伴的长期合作关系与认证(世芯早年加入 TSMC DCA 并成为 VCA 成员为其奠基),使公司能承担 reticle-size FinFET 后端工程与流片统筹;2)构建封测与产后工程(PE/yield)团队与供应链管理体系,能将首片成功扩展为量产;3)把 IP 整合与验证流程制度化,确保多源 IP 在不同制程与封装下的兼容性与一次性通过率,将“第三方领先 IP 组合+内部/客制 IP 支援”作为服务定位,从而支持大型 SoC 整合。

模式 3.0(约 2021 年至今)可总结为“面向 AI/HPC 的 Platform-ASIC 伙伴,强化 先进制程与系统级封装能力”。行业进入 AI/HPC 周期,世芯在该阶段重点发展7/6/5/4/3nm 以及更先进节点的设计能量,并把先进封装(2.5D/3D/CoWoS、chiplet、3DIC)与系统级 PI/SI/热/功耗工程纳入常规交付范畴;世芯电子于 2022.6.15 宣布其高性能计算 ASIC 服务已可承接 3nm 设计,并以 2023 年第一季为首颗测试芯片目标,之后在2025.1.16 推出 3DIC 设计服务并在 2025.7.22 发布 2nm 设计平台/首批试片成果,这些表明其在端到端设计、die-to-die 整合与先进封装的生产就绪度逐步建立。这一转变更倚重系统级工程与平台化能力:首先需建立面向 3DIC/chiplet 的热/电/互连协同设计流程与验证平台,其次要有在先进制程(N7→N5→N3→N2)上持续的 tape-out 与试片成功案例以取得 foundry 与客户信任,最后需将 IP-to-system(含 die-to-die 互联 IP)与先进封装交付整合为可重复的商业产品。

如今公司商业模式可归纳为四个核心模块:1)设计服务(NRE/工程费),涵盖 SoC前后端与 IP 整合;2)产制协同与量产导入(turnkey management),负责 foundry 与封测供应链管理;3)先进封装与测试服务,包括 CoWoS、2.5D/3D 与 chiplet 方案;4)量产后工程与品质支持(Product Engineering / QA),用于提升良率与生命周期管理。公司通过供应链整合与快速量产导入提升客户 time-to-market 与成本效率,这构成公司商业模式逐步演进并切入 AI/HPC 高价值订单的核心逻辑。

2021 年 4 月世芯受美国对飞腾被列入实体清单影响,股价连续 5 个交易日跌停,从 920 新台币暴跌至 534 新台币,市值蒸发约 30 亿人民币。飞腾是世芯在中国大陆的最大客户,占当时公司营收比重接近 40%。美国商务部工业和安全局(BIS)将飞腾等7 家中国大陆超算实体列入实体清单后,世芯被迫暂停对飞腾的出货,市场担忧情绪导致股价大幅下挫。但世芯在 2021 年 Q1 的业绩表现亮眼,营收达 26.5 亿新台币(同比增长 74.9%),净利润 3.8 亿新台币(同比增长 120%)。世芯股价逐渐回升,2021 年底已恢复至 700-800 新台币区间。

2023-2024 年 AI 热潮推动股价暴涨。2023 年开始,随着全球 AI 算力需求爆发式增长,世芯凭借在 ASIC 设计领域的技术积累成功获得北美大客户订单。2023 年,世芯为理想汽车提供智能驾驶芯片后端设计服务,同时与特斯拉合作开发 Dojo 1 芯片。2024年世芯受益于北美客户 AI ASIC 出货及一款 5nm AI accelerator 放量,业绩大幅增长,全年营收达 519 亿新台币(同比增长 70%),净利润显著增长,北美市场营收占比从2023 年的 63%跃升至 2024 年的 86%,7nm 及以下先进制程贡献了 96%的营收。

夜雨聆风

夜雨聆风