DRAM全世代技术迭代八大维度优化点说明

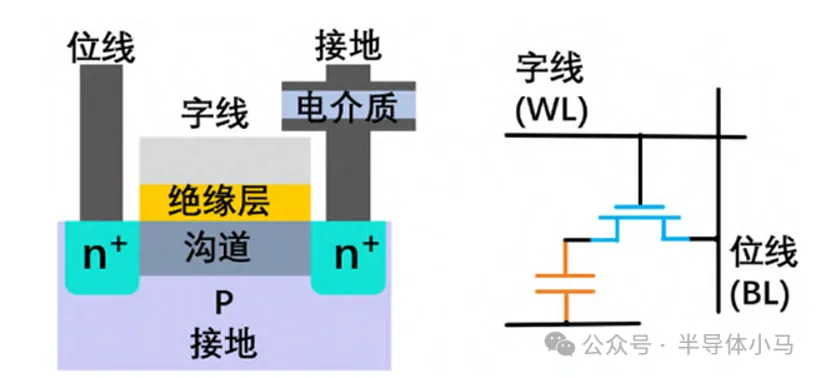

典型的DRAM结构单元由1个场效应晶体管和1个存取电容器(1T-1C)组成。接入晶体管的栅极端连接到字线(WL),漏极端通过位线触点(BLC)连接到位线(BL),另一端通过存储节点(SNC)连接到电容器。将接入晶体管作为开关,可以使电容器存储正/负电荷,从而存储比特数据。当晶体管关闭时,会向电容器上施加工作偏压。当晶体管被接通时,存储的电荷流入位线,产生一个电位变化,可以被连接到位线的放大器放大和检测,实现存储器数据信息的读取。

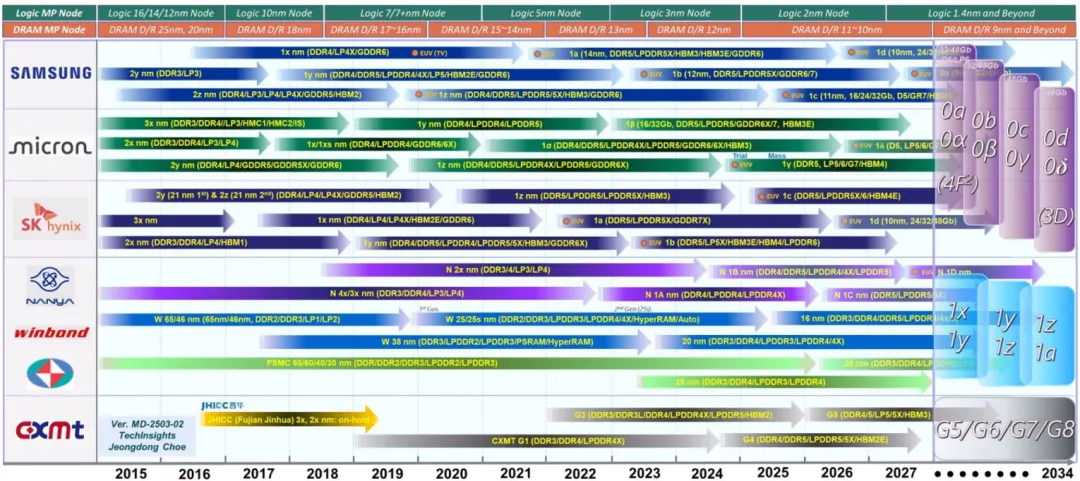

在早期,工艺节点名称确实与关键尺寸(如栅极长度)有一定对应关系。但随着技术发展到28nm以下,这种对应关系逐渐模糊。不同厂商在相同节点名称下,实际的物理尺寸可能存在显著差异。这种命名上的模糊性给行业分析和技术对比带来了不少困扰。

1)1x/1y/1z:过渡时期的命名约定

2015年前后,当DRAM行业进入20nm以下区间时,传统的纳米命名方式难以为继。三星、美光、SK海力士三大巨头开始采用字母后缀的方式来区分同代工艺的不同阶段:

-

1x nm:通常对应19-17nm级别,是该代工艺的”早期版本”

-

1y nm:约16-15nm级别,工艺的”中期优化版本”

-

1z nm:约14-12nm级别,该代工艺的”成熟版本”

2)1a/1b/1c:10nm级别的正式命名

当工艺继续微缩至10nm量级,DRAM行业正式采了”1a”、”1b”、”1c”的命名体系:

-

1a nm:约13-11nm,这是10nm级别的第一代产品

-

1b nm:约10-8nm,第二代10nm级工艺

-

1c nm:约7-5nm,第三代产品

3)0a/0b/0c/0d:10nm以下的探索

面向2025年及更远的未来,DRAM行业正在探索”0″开头的命名体系:

-

0a nm:预计对应5nm以下级别

-

0b/0c/0d:更遥远的下一代技术

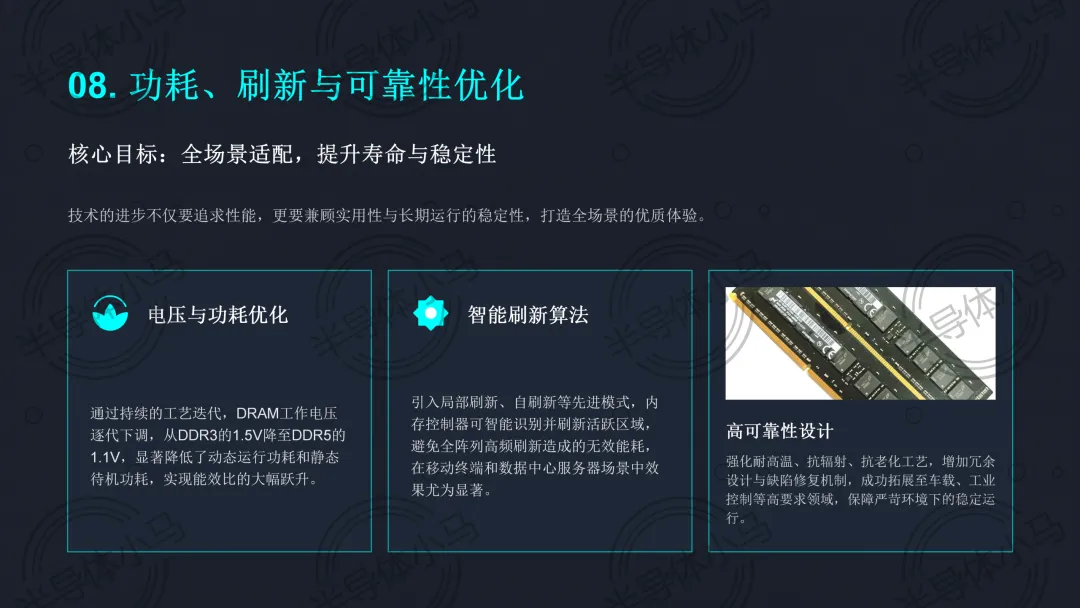

DRAM 全世代技术迭代按单元架构→工艺微缩→存储电容→晶体管→外围集成→传输接口→堆叠架构→功耗 / 可靠性八大维度推进,覆盖从传统微米级到 10nm 级(1α/1β/1c)+HBM 完整演进逻辑。

星球延伸阅读

-

DRAM Market Report.pdf

-

Memory Analyst Briefing -DRAM Session.pdf

-

DRAM 技术演进与未来趋势深度解析.pdf

-

DRAM技术迭代核心优化点.pptx

-

深入理解DRAM(DDR1~4).pdf

-

半导体深度报告:DRAM-存储芯片研究框架

-

DRAM Process flow.pdf

每增100人价格上调30元,即将上调~

夜雨聆风

夜雨聆风