硬核实测:把 OpenClaw 塞进本地,传统算力卡在了哪?

将 OpenClaw 这类高阶 AI Agent 进行私有化部署,已成为企业规避高昂云端 Token 账单与数据泄露风险的必由之路。然而,当 OpenClaw真正开始“干活”——在多个软件间无缝穿梭、进行逻辑思考并自动执行复杂任务时,其背后的系统消耗远非普通聊天 AI 可比。

把这样一位全能的“数字员工”塞进本地设备,究竟会遇到什么硬核阻力?本文跳过理论,只看实测数据。

内存墙:锁死生成速度的“隐形元凶”

目前驱动 OpenClaw 的前沿方案是 MoE(混合专家)架构大模型。它的机制极为聪明:帮你回邮件时调用“语言专家”,分析财报时唤醒“逻辑专家”,识别屏幕 UI 时切换至“视觉专家”。

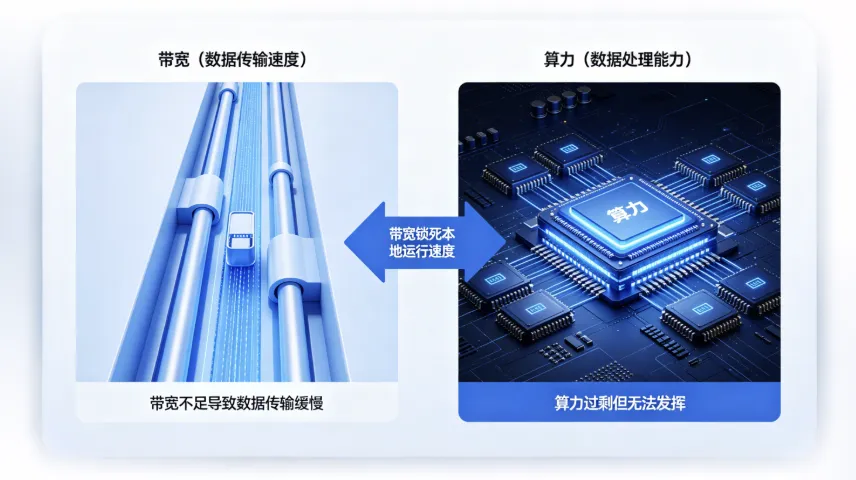

但这种按需切换的机制,对本地硬件提出了极其苛刻的要求——极高频的上下文切换与海量的内存读写。在这里,有一个决定生死的核心公式:

理论最大生成速度(Tokens/s)=内存带宽(GB/s)÷每次推理需读取的模型权重(GB)

以 Llama 4 Scout(Q4量化版)为例,每生成一个 Token,系统需要从内存中读取约 10GB 的激活参数权重。这意味着,如果芯片的内存带宽仅有 256 GB/s,其理论速度上限就被锁死在了25 Tokens/s 左右。扣除系统开销后,实际落地速度通常只有 10~18 Tokens/s。

结论:带宽,而非单纯的算力(TOPS),才是锁死 OpenClaw 本地运行速度的真正元凶。

AMD 395 极限拉扯:本地部署的现有天花板

为了探清现有硬件的极限,我们选取了目前极具代表性的高端移动端平台 AMD Ryzen AI MAX+ 395(Strix Halo)进行实测。

●硬件配置:16 核 Zen 5 CPU + 40 个 RDNA 3.5 计算单元。支持最高 128GB LPDDR5X-8000 统一内存。通过 VGM 技术,最高可将 96GB 划拨为独显显存——这是它能运行百亿参数模型的关键底牌。

●测试模型:Llama 4 Scout 109B Q4(MoE 架构,总参109B,激活参数17B)。

实测表现:优异,但逼近物理极限

●响应速度(TTFT):简单截图识别 <1秒;复杂 UI 理解与操作路径规划需 1~3 秒;长文档摘要加报表生成约 3~6 秒。这已处于本地部署的业界领先水平。

●生成速度:实测达到 13~18 Tokens/s,足以流畅驱动多应用 Agent 工作流。

●能耗比:满载 AI 推理功耗约 120~140W,相比双 GPU 服务器,能效比优势显著。同时支持最长 256K tokens 的上下文窗口(需开启 Flash Attention + Q8 KV Cache)。

核心洞察一:MoE 是“逆袭”的关键。

同样是 AMD 395,若运行 Dense(稠密)架构的 70B 模型,因带宽瓶颈速度会骤降至约 3 Tokens/s,几不可用。而 Llama 4 Scout 虽总参高达 109B,但每次推理仅激活 17B 参数,内存读取压力骤降,让 AMD 395 得以流畅运行。

核心洞察二:一个反直觉的横向对比。

●Apple M4 Max(128GB,内存带宽 546 GB/s):凭借更高的带宽,同模型下预估可达 20~28 Tokens/s。

●NVIDIA RTX 4090(24GB 显存,带宽 1008 GB/s):无论单卡还是双卡交火,即便带宽一骑绝尘,却因显存上限仅 24GB,根本无法完整加载体积达 66GB 的 Llama 4 Scout 109B 模型,直接宣告出局。

这揭示了一个残酷的事实:传统独立显卡的瓶颈不是不够快,而是“肚子太小”——统一内存架构(Unified Memory)才是本地运行大模型的绝对先决条件。

尽管 AMD 395 证明了本地运行百亿参数 AI 的可行性,但 256 GB/s 的带宽是一道难以逾越的“隐形天花板”。当面对OpenClaw 更复杂的多窗口并发、更长的上下文推理任务时,这面“内存墙”只会越来越厚。

扶光芯片:从底层重写内存的物理规则

如何在不无限增加功耗和成本的前提下,彻底推翻这面“内存墙”?微珩扶光芯片给出的答案是:2D + 3D 异构内存架构。

这不是在旧有框架内强行堆砌带宽,而是彻底重新定义内存的物理组织方式。

●3D DRAM(超速通道):通过 TSV(硅穿孔)技术将多层 DRAM 晶粒垂直堆叠,极大地缩短了数据传输路径并降低电气延迟。在扶光芯片中,3D DRAM 专门承载两类核心数据:

1. 高频激活的 MoE 专家权重:让每一次“专家切换”几乎做到零延迟,从传统的“算力等数据”变为“数据喂算力”。

2. 实时推理上下文(KV Cache):确保长序列任务(如长文档阅读、代码分析)的缓存读写速度完美契合推理节拍。

●2D DRAM(容量底座):以高密度、低成本的优势,承载模型中处于“待命状态”的非活跃专家权重与历史推理数据。

●智能调度引擎:位于两者之间的“超级大脑”,以纳秒级精度实时决定数据分流。

工作流实战解析:以“整理 50 页报告并发送邮件”这一复杂任务为例。意图识别与视觉元素捕捉走 3D DRAM 超速通道;长文档的上下文积累存入 2D DRAM 容量池;当进入多步骤行动规划时,数据再次无缝切回 3D DRAM。每一块内存都在做自己最擅长的事,彻底规避了传统单一架构下的带宽挤兑与争抢。

降维打击:桌面级Deepseek V4 284B 版本

依托这套革命性底层架构,设备得以驾驭旗舰级 DeepSeek-V4 Flash 284B 大模型,2840 亿超大体量参数,完成纯端侧落地,高效流畅运行全量推理任务。要知道,284B 级别大模型落地的最大拦路虎并非算力,而是“显存墙”。即使在当下,要想满血流畅运行这个量级的超级模型,依然需要依赖多卡并联的 NVIDIA B200(Blackwell架构)顶配算力服务器。而现在,通过 2D+3D 异构存算,我们在端侧撕开了一道突破口。扶光芯片,让一台普通的桌面级设备,实现了规模更大的 284B 本地推理。

本地 AI 算力的未来,绝不在于单纯地堆砌晶体管和 TOPS,而在于直击“大模型 + Agent”时代的真实命门——带宽与容量的平衡。

从 AMD 395 触碰到的 256 GB/s 天花板,到微珩扶光芯片凭借 2D+3D 异构架构完成的底层突破,我们正在见证一场算力范式的转移。最终的愿景正在化为现实:在你的办公桌上,放着一台无需联网、绝对安全,却拥有真正“数字员工”级别智力的本地机器。

微珩科技(Nanotrix)是端侧AI推理芯片领域创新引领者,凭借独创 3D LPU 专属架构,打造极致性能与超低功耗的端侧 AI 推理芯片,为智能终端、边缘计算等领域提供高效 AI 算力解决方案。

2025年初,Nanotrix由上市公司投资创立。团队由多位全球顶尖芯片设计公司的资深专家组成,在高性能芯片设计、先进制程、生产、封装及测试等方面有超过20年的经验和供应链积淀。该团队从2019年至今,成功设计了多款高性能计算芯片,累积销售额超10亿元人民币。

Nanotrix is a pioneering leader in the edge AI inference chip sector. Leveraging its proprietary 3D LPU architecture, Nanotrix develops edge AI inference chips with extreme performance and ultra-low power consumption, delivering high-efficiency AI computing power solutions for smart terminals, edge computing, and other fields.

In early 2025, Nanotrix was founded with investment from a listed company.

The team consists of multiple senior experts from the world’s leading chip design companies, with over 20 years of experience and supply chain expertise in high-performance chip design, advanced process nodes, manufacturing, 3D packaging, and testing. Since 2019, this team has successfully designed multiple high-performance computing chips, achieving cumulative sales exceeding RMB 1 billion.

联系我们:

公司地址:上海市徐汇区龙启路158号2201室

官网:https://www.nano-trix.com

邮箱:market@nano-trix.com

夜雨聆风

夜雨聆风