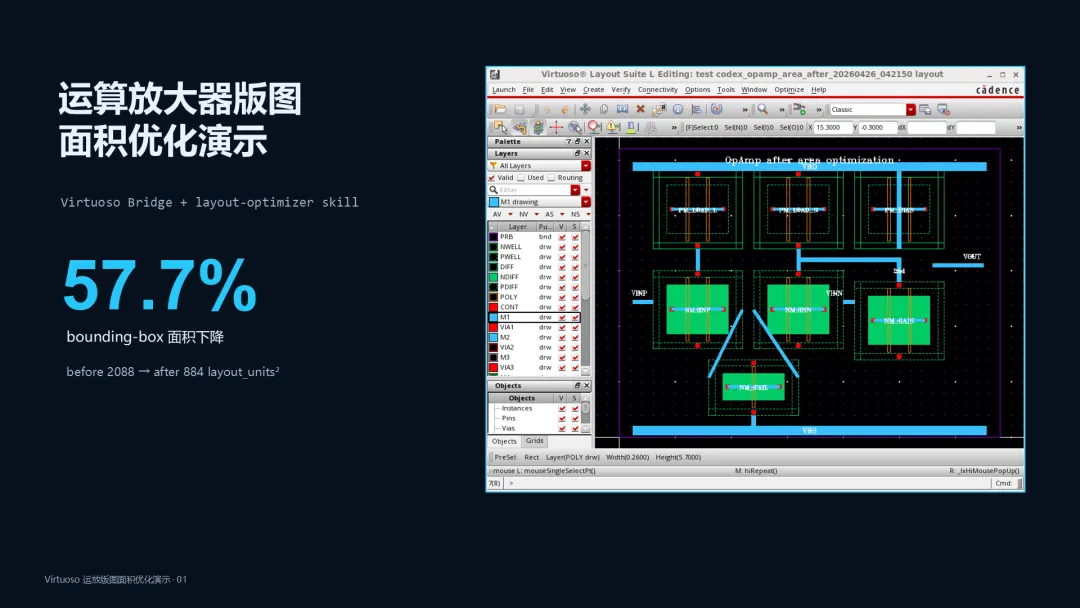

AI如何驱动IC版图优化实例演示

在集成电路设计领域,版图优化是连接电路设计与制造的关键环节。传统版图优化依赖工程师的经验积累,通常需要反复迭代才能达到面积、性能和良率的平衡。随着人工智能技术的发展,AI驱动的版图优化正逐渐成为行业关注的焦点。

本文通过一个运算放大器(OpAmp)的完整优化实例,详细展示AI在版图面积优化中的技术路径和实现流程。

注:本文中的面积优化数据为抽象演示版图的测试结果,不代表AI在实际生产PDK中的优化能力。实际优化效果需结合具体工艺进行验证。

一、技术背景与工具链

本次演示采用的技术方案基于: – Virtuoso Bridge:实现EDA工具与AI引擎的桥接 – layout-optimizer skill:AI版图优化核心技能模块

优化对象:运算放大器模拟版图

该版图包含差分对、尾电流管、PMOS负载、偏置电路和增益级等核心模块,涵盖了典型模拟电路的版图特征。

二、优化前后量化对比

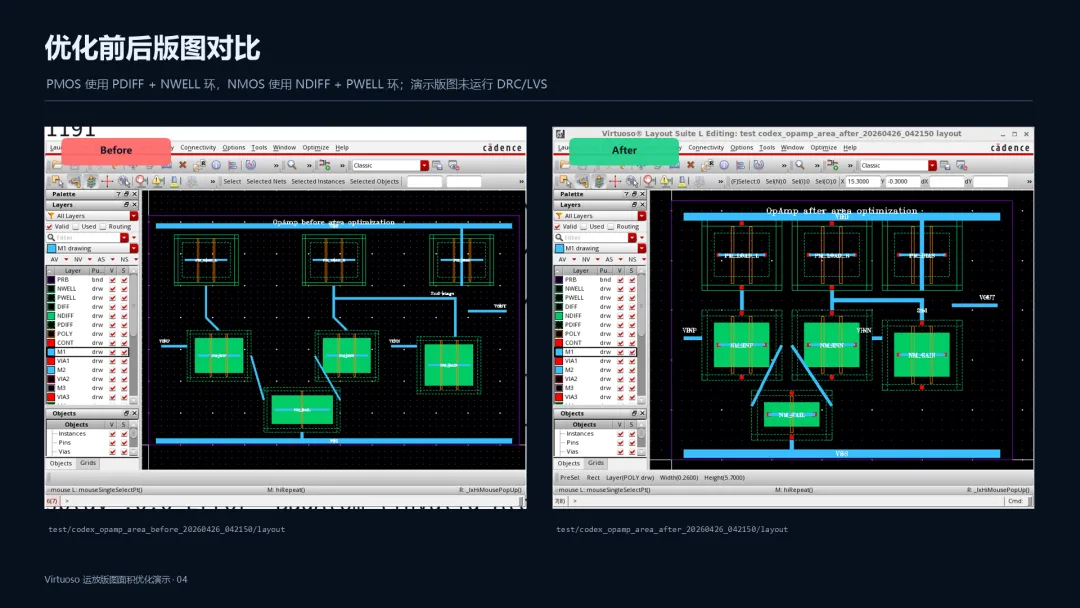

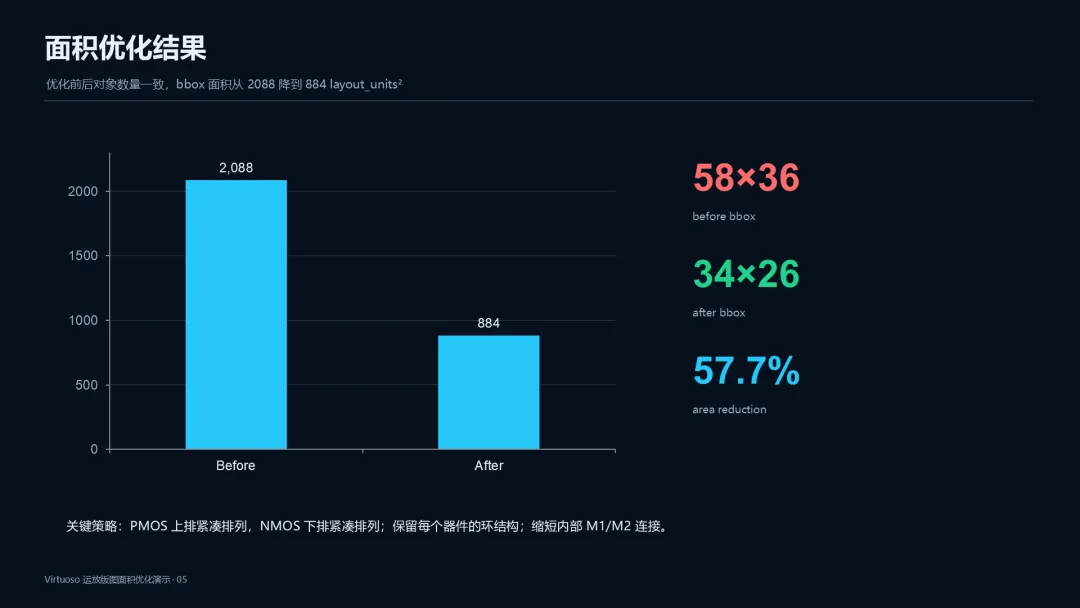

通过AI优化,该运算放大器版图实现了显著的面积缩减。以下是详细的量化指标对比:

|

|

|

|

|

|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-57.7% |

|

|

|

|

|

关键数据解读: – 面积缩减57.7%,意味着芯片成本可显著降低 – 对象总数保持不变,说明电路拓扑和连接关系完整保留 – 所有器件的隔离环约束均得到保持

三、AI优化策略详解

AI引擎生成的优化策略以结构化格式记录,包含分析、策略和执行顺序三个核心部分。

策略分析阶段

AI首先对原始版图进行几何分析,识别出布局松散的问题特征,发现该运算放大器版图的差分对、尾电流管、PMOS负载、偏置电路和增益级等器件分散在较宽的边界范围内。

优化策略1:实例重排

将PMOS器件紧凑排列在顶部一行,将NMOS器件紧凑排列在底部一行,包括PM_LOAD_L、PM_LOAD_R、PM_BIAS、NM_INP、NM_INN、NM_TAIL、NM_GAIN等所有器件。

技术要点: – 按器件类型分区排列(PMOS在上,NMOS在下) – 保持器件间的信号连接关系 – 预期贡献约55%的面积缩减

优化策略2:重新布线

在布局紧凑化后,对VINP、VINN、VOUT、VDD、VSS等所有节点进行重新布线,重点缩短局部M1/M2金属层的连接。

技术要点: – 重排后进行局部布线优化 – 重点缩短M1/M2金属层的关键路径 – 次要面积缩减,主要改善线长和性能

优化策略3:约束保留

保持每个PMOS块被NWELL环包围,每个NMOS块被PWELL环包围,确保器件隔离的完整性。

技术要点: – 保持所有PMOS被NWELL包围 – 保持所有NMOS被PWELL包围 – 确保器件隔离完整性

执行顺序

优化按照”重排→布线→约束验证”的顺序执行,确保策略的正确实施。

四、完整演示流程

本次演示遵循标准化的AI版图优化工作流,共分为5个关键步骤:

步骤1:创建宽松版图

-

生成初始的抽象运算放大器版图 -

器件布局相对松散,为优化留出空间 -

建立完整的电路拓扑和连接关系

步骤2:读取几何并统计bbox

-

解析版图几何数据结构 -

统计边界框尺寸和对象分布 -

生成初始版图的summary.json统计文件 -

记录优化前的各项几何指标

步骤3:生成压缩策略

-

AI引擎全面分析版图特征 -

识别布局优化的关键点和机会 -

生成结构化优化策略 -

评估各策略的预期效果和潜在风险

步骤4:创建紧凑副本

-

按照优化策略执行具体操作 -

首先进行器件重排,然后重新布线 -

生成优化后的新版图 -

验证约束完整性和设计规则

步骤5:导出报告与截图

-

生成详细的优化报告 -

保存优化前后的对比截图 -

生成优化后的统计数据文件 -

整理完整的工程交付物

五、技术实现与交付物

复现方法

演示可通过运行相关Python脚本完整复现整个优化过程。

交付物清单

本次优化演示提供完整的工程交付物:

|

|

|

|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

六、技术总结与展望

技术亮点

- 策略透明化

:优化策略以可读的格式记录,便于审计和调整 - 约束驱动

:在优化过程中保持关键设计约束(如阱隔离) - 可复现性

:完整的工程交付物和复现流程,支持结果重现 - 效率提升

:数分钟内完成传统工具数小时的工作量

适用场景

该技术方案适用于: – 模拟/混合信号电路版图优化 – 标准单元库面积优化 – 定制IP版图的快速迭代

未来展望

随着AI模型的持续训练和优化,未来有望在以下方面取得突破: – 多目标优化(面积+性能+良率) – 全流程DRC/LVS感知的优化 – 更复杂的射频/毫米波版图优化

注:本演示为抽象运算放大器版图演示,非PDK验证的掩膜版图。实际生产环境中需结合具体工艺PDK进行完整的DRC/LVS/PEX验证。

夜雨聆风

夜雨聆风