先进封装:AI算力背后的"隐形冠军"

朋友们好,我们之前对AI产业链的上游板块:光模块,存储芯片等环节进行了深度分析,今天我们把目光向中游靠一下,来聊聊即将爆发的工艺环节:先进封装!

喜欢的朋友可以随手点个关注和在看,您的点赞是博主更新的动力,非常感谢大家的阅读!

咱们开始进入正题!

为什么说先进封装是AI算力狂奔背后那个”闷声发大财”的隐形冠军呢?你想想,先不说咱们用的手机电脑等芯片,每一台算力服务器,算力需要的英伟达GPU,每一颗HBM内存,背后都离不开它。如果把AI芯片比作一个精密的大脑,那先进封装就是连接这些大脑细胞的神经和血管——没有它,GPU和HBM之间怎么协同?算力再强的芯片,数据传不动也白搭。

今天这篇文章,博主就从”AI为什么离不开封装”讲起,对这个产业链进行深度分析。

一、先进封装为什么突然这么”香”?

算力时代的底层矛盾很简单:芯片越做越小,数据越跑越多,传统封装装不下了。

一方面,AI算力每3.5个月就翻一番,数据中心带宽需求直接飙到100Tbps以上,传统封装根本扛不住这种级别的数据吞吐。另一方面,2nm以下制程逼近物理极限,硅晶体管快要碰到量子效应的天花板,继续往小做的成本翻了近三倍。

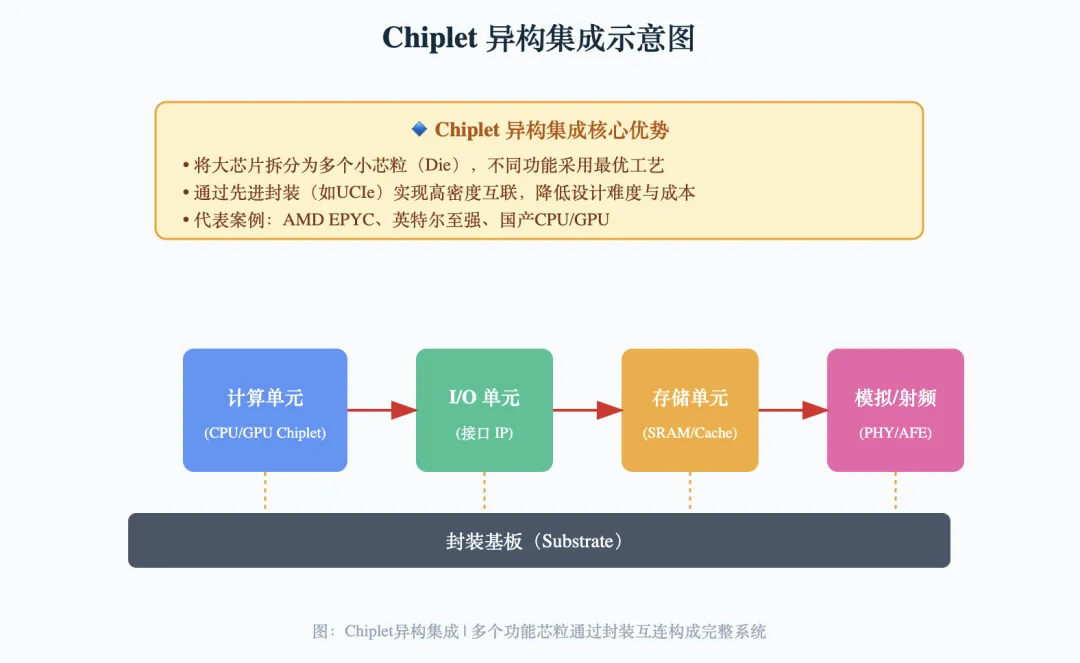

这两股力量一推,行业公认的解决方案就是异构集成——把多个不同工艺的芯片”拼”在一个封装里,用先进封装技术让它们协同工作。

二、主流封装技术:三路大军各显神通

先看一张博主整理的表格,把三种核心封装技术一次性理清:

下面逐一拆解。

🔥 CoWoS——台积电的绝对王牌

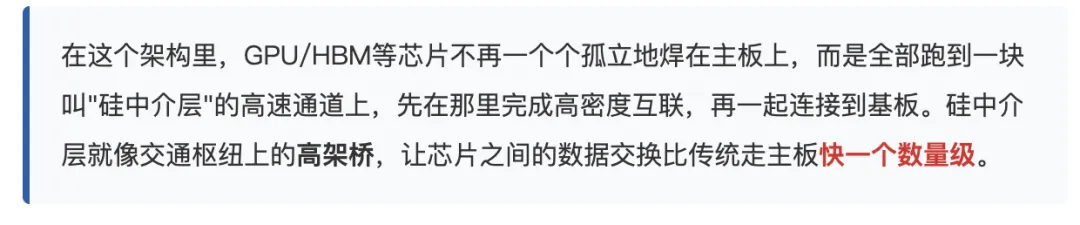

CoWoS的本质用一句话说就是:把计算和内存之间那条路修成”高速公路”。

台积电已经把CoWoS列为核心战略。目前已量产5.5倍光罩尺寸版本,规划2027年实现9.5倍光罩尺寸规模量产,单封装有效面积接近8000mm²,可支持4颗3D堆叠芯片系统、12层及以上HBM与多颗逻辑芯片高密度集成。按照台积电北美技术论坛的最新消息,远期目标更是要推到约14倍和40倍光罩尺寸,彻底要把先进封装做成系统级平台。

📊 产能方面供不应求。2026年底月产能预计达约11.5万至14万片晶圆,到2027年进一步攀升至约17万片。台积电已规划约7座先进封装工厂,全面部署CoWoS、WMCM及SoIC三大核心技术,绝大部分产能优先服务AI算力需求。

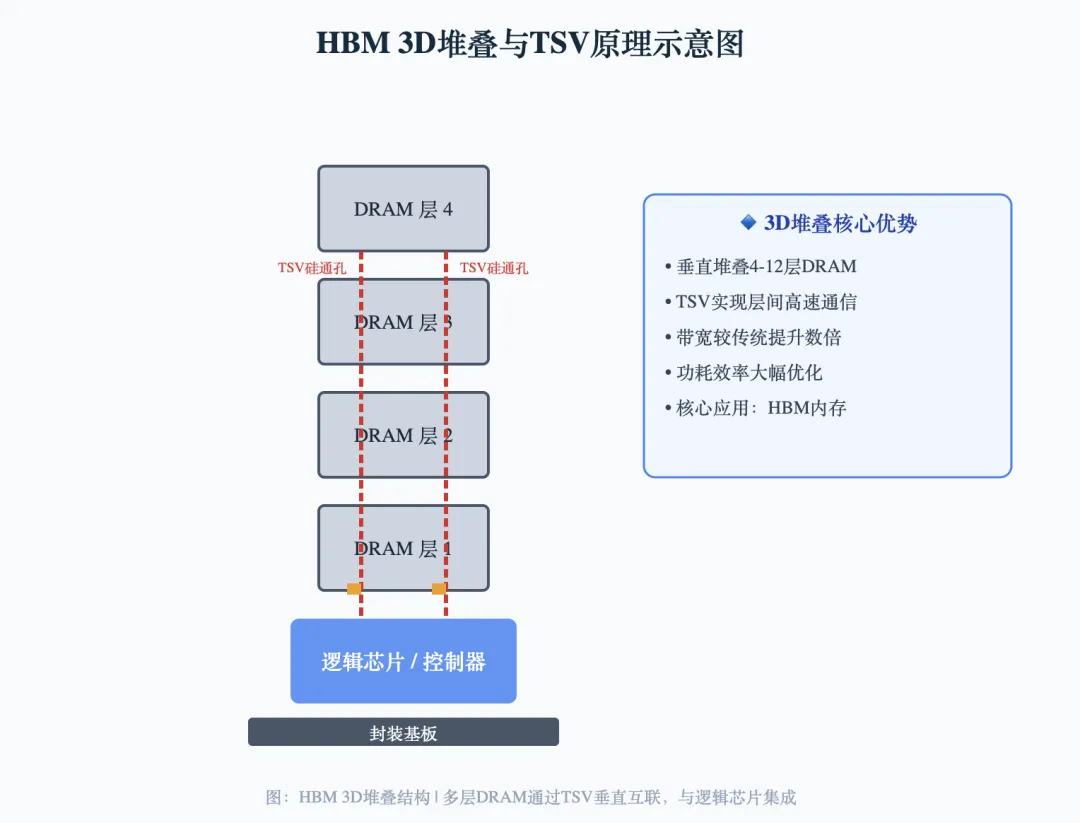

🔥 HBM 3D堆叠——存储界的”千层饼”

HBM做的就是垂直堆叠——把4层、8层甚至12层DRAM芯片像叠千层饼一样垒起来,中间通过TSV(硅通孔)打洞穿通,让数据在垂直方向高速穿梭。

SK海力士计划2026年启动HBM4大规模量产。这背后有一个关键约束:CoWoS封装中,12层及以上HBM集成需求持续增长,而三星、SK海力士、美光已把新增产能的约70%倾斜给HBM,直接导致普通存储器供给收缩、价格上行。

🔥 Chiplet——”芯片积木”

Chiplet把一块大芯片拆成几块”小砖头”,每块砖用最适合的工艺去制造,然后再拼到一起。AMD的EPYC处理器就是典型的例子。它天然依赖先进封装来”拼图”——UCIe标准接口让来自不同厂商的”芯片积木”可以自由组合,进一步扩大了封装的市场空间。

三、全球竞争格局:台积电领跑,日月光三星安靠贴身追赶

日月光2026年在全球同步动工六座新厂,原定约70亿美元的年度资本支出计划仍有上调空间。斥资约148.5亿新台币收购面板企业群创南科Fab 5厂区,快速补齐先进封装产能缺口。同时官宣CPO技术将在今年正式启动量产,切入AI高速传输先机。

三星电子已调整下一代FOPLP封装技术基板尺寸,并将向越南投资约40亿美元建设半导体封测厂,首期投入近半数,瞄准全球数据中心及AI设备需求。

安靠资本开支计划也全力投向先进封装产能扩张,越南工厂被定位为”未来十年增长引擎“,主攻SiP和HBM集成,目标覆盖高性能计算(HPC)与AI市场。

台积电、三星、英特尔在”后道环节”持续加码,反映出全球半导体产业的价值链正在从前段晶圆制造向后段封装迁移。

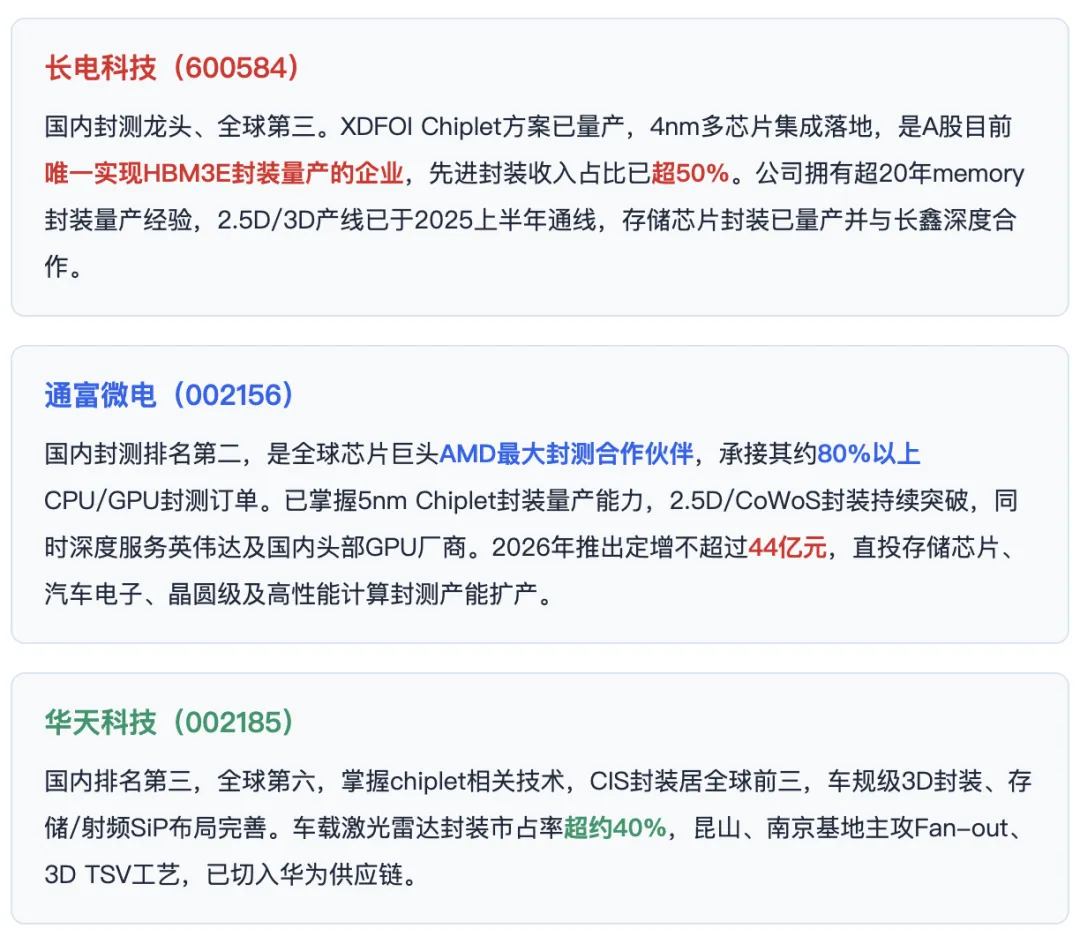

四、国内先进封装企业:长电通富华天三足鼎立

国产先进封装近年来取得了突破性进展,已形成以长电科技、通富微电、华天科技三巨头为核心的产业格局。

其他值得关注的标的:

五、未来技术格局:三大演进方向

方向一:光子互连——CPO加速量产(这个非常重要,建议大家重点关注)

当前大模型训练面临两大瓶颈:”内存墙“(HBM容量不够)和”互联墙“(芯片间数据传输太慢)。

CPO的核心思想很激进——把光收发器直接塞进芯片封装内部,让电信号在最短路径就变成光信号,不必再跑到电路板上兜一大圈。相比传统可插拔光模块,功耗效率提升约2倍、传输延迟降低近90%。

📊 台积电旗下COUPE光子引擎将于2026年达成关键里程碑,采用基板原生CPO解决方案,正式迈入量产,已应用于约200Gbps微环调变器。日月光半导体同样确认,CPO技术将在2026年正式启动量产。

方向二:材料革命——玻璃基板+SiC成为关键突破口(玻璃基板方向也很重要,可以重点关注)

AI芯片从千亿晶体管向万亿晶体管迈进,传统有机基板热膨胀不匹配、翘曲、信号损失问题越来越突出。

玻璃基板凭借接近零的热膨胀系数、优异平整度和低传输损耗,已替代传统硅中介层成为下一代AI训练的”标准板材”。三星对此大规模投入研发。TGV玻璃基板市场将从2026年约9.3亿美元逐步成长至2034年约15.5亿美元。FOPLP与玻璃基板有望在2026至2028年正式进入小批量产阶段。

台积电法说会同步释放重要创新信号——碳化硅(SiC)材料在散热、应力和大尺寸上的优势,已验证能解决超大尺寸封装的翘曲与热管理难题。SiC有望以热扩散层、热承载层和结构支撑层渐进导入CoWoS封装流程。

方向三:设备国产替代——从0到1突破

先进封装的国产化水平正在从”关键技术突破”向”系统性扩产”迈进。迈为股份在国内率先完成激光开槽、激光改质切割、刀轮切割、研磨抛光一体及键合设备等核心装备的国产化替代,多款设备已批量交付长电科技、华天科技、通富微电等国内头部封装企业并稳定量产。

六、博主的一张表总结

写在最后

很多人对”芯片产业”的理解还停留在”光刻机多先进、纳米节点多小”这些层面。但台积电法说会释放的一个信号极其明确——先进封装已从”配角”晋级为”AI算力主引擎”,芯片的成败不再仅仅取决于前段制程,而是更取决于晶圆制造与先进封装的系统协同能力。

过去,先进封装被人当作一个后道环节”打包发走”;如今,它直接决定大模型算力的上限。

🔒 台积电把CoWoS的尺寸从5.5倍放大到约14倍甚至约40倍🔒 玻璃基板从样品走向小批量产🔒 CPO真正落地取代可插拔光模块

先进封装这个赛道已经不是”卖铲子的逻辑”,而是整个人工智能算力竞赛的基石。谁在封装上领先,谁就定义了AI时代的硬件标准。

对于国内企业而言,先进制程受限,让先进封装成为国产算力产业链中自主可控最急迫且价值增量最可观的一环。正处在”技术突破”与”份额提升”的战略共振点上。整个逻辑正在由”扩产”切换到”技术差异化+分蛋糕“,谁能率先实现大尺寸+高良率+先进封装平台商业化,谁就站在了下一轮行情的起点上。

当台积电把CoWoS做到约40倍光罩尺寸,当CPO取代可插拔光模块,当玻璃基板成为下一代AI训练的”标准板材”——先进封装已经不再是后道工序,而是整个AI算力竞赛的基石。所以,谁在封装上领先,谁就定义了AI时代的硬件标准。

⚠️ 风险提示:本文仅为行业分析与知识分享,不构成任何投资建议。

🔔 觉得有用,欢迎点赞收藏转发

关注博主,持续追踪 AI / 芯片 / 机器人 / 新能源赛道等高端制造赛道

夜雨聆风

夜雨聆风