玻璃基板正在突破AI芯片封装瓶颈

玻璃凭借更优异的热性能与机械性能,正成为先进封装的下一代核心材料。

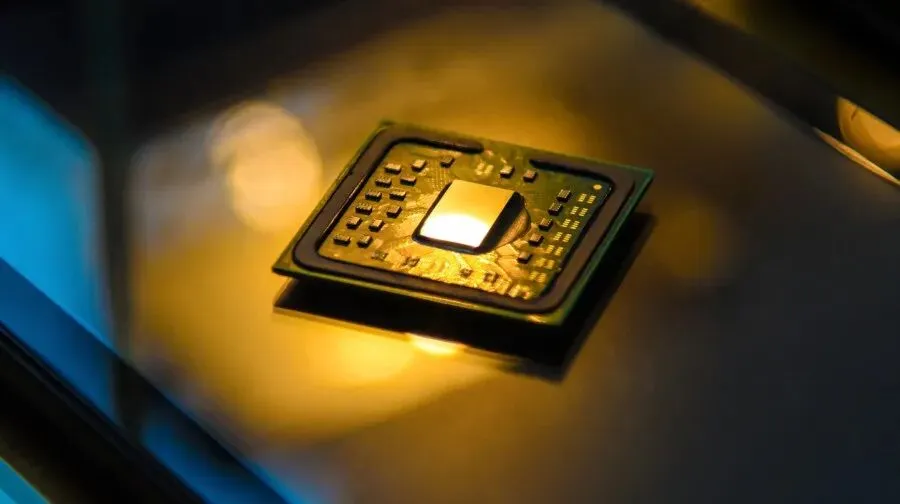

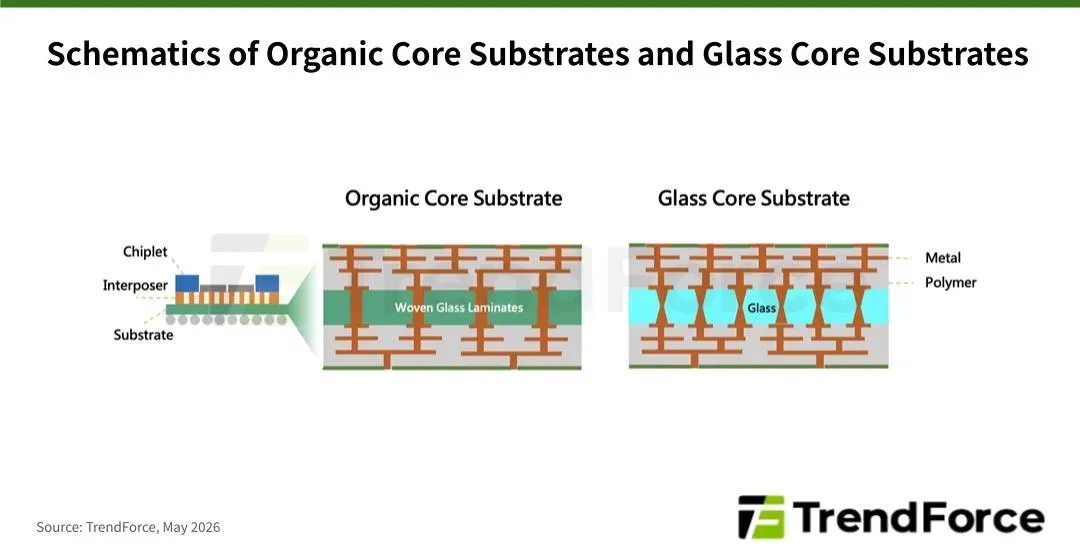

业界讨论AI基础设施建设,往往只聚焦芯片与算力层面。但表象之下,一系列供应链瓶颈正悄然决定着AI部署的进度与成本。本文将聚焦玻璃基板。随着AI芯片复杂度不断提升,封装尺寸持续扩大,传统有机基板已触及性能极限。封装组装的高温环境下,翘曲问题会降低良率;且随着封装尺寸越大,翘曲管控难度也愈发加剧。在此背景下,玻璃凭借更优异的热性能与机械性能,正成为先进封装的下一代核心材料。玻璃基方案主要分为两类:一类以玻璃替代基板芯层,称为玻璃芯基板;另一类以玻璃替代硅中介层,称为玻璃中介层。

英特尔在玻璃基板技术上布局积极。早在2023年,英特尔就将玻璃基板纳入先进封装路线图。2026年1月,在日本NEPCON展会上,英特尔首次展出EMIB封装+玻璃芯基板整合样品,实现无微裂纹(NoSeWaRe),标志着向商业化落地迈出关键一步。与此同时,台积电、三星、Rapidus预计陆续推出玻璃中介层方案;SK旗下Absolics则瞄准2026年实现玻璃基板量产。

本文将解析玻璃基板的技术优势、量产难题,以及当前供应链厂商格局的演变态势。

芯片尺寸越大,封装难题越突出

芯片尺寸越大,封装难题越突出

随着AI算力需求激增,单颗AI芯片的封装尺寸持续放大。尽管阿斯麦的EUV(0.33NA)光刻,目前将最大掩模版尺寸限制在26×33毫米(约830平方毫米),但台积电采用掩模拼接技术,拼接多块掩模图形以做大芯片尺寸。

英伟达Blackwell架构GPU单封装尺寸约为掩模版尺寸的3.3倍,面积达约2739平方毫米;下一代Rubin GPU预计扩至掩模版4倍尺寸,约3320平方毫米;Rubin Ultra GPU更将达到掩模版9倍尺寸,约7470平方毫米。除英伟达外,谷歌TPU v9x(HumuFish)也将采用掩模版9.5倍的超大封装尺寸。

从台积电CoWoS掩模版尺寸路线图来看:目前5.5倍掩模版尺寸已量产,9倍目标2027年落地,14倍规划2028年,14倍以上版本预计2029年推出。英特尔则计划2028年推出12倍掩模版尺寸的EMIB方案,匹配超大芯片封装需求。

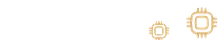

但封装尺寸持续放大,带来两大核心挑战:第一,方形大芯片难以在圆形晶圆上高效排布,晶圆边缘面积浪费严重。由此催生面板级封装(PLP)思路:以方形面板替代圆形晶圆,面积利用率可提升至75%以上。圆晶圆与方面板面积利用率对比:300毫米圆晶圆随芯片尺寸增大,利用率从约60%降至50%左右;而方形面板可稳定维持约75%利用率。

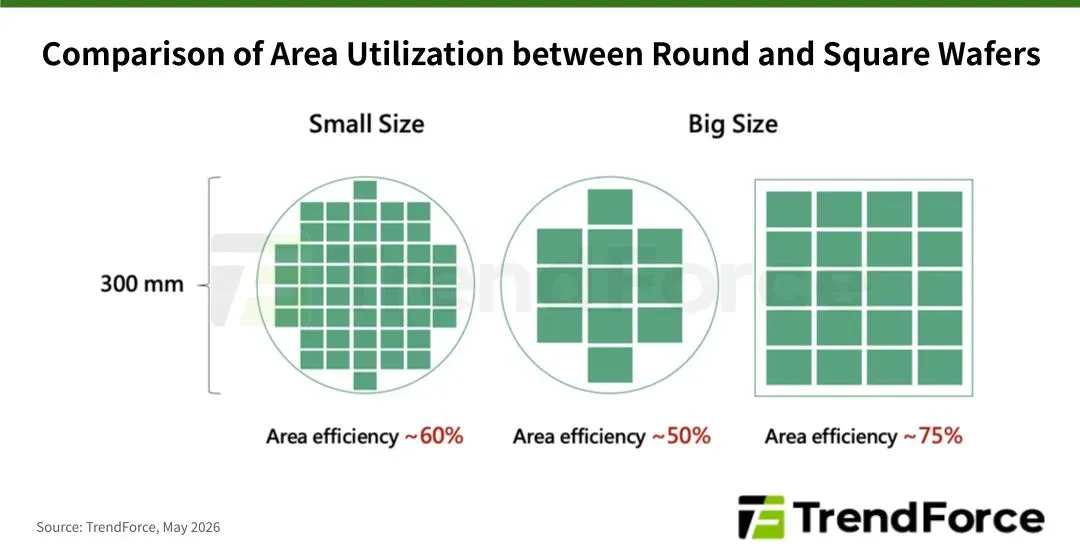

第二,若超大封装继续采用有机芯基板(主流为ABF材料,由树脂、玻纤布、铜箔压合制成),回流焊加热过程中翘曲会愈发严重,进而拉低整体集成良率。

因此,玻璃表面平整度高,且热膨胀系数(CTE)与硅材料接近,成为替代有机材料、用作中介层与封装基板的理想选择。

玻璃基板为何优于有机基板?

玻璃基板为何优于有机基板?

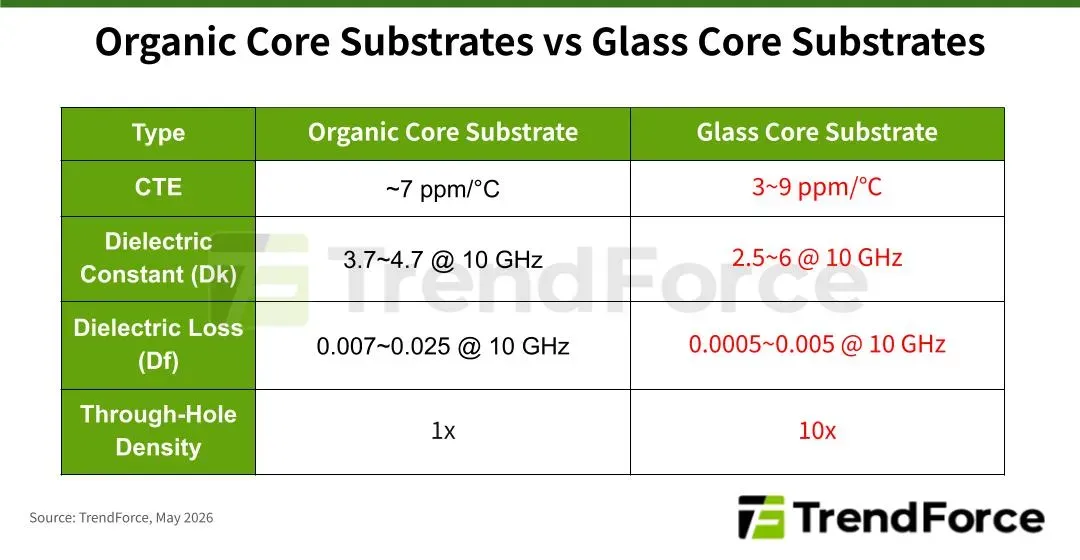

玻璃基板为何优于有机基板,其核心原因在于热性能、电气性能、物理结构全面占优。热膨胀系数与硅匹配,有机芯基板热膨胀系数约7ppm/℃,与硅的2.6ppm/℃差距大,极易引发翘曲;玻璃热膨胀系数可控制在3–9ppm/℃,可与硅精准匹配,即便超大封装也能维持稳定良率。

其次介电性能优异,玻璃是绝佳绝缘材料,10GHz频率下,介电常数Dk低至2.5–6,介电损耗Df低至0.0005–0.005,可保障高速传输下的信号完整性。

第三,表面极致平整:玻璃表面平整度与光洁度极高,可实现更精细的线路线宽/线距(L/S),可达2微米以下。

各家厂商布局进度与时间规划

各家厂商布局进度与时间规划

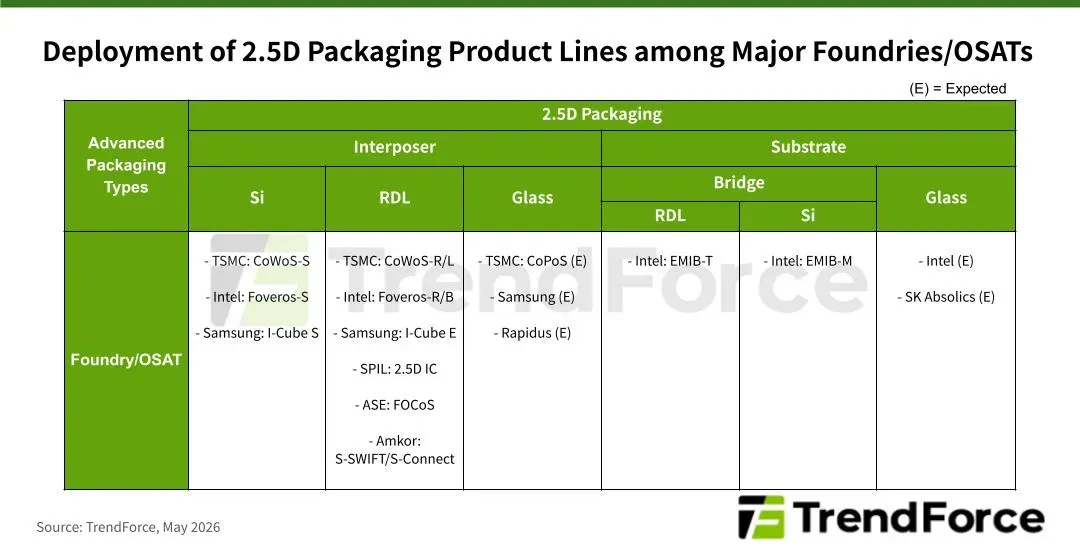

凭借适配先进封装的优异物性,全球主流晶圆厂与封测厂纷纷新增玻璃基板、玻璃中介层产线。

台积电2025年推出310×310毫米CoPoS(面板基板芯片)产线规划;计划2026年在景硕设立首条试产线,2027年小批量试产,2028–2029年实现量产。台积电在CoPoS中把玻璃用作中介层,厚度要求更薄(约400微米,仅为普通基板一半)、热膨胀系数匹配标准更严苛,技术难度高于玻璃基板方案。

三星2024年CES官宣研发玻璃中介层技术;2025年通过子公司SEMCO建成首条玻璃芯基板试产线,规划2027年量产。Rapidus在2025年日本半导体展,展出目前最大尺寸600×600毫米玻璃中介层样品,目标2028年量产。

韩国SK集团与应用材料合资企业Absolics,早在2022年就投入约3000亿韩元,在美国佐治亚州卡温顿建成首座玻璃基板工厂。公司目标研发可直接内嵌有源/无源器件的玻璃基板,省去中介层环节,缩减封装面积、厚度与功耗;基板尺寸500×500毫米,规划2026年量产。

英特尔是玻璃基板研发最为激进的厂商。2023年9月,英特尔官宣先进封装导入玻璃基板,量产窗口锁定2026–2030年。2026年1月22日日本NEPCON展,英特尔展出首款EMIB+玻璃芯基板整合样品:封装尺寸78×77毫米(约1716平方毫米),支持2倍掩模版尺寸,采用10-2-10堆叠结构(10层重布线层+2层玻璃芯+10层重布线层,共22层),总厚度800微米,凸点间距45微米。同时测试实现无微裂纹(NoSeWaRe),为量产扫清关键障碍。

量产最大拦路虎:SeWaRe微裂纹

量产最大拦路虎:SeWaRe微裂纹

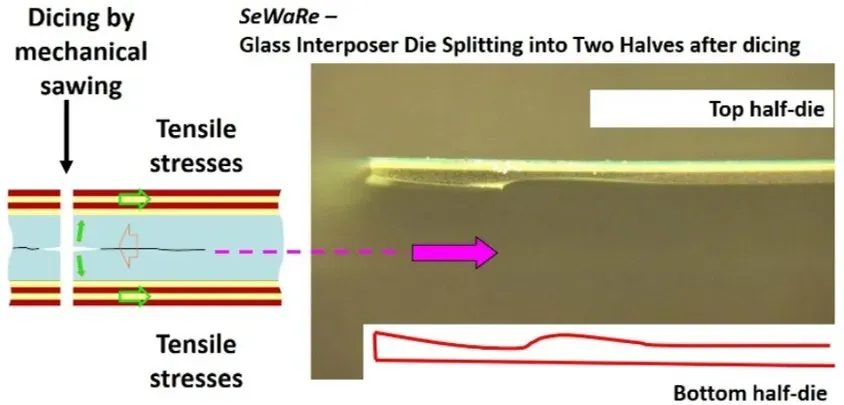

玻璃基板量产最大难题是SeWaRe,指加工(尤其打孔、切割)过程中产生的微裂纹。玻璃材质脆性大,一旦产生微裂纹,会形成应力集中点,后续测试与封装工序中极易引发基板断裂。

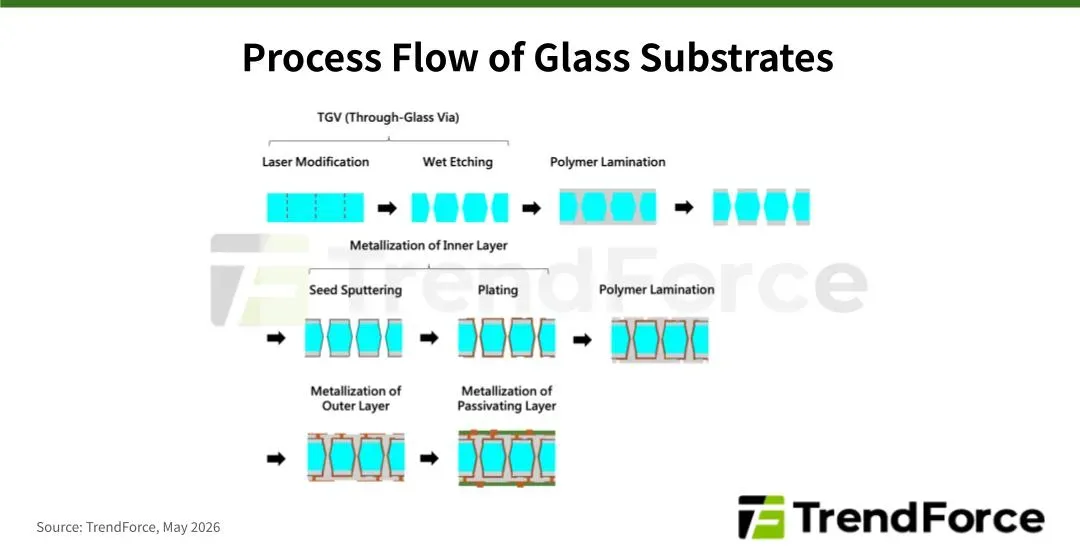

为降低SeWaRe发生概率,当前主流玻璃基板制造工艺流程如下:

-

玻璃通孔(TGV):先对玻璃内部做激光改性,再对改性区选择性湿法刻蚀形成通孔;通孔设计为X型锥面侧壁,利于分散应力。

-

聚合物覆膜:在玻璃表面压合树脂缓冲层。铜热膨胀系数偏高(约17ppm/℃),树脂层隔离铜与玻璃,避免热胀冷缩产生开裂。

-

种子层溅射:在表面溅射金属种子层。

-

电镀沉积:在种子层表面电镀均匀金属层,减少铜材用量,规避热胀冷缩开裂风险。

按所需层数重复第2–4步,即可完成多层堆叠结构。

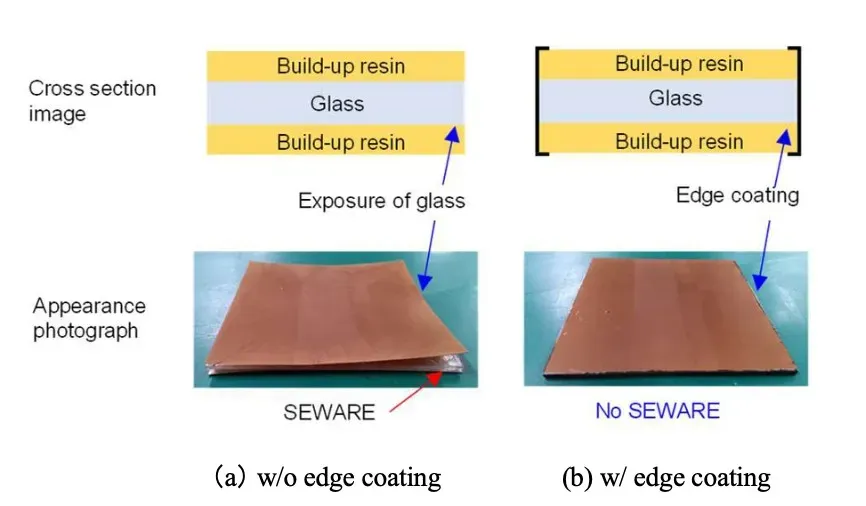

多层制程中,树脂层仍会随热胀冷缩发生偏移,对玻璃产生拉应力。新光电气工业研究表明:对玻璃基板做边缘树脂涂覆可降低边缘应力。例如300微米厚树脂层会对玻璃产生约95兆帕应力,边缘涂覆后可降至约49兆帕。

为攻克SeWaRe难题,玻璃基板全产业链厂商纷纷推出对应方案:德国LPKF推出用于玻璃通孔的LIDE激光改性刻蚀工艺;日本DISCO推出SD、LEAF激光切割技术;Onto Innovation发布Firefly G3用于硅通孔/玻璃通孔检测的量测设备。

供应链格局现状

供应链格局现状

目前玻璃基板制造所需核心半导体设备、材料,高度集中于欧美日龙头企业,例如玻璃通孔设备:LPKF;低膨胀玻璃材料:肖特、康宁、AGC、NEG;刻蚀与电镀设备:泛林半导体;切割设备:DISCO;检测量测设备:Onto、科磊;临时键合/解键合设备:SUSS、EVG。

玻璃基板技术正多路线同步推进。

夜雨聆风

夜雨聆风