真正关心硬件的人应该设计自己的硬件设计软件 — 早上听Scala day 2025学习体会

早上听Scala day 2025,

以色列理工毕业的Ph.D讲开源项目:

DFiantHDL https://github.com/DFiantHDL/DFHDL

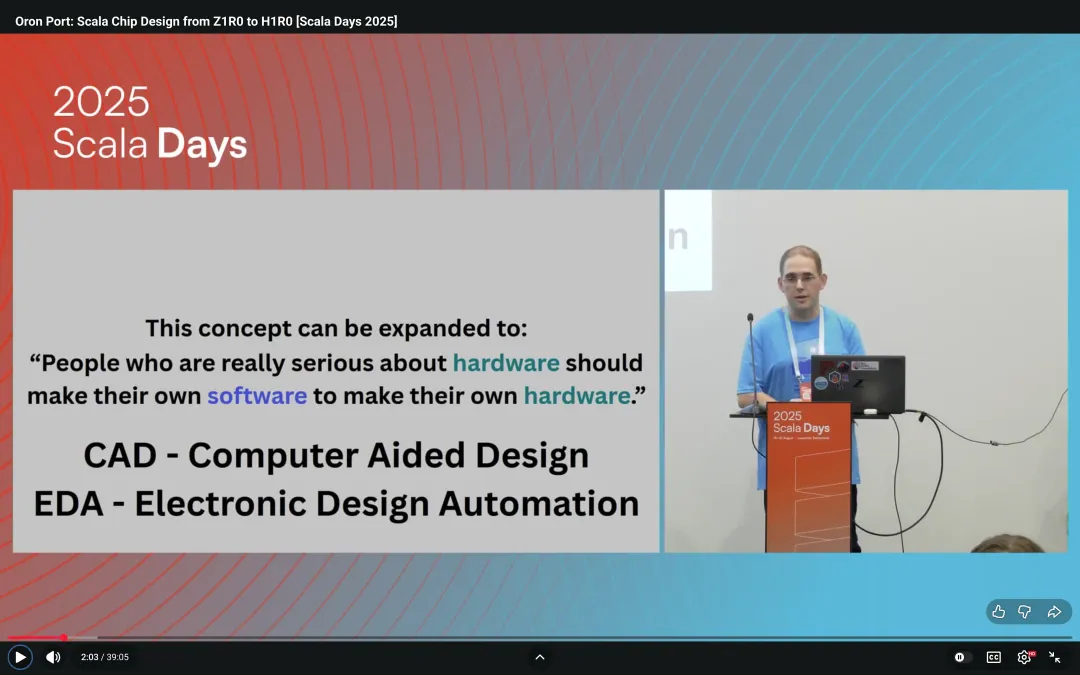

这场 Scala Days 2025 的分享用“披萨流水线”类比解释了同步数字电路和硬件设计的基本思路,指出传统 HDL 如 Verilog/VHDL 在类型安全、易用性和工具一致性上都有明显痛点,随后介绍了基于 Scala 3 的硬件描述库 DFHDL:它把事件级、寄存器传输级和数据流级三种抽象统一到同一语言里,借助 Scala 3 的类型系统、上下文机制和编译器插件,把板卡连接、时钟/资源配置、断言、编译期与运行期检查等繁琐细节自动化,让开发者更专注于描述“硬件要做什么”而不是“底层怎么接”,并通过现场 FPGA LED 跑马灯演示说明这种方式能显著降低硬件设计入门门槛、

我的学习体会:

这次报告报告人并未提及Claude,但是在DFHDL项目的根目录下,有一个名为

https://github.com/DFiantHDL/DFHDL/blob/main/.claude/commands/的目录,从顶层非常详细地指导Claude如何协同进行 Scala代码检查和归整。

我认为System Verilog/Verilog => Scala => Claude Code,是一层又一层的抽象。虽然抽象得厉害,但是仍然需要使用者对专业知识有坚实的把握,和对顶层逻辑的清晰规划。

https://www.youtube.com/watch?v=5VdlKguxUqA

为体现是真人在学科学文化知识,真人在写学习体会:插播一下北京北土城护城河风光

夜雨聆风

夜雨聆风